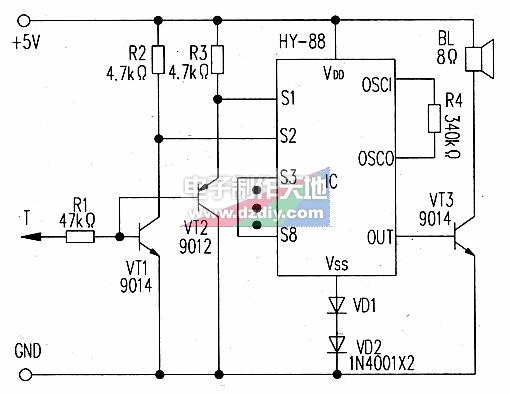

關(guān)鍵字:邏輯測試電路圖,HY88

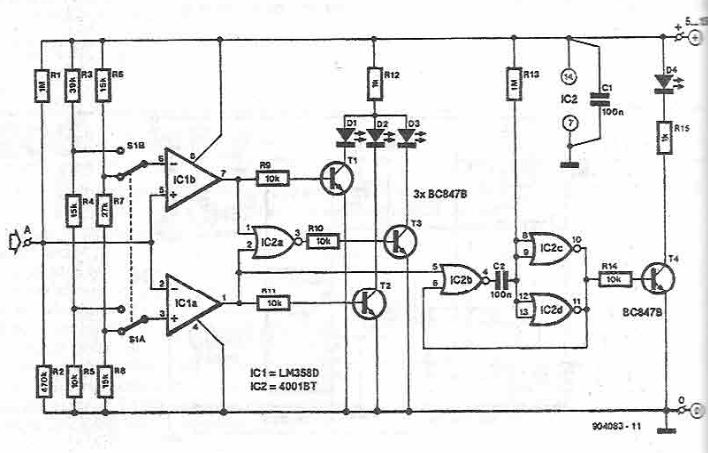

電路原理:電路中.HY-88是一片采用PCB(印刷線路板式軟封裝)封裝的8聲效音樂集成電路,它有s1~s8共8個觸發(fā)控制端,低電平觸發(fā)有效,對應著內(nèi)部ROM(只讀存儲器)預先存儲的8種動物叫聲,分別是蟲叫、蟋蟀、青蛙、布谷鳥、貓、狗、牛及馬蹄聲。調(diào)整振蕩電阻R4可改變叫聲音調(diào),音頻信號經(jīng)VT3放大后驅(qū)動揚聲器BL發(fā)聲。VD1、VD2是降壓二極,以使其Vdd,Vss間的工作電壓符合2.5V~4.5V范圍要求。該邏輯筆的檢測狀態(tài)為:(1)當探針T未接觸電路或檢測到“懸空”時,VT1和VT2均截止,Ic的觸發(fā)端s1、s2分別被R3、R2上拉為“1”,IC不工作,BL無聲;(2)當探針T檢測到“O”時,VT1截止,VT2導通,s2為“1”,s1被“0”觸發(fā),BL發(fā)出蟲鳴聲;(3)當探針T檢測到“1”時,VT1導通,VT2截止,S1為“1”,S2被“0”觸發(fā),BL發(fā)出蟋蟀叫聲;(4)當探針T檢測到“CP”脈沖時,、VT1、VT2輪流導通,s1、S2被交替觸發(fā),BL產(chǎn)生蟋蟀和蟲兩種嗚叫聲。

作者:沈左

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學習之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

發(fā)布評論請先 登錄

相關(guān)推薦

西門子推出Tessent In-System Test軟件

西門子數(shù)字化工業(yè)軟件日前推出 Tessent In-System Test 軟件,作為一款突破性的可測試性設(shè)計(DFT)解決方案,旨在增強下一代集成電路(IC)的系統(tǒng)內(nèi)測試能力。

時序邏輯電路的基本概念、組成、分類及設(shè)計方法

Logic Circuit)是一種在數(shù)字電路中,其輸出不僅取決于當前輸入,還取決于過去輸入歷史的電路。與組合邏輯電路(Combinational Logic Circuit)不同,組合邏輯

時序邏輯會產(chǎn)生鎖存器嗎

時序邏輯電路本身并不直接“產(chǎn)生”鎖存器,但鎖存器是時序邏輯電路中的重要組成部分。時序邏輯電路(Sequential Logic Circuits

opa857在test mode下,out端輸出電壓不隨TEST_IN的電壓變化怎么解決?

原理圖:

CTRL(增益控制引腳): logic 0–5kΩ

logic 1–20kΩ

OPA857有兩種模式:normal mode 和 test mode ,由TEST_

發(fā)表于 08-02 07:15

組合邏輯電路邏輯功能的測試方法

,對組合邏輯電路邏輯功能的測試是確保數(shù)字系統(tǒng)正確性的關(guān)鍵步驟。 二、測試目的 組合邏輯電路邏輯功

觸發(fā)器和時序邏輯電路詳解

電路(Sequential Logic Circuits)則是由觸發(fā)器、邏輯門以及可能的時鐘信號源組成的電路,它們能夠處理隨時間變化的輸入信號,并產(chǎn)生隨時間變化的輸出信號。下面將詳細探討觸發(fā)器和時序

模擬示波器能測試邏輯信號嗎

模擬示波器是一種用于測量和顯示電壓波形的電子測試儀器,它能夠測量電壓、頻率、周期、相位等參數(shù)。雖然模擬示波器主要用于測量模擬信號,但在某些情況下,它也可以用于測試邏輯信號。 模擬示波器測試

組合邏輯控制器的設(shè)計步驟是什么

組合邏輯控制器(Combinatorial Logic Controller)是一種數(shù)字電路,用于根據(jù)輸入信號生成輸出信號。它不包含存儲元件,因此輸出僅取決于當前的輸入信號。組合邏輯控制器廣泛應用

組合邏輯控制器的基本概念、實現(xiàn)原理及設(shè)計方法

組合邏輯控制器(Combinatorial Logic Controller)是一種在數(shù)字電路中實現(xiàn)邏輯功能的設(shè)備,它根據(jù)輸入信號的當前狀態(tài)來產(chǎn)生輸出信號,而不考慮輸入信號的歷史狀態(tài)。組合邏輯

車載T-Box邏輯功能測試方案

北匯信息基于對客戶需求規(guī)范、行業(yè)法規(guī)及自身測試經(jīng)驗Know-How,為客戶提供完整和專業(yè)的T-Box邏輯功能測試解決方案。支持在實驗室環(huán)境及實車環(huán)境下完成T-Box上層邏輯功能

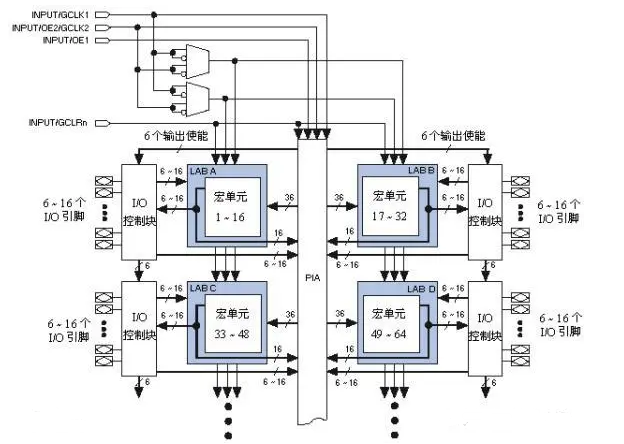

CPLD組成和邏輯塊作用介紹

在CPLD(Complex Programmable Logic Device,復雜可編程邏輯器件)中,邏輯塊是實現(xiàn)邏輯功能的核心模塊。它主要由可編程乘積項陣列(即與陣列)、乘積項分配

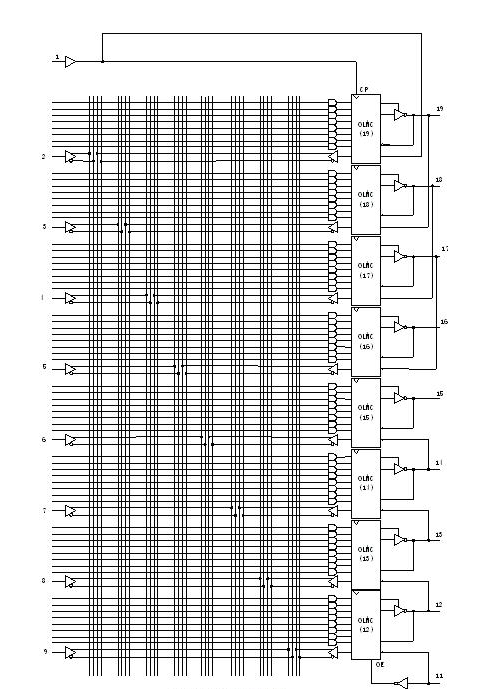

通用陣列邏輯(GAL)電路結(jié)構(gòu)設(shè)計分析

通用陣列邏輯(GAL)是一種可編程邏輯器件,由Lattice公司在PAL(可編程陣列邏輯)的基礎(chǔ)上設(shè)計出來。GAL采用可編程的輸出邏輯宏單元OLMC(Output

發(fā)表于 02-02 12:21

?1834次閱讀

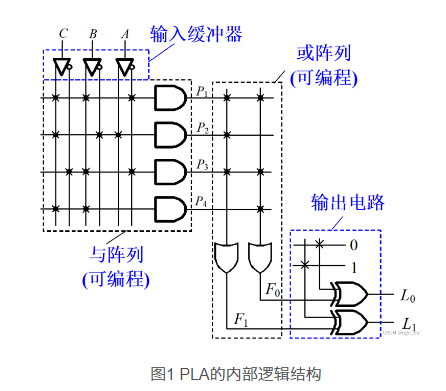

可編程邏輯陣列PLA內(nèi)部邏輯結(jié)構(gòu)示意

可編程邏輯陣列(Programmable Logic Array,PLA)和可編程陣列邏輯(Programmable Array Logic,PAL)都是數(shù)字

發(fā)表于 02-02 11:41

?2494次閱讀

音樂邏輯測試筆,Logic test circuits

音樂邏輯測試筆,Logic test circuits

評論