摘要

模擬帶寬的重要性高于其他一切在越來越多的應用中得到體現。隨著GSPS或RF ADC的出現,奈奎斯特域在短短幾年內增長了10倍,達到多GHz范圍。這幫助上述應用進一步拓寬了視野,但為了達到X波段(12 GHz頻率),仍然需要更多帶寬。在信號鏈中運用采樣保持放大器 (THA),可以從根本上擴展帶寬,使其遠遠超出ADC采樣帶寬,滿足苛刻高帶寬的應用的需求。本文將證明,針對RF市場開發的最新轉換器前增加一個THA,便可實現超過10 GHz帶寬。

簡介

GSPS轉換器是當下熱門,其優勢在于既能縮短RF信號鏈,又能在FPGA中創建更多資源結構以供使用,例如:減少前端的下變頻以及后級的數字下變頻器 (DDC)。但相當多的應用仍然需要高頻率的原始模擬帶寬 (BW),其遠遠超出了RF轉換器所能實現的水平。在此類應用中,特別是在國防與儀器儀表行業(無線基礎設施也一樣),仍然有將帶寬完全擴展到10 GHz或以上的需求,覆蓋范圍超出C波段,越來越多的應用需要覆蓋到X波段。隨著高速ADC技術的進步,人們對GHz區域內高速精確地分辨超高中頻 (IF) 的需求也在提高,基帶奈奎斯特域已超過1 GHz并迅速攀升。這一說法到本文發表的時候可能即已過時,因為這方面的發展非常迅猛。

這帶來了兩大挑戰:一個是轉換器設計本身,另一個是將信號耦合到轉換器的前端設計,例如放大器、巴倫和PCB設計。轉換器性能越出色,就對前端信號質量要求更高。越來越多的應用要求使用分辨率在8到14位的高速GSPS轉換器,然而前端的信號質量成為了瓶頸—系統的短板決定了整個項目的指標。

本文定義的寬帶是指使用大于數百MHz的信號帶寬,其頻率范圍為DC附近至5 GHz-10 GHz區域。本文將討論寬帶THA或有源采樣網絡的使用,目的是實現直至無窮大的帶寬(抱歉,現在還沒有玩具總動員表情符號可用),并著重介紹其背景理論,該理論支持擴展RF ADC的帶寬,而RF ADC單憑自身可能沒有此能力。最后,本文將說明一些考慮因素和優化技術,以幫助設計人員實現超寬帶應用切實可行的寬帶解決方案。

打好基礎

對于雷達、儀器儀表和通信應用,高GSPS轉換器應用得非常廣泛,因為它能提供更寬的頻譜以擴展系統頻率范圍。然而,更寬的頻譜對ADC本身的內部采樣保持器提出了更多挑戰,因為它通常未針對超寬帶操作進行優化,而且ADC一般帶寬有限,在這些更高模擬帶寬區域中其高頻線性度/SFDR會下降。

因此,在ADC前面使用單獨的THA來拓展模擬帶寬成為了一個理想的解決方案,如此便可在某一精確時刻對頻率非常高的模擬/RF輸入信號進行采樣。該過程通過一個低抖動采樣器實現信號采樣,并在更寬帶寬范圍內降低了ADC的動態線性度要求,因為采樣率RF模數轉換過程中保持不變。

這種方案帶來的好處顯而易見:模擬輸入帶寬從根本上得以擴展,高頻線性度顯著改善,并且與單獨的RF ADC性能相比,THA-ADC組件的高頻SNR得到改進。

THA特性及概述

ADI的THA系列產品可以在18 GHz帶寬范圍內提供精密信號采樣,在DC至超過10 GHz的輸入頻率范圍內具有9到10位線性度、1.05 mV噪聲和

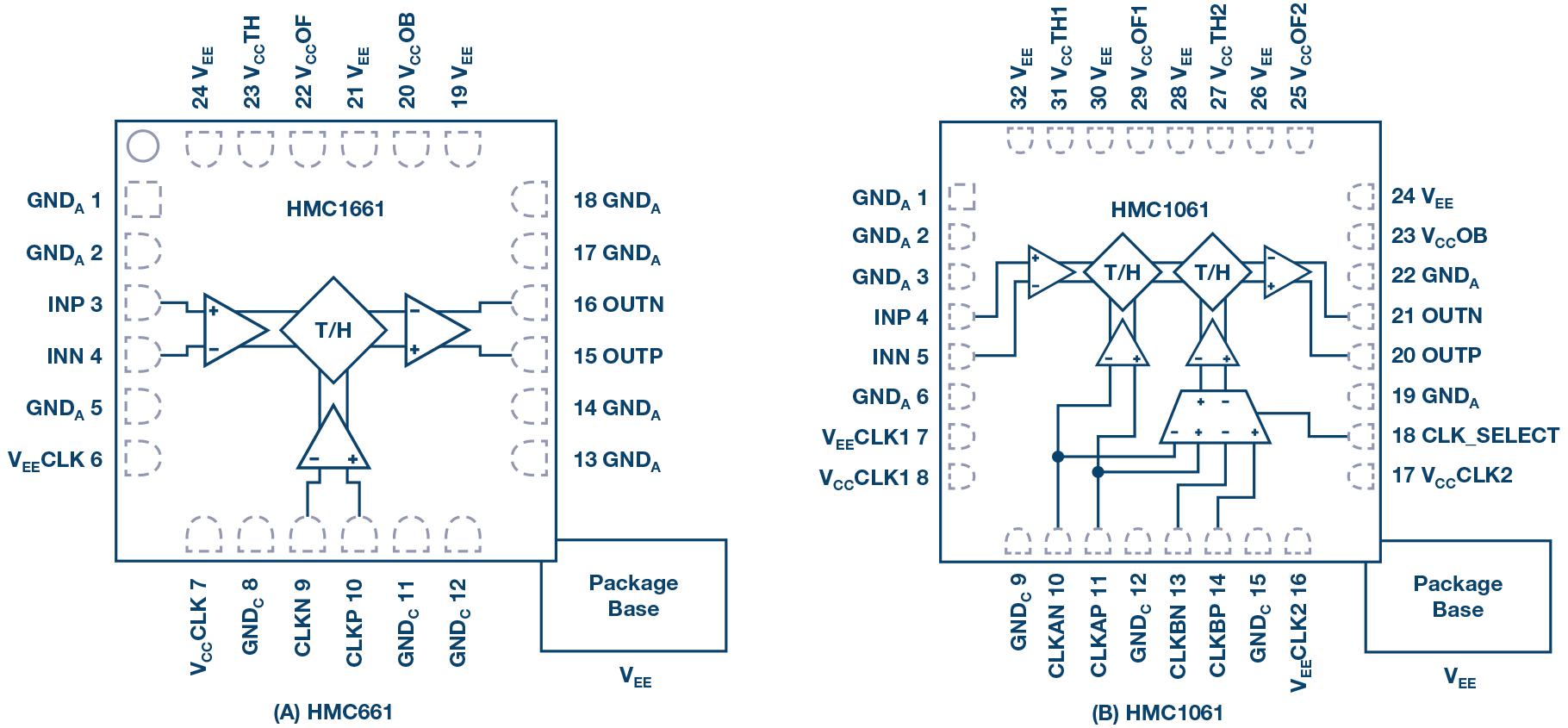

以單級THA HMC661為例,產生的輸出由兩段組成。在輸出波形(正差分時鐘電壓)的采樣模式間隔中,器件成為一個單位增益放大器,在輸入帶寬和輸出放大器帶寬的約束下,它將輸入信號復制到輸出級。在正時鐘到負時鐘躍遷時,器件以非常窄的采樣時間孔徑對輸入信號采樣,并且在負時鐘間隔內,將輸出保持在一個相對恒定的代表采樣時刻信號的值。配合ADC進行前端采樣時,常常優先使用單級器件(ADI 同時法布里了兩級THA 的型號HMC1061),原因是多數高速ADC已經在內部集成一個THA,其帶寬通常要小得多。因此,在ADC之前增加一個THA便構成一個復合雙級組件(或一個三級組件,如果使用的是雙級HMC1061),THA在轉換器前面。采用同等技術和設計時,單級器件的線性度和噪聲性能通常優于雙級器件,原因是單級器件的級數更少。所以,單級器件常常是配合高速ADC進行前端采樣的最佳選擇。

延遲映射THA和ADC

開發采樣保持器和ADC信號鏈的最困難任務之一,是在THA捕獲采樣事件的時刻與應將其移到ADC上以對該事件重新采樣的時刻之 間設置適當的時序延遲。設置兩個高效采樣系統之間的理想時間差的過程被稱為延遲映射。

在電路板上完成該過程可能冗長乏味,因為紙面分析可能不會考慮PCB板上時鐘走線傳播間隔造成的相應延遲,內部器件組延遲,ADC孔徑延遲,以及將時鐘分為兩個不同段所涉及到的相關電路(一條時鐘走線用于THA,另一條時鐘走線用于ADC)。設置THA和ADC之間延遲的一種方法是使用可變延遲線。這些器件可以是有源或無源的,目的是正確對準THA采樣過程的時間并將其交給ADC進行采樣。這保證了ADC對THA輸出波形的穩定保持模式部分進行采樣,從而準確表示輸入信號。

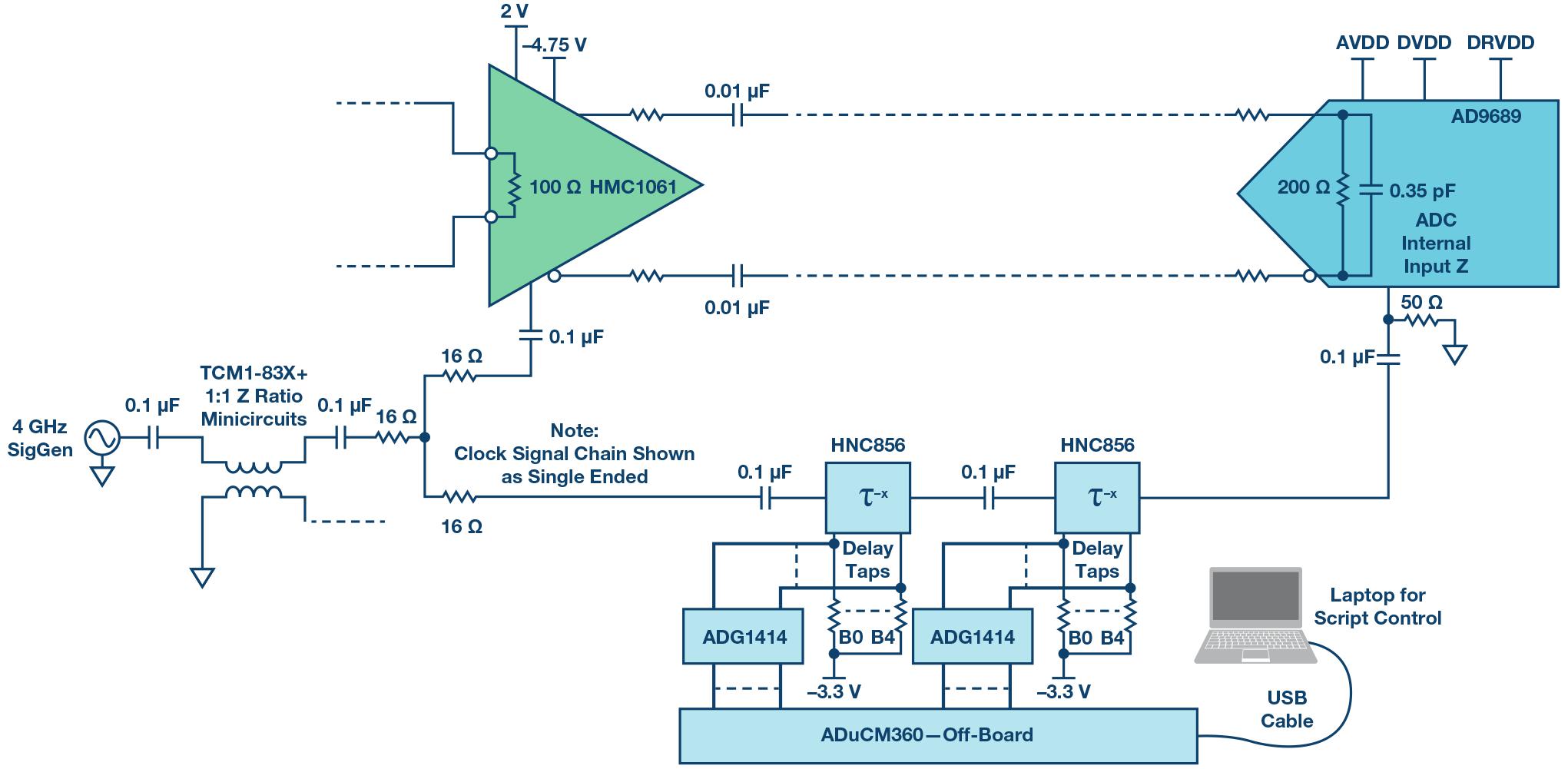

如圖2所示, HMC856 可用來啟動該延遲。它是一款5位QFN封裝,90 ps的固有延遲,步進為3 ps或25ps ,32位的高速延時器。它的缺點是要設定/遍歷每個延遲設置。要使能新的延遲設置,HMC856上的每個位/引腳都需要拉至負電壓。因此,通過焊接下拉電阻在32種組合中找到最佳延遲設置會是一項繁瑣的任務,為了解決這個問題,ADI使用串行控制的SPST開關和板外微處理器來幫助更快完成延遲設置過程。

為了獲得最佳延遲設置,將一個信號施加于THA和ADC組合,該信號應在ADC帶寬范圍之外。本例中,我們選擇一個約10 GHz的信號,并施加-6 dBFS的電平(在FFT顯示屏上捕獲)。延遲設置現在以二 進制步進方式掃描,信號的電平和頻率保持恒定。在掃描過程中顯示并捕獲FFT,收集每個延遲設置對應的基波功率和無雜散動態范圍 (SFDR) 數值。

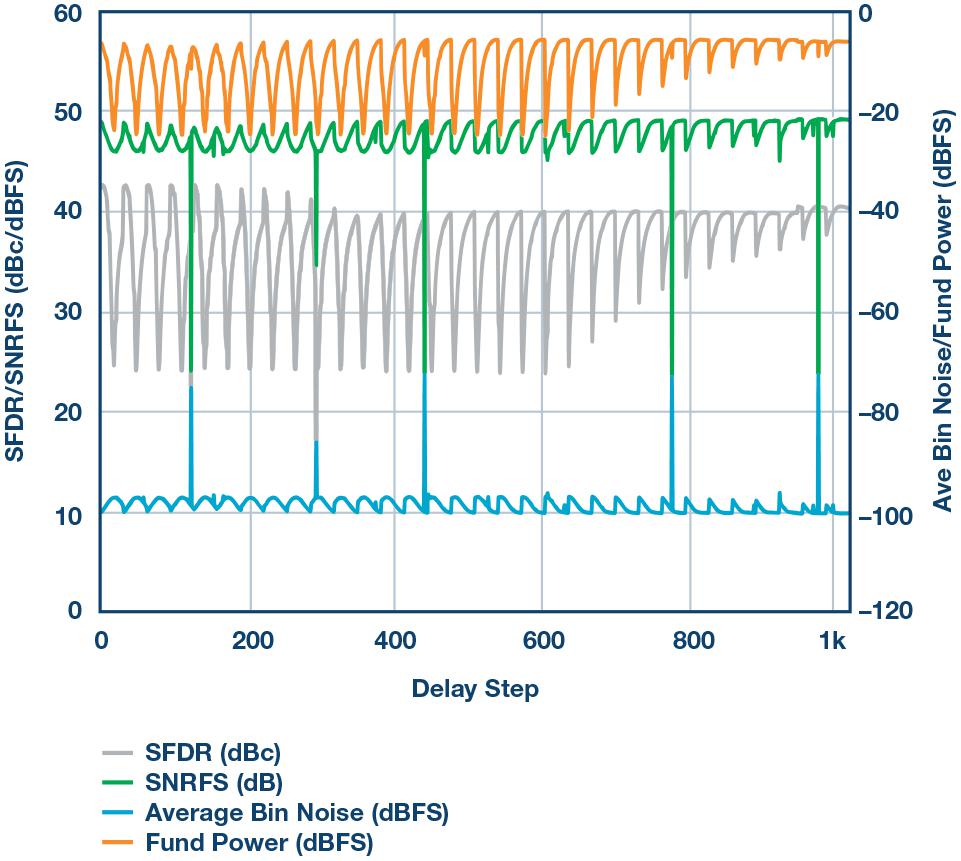

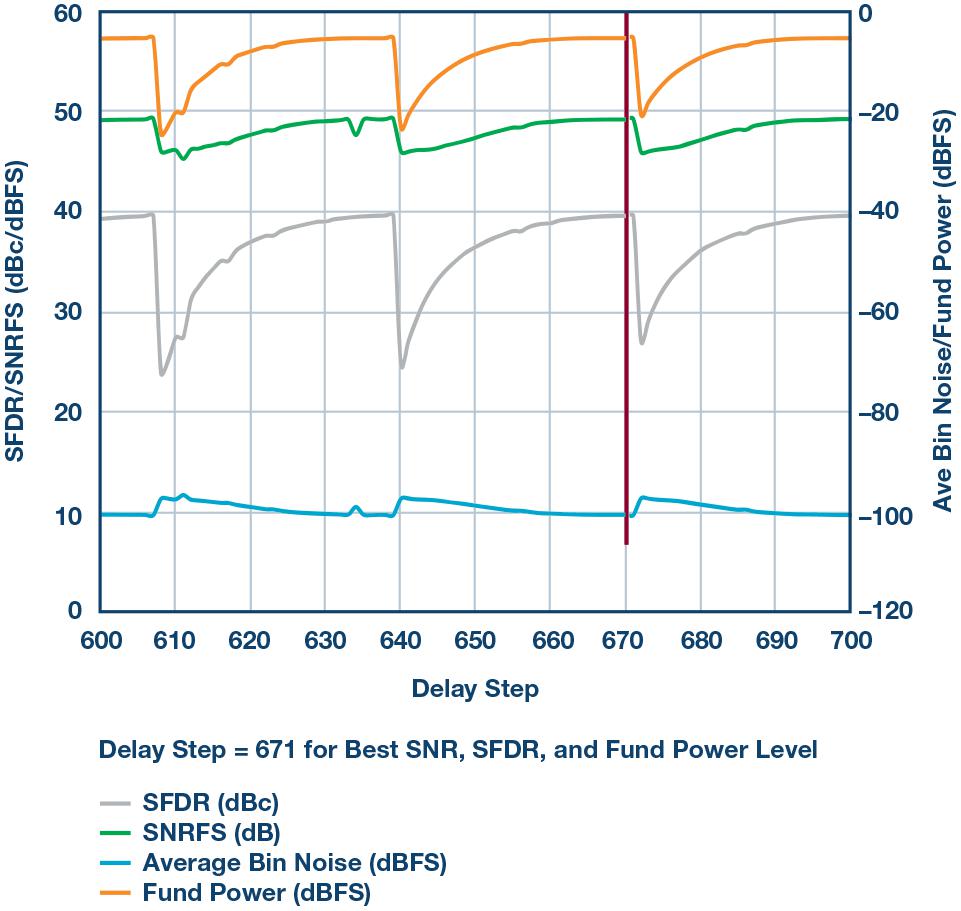

結果如圖3a所示,基波功率、SFDR和SNR將隨所應用的每個設置而變化。如圖所示,當把采樣位置放在更好的地方(THA將樣本送至ADC的過程之中)時,基波功率將處于最高水平,而SFDR應處于最佳性能(即最低)。圖3b為延遲映射掃描的放大視圖,延遲設定點為671,即延遲應該保持固定于此窗口/位置。請記住,延遲映射程序僅對系統的相關采樣頻率有效,如果設計需要不同的采樣時鐘,則需要重新掃描。本例中,采樣頻率為4 GHz,這是該信號鏈中使用的THA器件的最高采樣頻率。

針對大量原始模擬帶寬的前端設計

首先,如果應用的關鍵目標是處理10 GHz的帶寬,我們顯然應考慮RF方式。請注意,ADC仍然是電壓型器件,不會考慮功率。這種情況下,"匹配"這個詞應該謹慎使用。我們發現,讓一個轉換器前端在每個頻率都與100 MSPS轉換器匹配幾乎是不可能的;高頻率帶寬的RF ADC不會有太大的不同,但挑戰依舊。術語"匹配"應表示在前端設計中能產生最佳結果的優化。這是一個無所不包的術語,其中,輸入阻抗、交流性能 (SNR/SFDR)、信號驅動強度或輸入驅動、帶寬以及通帶平坦度,這些指標都能產生該特定應用的最佳結果。

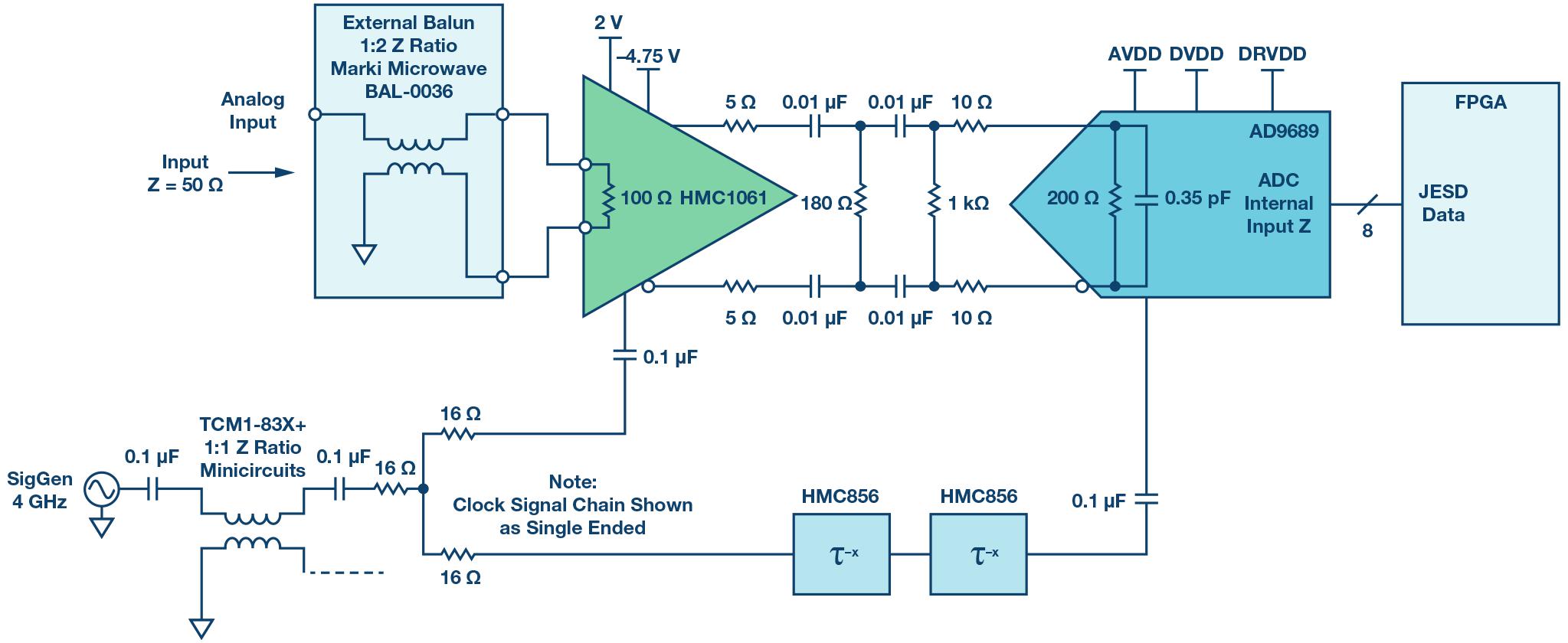

最終,這些參數共同定義了系統應用的匹配性能。開始寬帶前端設計時,布局可能是關鍵,同時應當最大限度地減少器件數量,以降低兩個相鄰IC之間的損耗。為了達到最佳性能,這兩方面均非常重要。將模擬輸入網絡連接在一起時務必小心。走線長度以及匹配是最重要的,還應盡量減少過孔數量,如圖4所示。

信號通過差分模式連接到THA輸入(我們同時是也提供單端射頻信號輸入的參考設計鏈路),形成單一前端網絡。為了最大限度地減少過孔數量和總長度,我們在這里特別小心,讓過孔不經過這兩條模擬輸入路徑,并且幫助抵消走線連接中的任何線腳。

最終的設計相當簡單,只需要注意幾點,如圖5所示。所使用的0.01 F電容是寬帶類型,有助于在較寬頻率范圍內保持阻抗平坦。典型的成品型0.1 F電容無法提供平坦的阻抗響應,通常會在通帶平坦度響應中引起較多紋波。THA輸出端和ADC輸入端的5和10串聯電阻,有助于減少THA輸出的峰化,并最大限度地降低ADC自身內部采樣電容網絡的殘余電荷注入造成的失真。然而,這些值需要謹慎地選擇,否則會增加信號衰減并迫使THA提高驅動強度,或者設計可能無法利用ADC的全部量程。

最后討論差分分流端接。當將兩個或更多轉換器連接在一起時,這點至關重要。通常,輕型負載(例如輸入端有1 k負載)有助于保持線性并牽制混響頻率。分流器的120 分流負載也有此作用,但會產生更多實際負載,本例中為50 ,這正是THA希望看到并進行優化的負載。

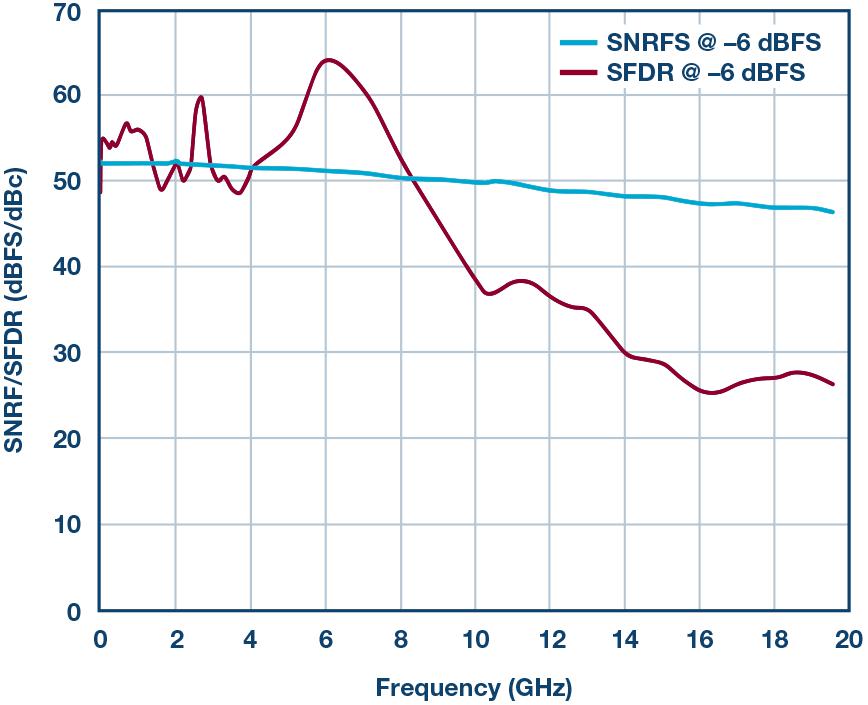

現在看結果!檢查圖6中的信噪比或SNR,可以看出在15 GHz范圍上可以實現8位的ENOB(有效位數)。這是相當不錯的,想想對于相同性能的13 GHz示波器,您可能支付了12萬美元。當頻率向L、S、C和X波段移動時,集成帶寬(即噪聲)和抖動限制開始變得顯著,因此我們看到性能出現滾降。

還應注意,為了保持THA和ADC之間的電平恒定,ADC的滿量程輸入通過SPI寄存器內部更改為1.0 V p-p。這有助于將THA保持在線性區域內,因為其最大輸出為1.0 V p-p差分。

同時顯示了線性度結果或SFRD。這里,到8 GHz為止的線性度超過50 dBc,到10 GHz為止的線性度超過40 dBc。為在如此寬的頻率范圍上達到最佳線性度,此處的設計利用 AD9689模擬輸入緩沖電流設置特性進行了優化(通過SPI控制寄存器)。

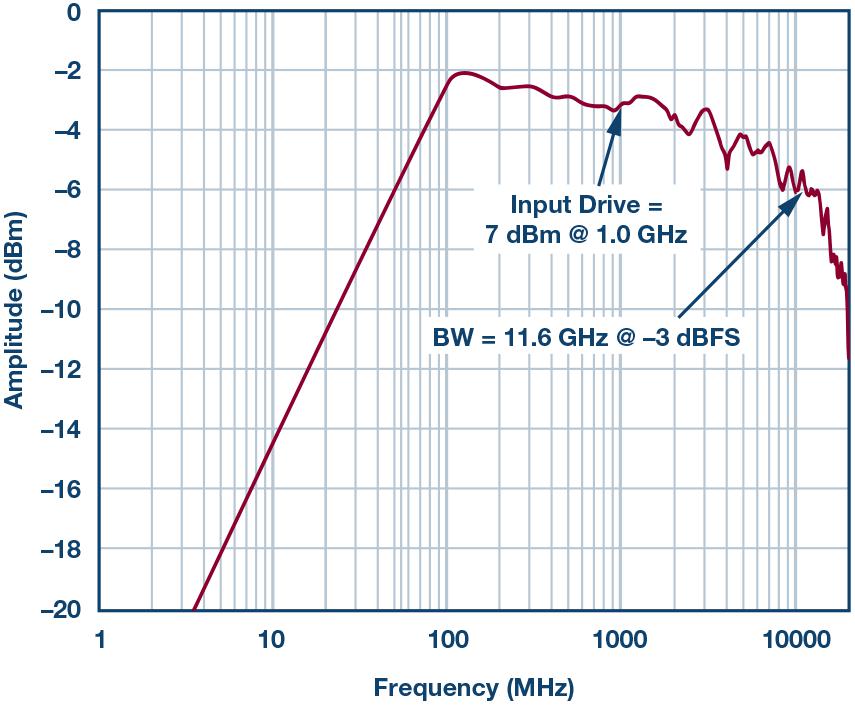

圖7顯示了通帶平坦度,證明在RF ADC之前增加一個THA可以實現 10 GHz的帶寬,從而充分擴展AD9689的模擬帶寬。

結語

對于那些需要在多GHz模擬帶寬上實現最佳性能的應用,THA幾乎是必不可少的,至少目前是如此!RF ADC正在迅速趕上。很容易明白,在對較寬帶寬進行采樣以覆蓋多個目標頻帶時,GSPS轉換器在理論上具有易用性優勢,可以消除前端RF帶上的一個或多個向下混頻級。但是,實現更高范圍的帶寬可能會帶來設計挑戰和維護問題。

在系統中使用THA時,應確保采樣點的位置在THA和ADC之間進行了優化。使用本文所述的延遲映射程序將產生總體上最佳的性能結果。了解程序是乏味的,但是非常重要。最后應記住,匹配前端實際上意味在應用的給定一組性能需求下實現最佳性能。在X波段頻率進行采樣時,樂高式方法(簡單地將50 阻抗模塊連接在一起)可能不是最好的方法。

作者

Rob Reeder是ADI公司高速轉換器和RF應用部(美國北卡羅來納州格林斯博羅)的高級系統應用工程師。他發表了大量有關各種應用的轉換器接口、轉換器測試和模擬信號鏈設計的文章。Rob曾在航空航天和防務部擔任應用工程師5年之久,專注于雷達、EW和儀器儀表等各種應用領域。他曾在高速轉換器產品線上任職9年。在此之前,Rob還從事過測試開發和模擬設計工作(效力于ADI多芯片產品集團),擁有5年的太空、防務和高度可靠的應用模擬信號鏈模塊設計經驗。Rob于1996年和1998年分別獲得北伊利諾斯州大學(伊利諾斯迪卡爾布市)的電子工程學士(BSEE)學位和電子工程碩士(MSEE)學位。Rob晚上不寫論文或在實驗室研究電路時,他喜歡在健身房活動、聽電子音樂、用舊木板制作家具;最重要的是和他的兩個孩子一起放松自己。

-

放大器

+關注

關注

143文章

13554瀏覽量

213144 -

RF

+關注

關注

65文章

3042瀏覽量

166830 -

GSPS

+關注

關注

0文章

48瀏覽量

16888

發布評論請先 登錄

相關推薦

利用采樣保持放大器和RF ADC從根本上擴展帶寬以突破X波段頻率

RF技術:利用THA從擴展帶寬以突破X波段頻率

RF技術:利用THA從擴展帶寬以突破X波段頻率

評論