對于setup violation,大家一定都非常熟悉,網(wǎng)上也有很多相關(guān)的資料。今天我們來介紹下對于項目后期ECO階段,我們?nèi)绾蝸硇迯?fù)setup violation.

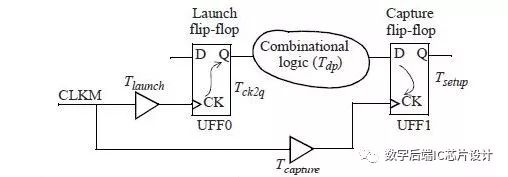

首先我們來回顧一下setup的定義,簡單來說,setup檢查是為了檢查數(shù)據(jù)傳輸不能太慢,否則,在目的寄存器的capture edge不能正確的鎖存數(shù)據(jù)。如下圖所示:

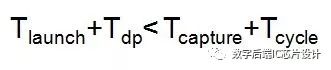

用公式簡單表示為:

Tlaunch為launch clock path delay

Tcapture為capture clock path delay

Tdp為data path delay

Tcycle為時鐘周期

詳細(xì)公式可以查看下列文章

【時序分析基本概念介紹

上述公式成立就代表setup沒有violation,因此我們可以知道修復(fù)setup的主要方法有以下三種:

1. 減小data path的delay

這是我們經(jīng)常使用的修復(fù)setup的方法,但實際上,setup不好修的原因也是在于我們需要在data path上做減法,和hold相反,一般來說,把path變短總是要比把path變長困難許多,這邊列舉了一些經(jīng)常使用到一些減小path delay的方法。

1) Vt Swap

通常是指選用Vt更小或者channel length, 一般的,同一種cell會分為HVT, RVT, LVT, SLVT。他們的速度大小按快到慢依次排列為SLVT, LVT, RVT, HVT。 功耗大小正好相反。每種VT cell又會分為不同的channel length,比如C20, C24, C28,C32。 數(shù)值越高,速度越慢。因此,在項目功耗允許的前提下,我們可以采用Low Vt的cell來替換High Vt的cell,或者選用小的channel length的cell。 這是修復(fù)setup最簡單也最常用的方法。

2)插入BUF

Setup violation其實絕大部分原因是由于drv造成的,我們知道,cell的delay其實是根據(jù)它的input transition,以及output load查表計算得來。因此,我們解決了cap和slew的問題,timing其實自然也得到了解決。那drv的問題,很多一部分我們可以通過插入buf來修復(fù),比如net連接得太長導(dǎo)致驅(qū)動變?nèi)酰梢圆迦隻uf打斷net,來提高驅(qū)動;fanout太大,也可以通過插入buf來減少fanout數(shù)目。

3)Size up cell

這其實也是一種修復(fù)drv的手段,如果某個cell的驅(qū)動能力太弱,比較容易產(chǎn)生比較大的delay,因此我們可以通過size up這個cell來提高驅(qū)動能力,比如X1的BUF換成X4, X8的等。

但是我們在size up cell前也需要注意該cell的輸入/輸出transition的變化情況,因為驅(qū)動能力強(qiáng)的cell,它本身的load會比較大,可能會造成前一級cell驅(qū)動不了它的情況,所以實際的data path情況會比較復(fù)雜,不一定換大驅(qū)動的cell,delay就會變小。

一般情況下,如果我們看到某個cell的output transition比input transition大很多,那說明這個cell的驅(qū)動不夠,我們可以嘗試size up一下。如下圖所示:第一個X1的INV input transition是18.051,而輸出transition是66.328。明顯地時X1的INV推不動下面的14個fanout,可以考慮提高將X1的INV換成驅(qū)動更強(qiáng)的cell。

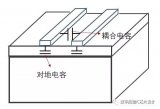

4)Layer assignment

這也是經(jīng)常使用的一種手段,通常來說,高層金屬電阻較小,net delay也較小。這種現(xiàn)象在先進(jìn)工藝中更常出現(xiàn)。我們可以將繞在低層的net,刪除wire后,設(shè)置繞線屬性,讓它繞在高層。

2. 增加capture clock path delay

這也是經(jīng)常使用的一種修復(fù)setup的方法,也就是我們經(jīng)常說的手動useful skew的方法。如果我們發(fā)現(xiàn)在data path上沒有可以明顯減小delay的地方時,我們可以采用在capture clock前墊clock buf的手段來增加capture clock path delay,從而起到修復(fù)setup violation的目的。

但是,由于這樣會動到clock path,所以我們墊buf前還是需要很謹(jǐn)慎的。首先我們得確保從capture clock出發(fā)的下一級path是不是有setup slack margin,同時,檢查一下到當(dāng)前該級register的input pin上的有沒有hold margin。

3. 減小launchclock path delay

這也是動clock path來修復(fù)setup violation的一種方法,不同的我們需要減小launchclock path delay。 這類方法在平時是很少使用到的,原因也是因為減小path delay是很困難的,更何況clock path上用得一般都是最快的cell。理論上我們可以減小clock path的級數(shù)來實現(xiàn),但實際操作起來還是要分析清楚clock的結(jié)構(gòu)。

上述就是一些修復(fù)setup violation的理論手段,在實際的ECO過程中,我們考慮得更多的是,如何提高修timing的效率? 畢竟如果timing path fail較多的話,手動修復(fù)是極其費(fèi)力費(fèi)時的一件事情。

一般signoff工具或者第三方的ECO工具都會自帶timing eco的功能,可以先做幾輪。 到工具修不動時,可以分析下timing報告,同時應(yīng)該要通過腳本處理自動產(chǎn)生一個Vt Swap的ECO腳本。因為,Vt Swap動的東西最少,甚至不需要重新eco route和抽spef,直接在signoff工具可以重新報timing看修復(fù)結(jié)果。

至于剩余的需要手修的path,照著timing report修復(fù)時,需要注意以下幾點:

1)檢查timing path的hold margin。 需要注意的是,一般setup的violation在SS corner下,而hold則出現(xiàn)在FF的corner下面,兩者之間有3倍左右的timing variation。所以,檢查margin時需要考慮不同的corner影響。如果設(shè)計頻率過高的話,可能會出現(xiàn)setup和hold相互打架的情況,這時可以考慮提高net delay占的比重,修出margin。

2)盡量動靠近endpoint的cell。因為越往path后面的cell,影響的path數(shù)目越少。但有時還是需要考慮path分叉情況再決定修復(fù)的方法。

3)修完所有path后,需要在PR工具中對動過的cell重新擺放以及route。

相比hold來說,setup要難修很多,大家在掌握修復(fù)方法以后,應(yīng)該進(jìn)一步考慮如何通過腳本來提高工作的效率。

-

寄存器

+關(guān)注

關(guān)注

31文章

5325瀏覽量

120053 -

Setup

+關(guān)注

關(guān)注

0文章

30瀏覽量

11974

原文標(biāo)題:Less is more——如何修復(fù)setup violation?

文章出處:【微信號:IC_Physical_Design,微信公眾號:數(shù)字后端IC芯片設(shè)計】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

2018年IC設(shè)計企業(yè)筆試題01英偉達(dá)Nvidia

如何使用良好的RTL設(shè)計實踐進(jìn)行修復(fù)

FPGA編譯在place步驟顯示“unusual high hold time violation detected”

MATLAB如何來設(shè)計濾波器

什么是Setup 和Holdup時間?

如何解決“access violation at address”錯誤

如何來手動修復(fù)max transition和max capacitance

Setup軟件安裝可執(zhí)行程序工具免費(fèi)下載

如何修復(fù)ECO階段的Noise Violation

圖形界面介紹:GUI上的按鍵是Violation Browser

通過解剖一個邊沿觸發(fā)器簡要說明setup和hold產(chǎn)生原因

我們?nèi)绾蝸硇迯?fù)setup violation?

我們?nèi)绾蝸硇迯?fù)setup violation?

評論