多核的微控制器(MCU)向來是設計上的一大挑戰,尤其是多核異構的設計。恩智浦半導體早在2011年年底,就率先推出了基于Cortex-M4F和Cortex-M0的雙核MCU——LPC43xx/43Sxx系列, 主頻高達204MHz。憑借其超強的處理性能,很快受到業界的好評。四年之后,MCU雙核精簡版本LPC5411x系列,在廣大LPC發燒友的期待中,終于露出了一代天驕的本色。

雙核MCU:LPC5411x

這款LPC5411x系列MCU集成了Cortex-M4F和Cortex-M0+雙內核,主頻高達100MHz 。因為Cortex-M4F內核采用Harvard架構,3級流水線,支持SIMD,支持單精度浮點運算,單個時鐘周期就能完成一條乘累加(MAC)指令,所以其處理性能強悍,一般用于處理復雜的計算或算法。而Cortex-M0+內核結構簡單,只有2級流水線,能效高,一般用于實時控制、外設管理、數據通信等任務。

在LPC5411x產品中Cortex-M4F是主核,而Cortex-M0+是從核。從核的主要任務是協助主核處理非計算性的雜務,充分解放主核的運算能力,這樣可以達到整個系統的最優性能。

為了實現整體性能最優,LPC5411x采用了多層AHB矩陣式總線架構,以及多個RAM分塊。下圖是LPC5411x的內部功能框圖,可以看到內部的AHB矩陣式總線架構,Cortex-M4F和M0+都是總線上的master,可以訪問所有的片上資源。總線訪問的優先級可以通過寄存器設定。

Cortex-M4F核在AHB總線上有3個接口:I-code, D-code和System總線。而Cortex-M0+只有一個System總線接口。不同的RAM塊可以被不同的AHB master同時訪問。

雙核MCU的存儲區分配

I-code總線用于從CODE內存分區取指令, 地址范圍是:0x0000-0000~0x1FFF-FFFF。D-code總線用于從CODE內存分區取操作數,地址范圍是:0x0000-0000~0x1FFF-FFFF。

當以上兩條總線同時訪問同一內存單元時,D-code總線訪問優先級比I-code高,所以D-code先訪問。對地址范圍從0x2000-0000~0xDFFF-FFFF的訪問是通過System總線進行的,可用于訪問操作數、指令等,數據訪問的優先級高于取指令及中斷向量。

各個存儲區所在的地址區域如下表:

| 存儲區 | 地址區域 | 大小 |

| Flash |

0x0000-0000 ~ 0x0003-FFFF |

256KB |

| Boot ROM |

0x0300-0000 ~ 0x0300-7FFF |

32KB |

| SRAMX |

0x0400-0000 ~ 0x0400-7FFF |

32KB |

| SRAM0 |

0x2000-0000 ~ 0x2000-FFFF |

64KB |

| SRAM1 |

0x2001-0000 ~ 0x2001-FFFF |

64KB |

| SRAM2 |

0x2002-0000 ~ 0x2002-7FFF |

32KB |

為優化系統整體處理能力,需要讓這兩個CPU內核同時以最快速度執行各自指令, 比如Cortex-M4F上能執行單周期的的MAC指令,同時Cortex-M0+上能執行單周期的32位乘法。

因此,存儲區的合理分配策略是,Flash和RAMX以及SRAM0需要分配給Cortex-M4F內核,分別用于存放指令代碼和操作數(見上圖紅/黃框部分)。而SRAM1/SRAM2這兩塊需要分給Cortex-M0+(見上圖綠色框部分)。 需要注意的是,只要其中一個RAM塊分配給某個CPU核,這個RAM塊就不能分配給另一個CPU核, 否則這兩個CPU核同時訪問同一塊區域時,就會出現總線爭用,而導致另一個CPU核訪問出現等待周期,從而降低整個系統處理效率。

雙核運行的功耗如何?

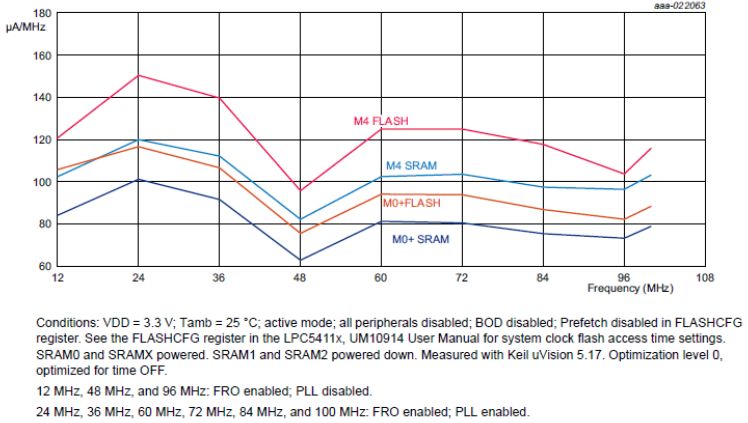

在回答這個問題之前,讓我們看一下其實測的CoreMark動態功耗圖吧:

以代碼放在Flash中運行并且主頻為48MHz為例,Cortex-M4F動態功耗大約為96uA/MHz,而Cortex-M0+為75uA/MHz。兩者之和為171uA/MHz,也就是說雙核同時運行時的功耗為8.2mA。這個功耗比許多其他廠家的單Cortex-M4F核的MCU還低,但性能要強很多。

當然如果你比較關心功耗,可以根據應用實際情況讓一個CPU內核進入低功耗模式,另一個CPU內核工作,等到一定條件時再喚醒另一個核。

雙核之間怎么通信?

下面這張圖說明了倆核之間的通信機制。

當一個CPU內核準備好數據之后,通過互鎖信號放在共享RAM中,再通過郵箱機制產生中斷事件,通知另一個CPU內核來處理。另一個CPU內核處理完數據后,清理相應的中斷標志。通過這種方式可以實現實時性很強的雙核通信和數據交換。也可以不用互鎖信號和共享RAM,直接通過郵箱機制傳遞最多32位的數據。

另外一種簡單的方法叫作消息隊列機制:直接在共享RAM中創建循環緩沖器用于消息隊列。當一個CPU內核準備好數據之后,就把數據發送到這個隊列最后面(隊尾),而另一CPU內核每次從這個隊列的最前面取數據。對每個隊列的訪問是單向的,即一個CPU核只能寫,而另一個CPU內核只能讀。要實現雙向,必須創建至少兩個隊列。 這種方法可以不用互鎖信號,但可以使用中斷機制通知另一個CPU核,以便實現實時通信和數據交換。

雙核的開發很難嗎?

針對雙核以及多核體系架構,恩智浦提供了多核SDK開發庫(稱為MCSDK), 以及豐富的例程,包含在相應多核平臺的MCUXpresso SDK 開發包中。 下圖顯示了MCSDK的架構:

eRPC即嵌入式遠程過程調用(Embedded Remote Procedure Call),是一套實現調用另一核上遠程服務的透明函數調用接口。MCMGR即多核管理器(Multicore Manager),是包含所有CPU內核信息及啟動從核的函數調用接口。RPMsg-Lite即遠程處理器消息機制精簡版(Remote Processor Messaging – Lite),包含了所有處理器間通信的函數庫。

這套庫支持市面上所有主流ARM Cortex-M軟件開發工具,包括IAR、KEIL、GCC,以及MCUXpresso IDE。

有了這套多核SDK開發庫,用戶可以不用關心硬件底層的通信機制,直接使用相應的例程和調用接口,幾分鐘內便可以實現雙核間的通信和數據交換代碼。

下面這個例子說明如何使用RPMsg-Lite,從一個CPU內核發送數據到另一內核:

rpmsg_lite_send(my_rpmsg, my_ept, REMOTE_EPT_ADDR, (char *)&msg,sizeof(msg), …);

其中my_rpmsg是rpmsg_lite_remote_init()或rpmsg_lite_master_init()調用所創建的RPMsg實例;如果是主CPU內核,就用rpmsg_lite_master_init()初始化, 否則就是遠程CPU內核,用rpmsg_lite_remote_init()初始化

my_ept是此消息管道的端點,由rpmsg_lite_create_ept()調用創建的:

my_ept = rpmsg_lite_create_ept(my_rpmsg, LOCAL_EPT_ADDR, …);

msg是真正要交換的消息。

REMOTE_EPT_ADDR,LOCAL_EPT_ADDR分別是此消息管道的遠程端點和本地端點的邏輯地址。

怎么調試雙核應用程序?

在回答這個問題之前,先看一下硬件調試接口圖:

上圖說明,LPC5411x 系列支持對雙核同時調試 ,就像調試單個CPU內核程序一樣簡單。

-

mcu

+關注

關注

146文章

17019瀏覽量

350374 -

雙核

+關注

關注

0文章

37瀏覽量

15180

原文標題:如果你的設計正好需要雙核MCU,請看本文 !

文章出處:【微信號:mcuworld,微信公眾號:嵌入式資訊精選】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

非對稱雙核MCU基礎知識及核間通信

基于雙核MCU提高系統性能

非對稱雙核MCU的基礎知識與重要特點

雙核MCU Pico的相關資料分享

雙核就是任性——LPC Xpresso54102開發板評測

非對稱雙核MCU基礎知識及核間通信

樹莓派不講武德,自研雙核MCU Pico,STM32哭暈在廁所!

如何玩轉HPM6000系列雙核MCU?

玩轉MCU雙核(上) 先楫HPM6000系列雙核怎么玩?答案超乎你想象!

雙核MCU開發其實也不難!

雙核MCU開發其實也不難!

評論