我們都知道,電路板的疊層安排是對PCB的整個系統設計的基礎。疊層設計如有缺陷,將最終影響到整機的emc性能。那么下面就和咱一起來看看到底如何才看懂疊層文件吧~

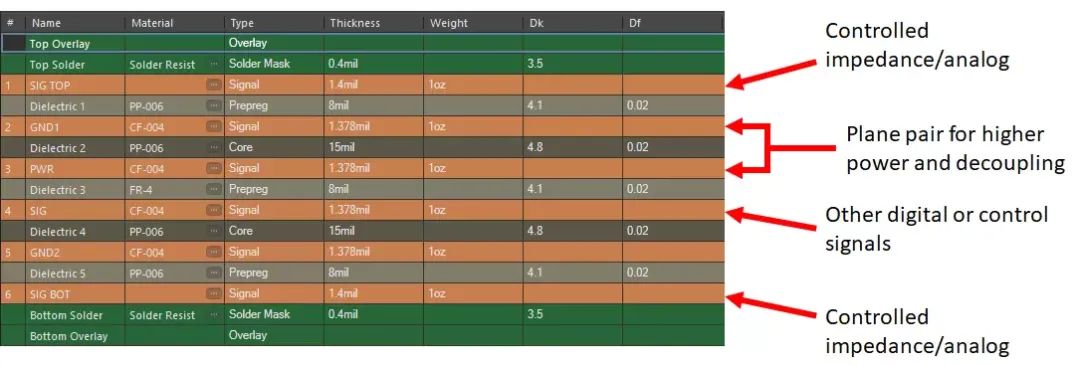

下圖是我們一般情況下看到的疊層好的文件圖示:

一、對(圖一)解析如下:

首先,我們可以看出疊層是8層板,有5個走線層(TOP、ART03、ART04、ART06、BOTTOM),有2個地層(GND02、GND05),有1個電源層(PWR07)。

其次我們可以獲得整個板子的使用的PP片情況,GND02-ART03一張芯板(core),ART4-GND05(core) 一張芯板,ART06-PWR07(core) 一張芯板, 其它的用PP加銅箔,最后壓合在一起而成的。TOP、GND02層中間的PP片是2116半固化片,ART03、ART04層中間的PP片是由2個3313半固化片和1個7628半固化片壓合而成,GND05、ART06層中間的PP片是由2個3313半固化片和1個7628半固化片壓合而成,PWR07、BOTTOM層中間的PP片是2116半固化片。

最后,可得知整個板厚為1.6mm(生產時允許有10%公差)。板厚計算如下示:

次外層2116厚度:

實測厚度=理論厚度—銅厚*(1—殘銅率)

=0.1174*39.3701mil—1.25*(1—65%)

=4.1845mil

內層3313*2+7628 厚度:

實測厚度=理論厚度—銅厚1*(1—殘銅率1)—銅厚2*(1—殘銅率2)

=(0.0987*2+0.1933)*39.3701mil—1.25*(1—65%)—1.25*(1—15%)

=13.8819mil

理論板厚:

板厚=內外層銅厚+PP片厚度+芯板厚度

=0.7087*2+1.25*6+4.1845*2+13.8819*2+5.1*3

=60.3502mil

=1.5329mm

二、咱們接著疊層好的文件圖二

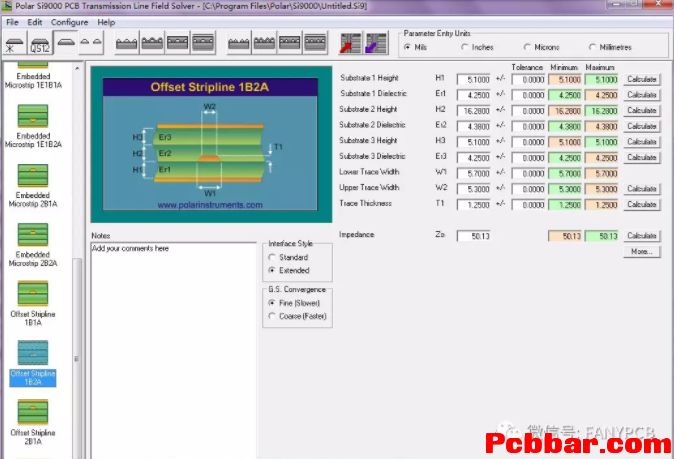

從(圖二)上,可以知道各個走線層單端50R阻抗的走線寬度和參考層。其中TOP、BOTTOM層走線寬度為6mil,TOP層參考GND02層,BOTTOM參考PWR07層;ART03、ART04層走線寬度為5.7mil,ART03層參考GND02層,ART04參考GND05層;ART06層走線寬度為5.4mil, ART06參考GND05、PWR07層。具體數值我們可以從Polar SI軟件中計算出來。

(1) 表層單端(TOP、BOTTOM):線寬6mil; =51.51*0.9+3.2=49.56

(2)內層單端(ART03、ART04):線寬5.7mil; =50.13

(3)內層單端(ART06):線寬5.4mil; =50.08

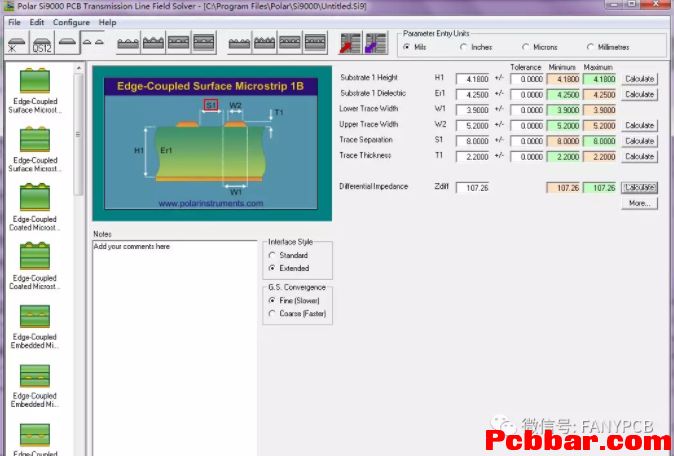

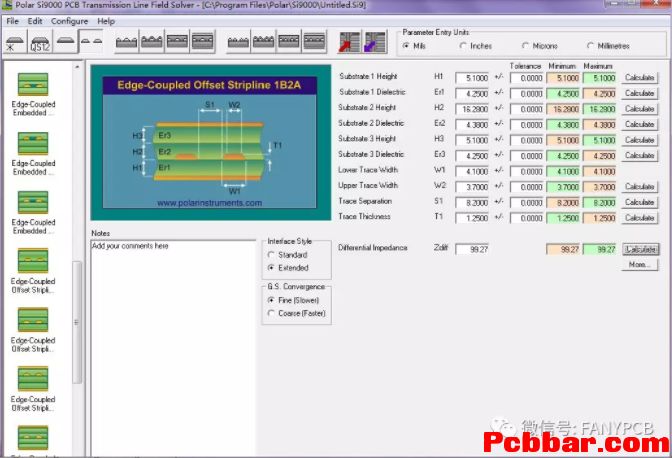

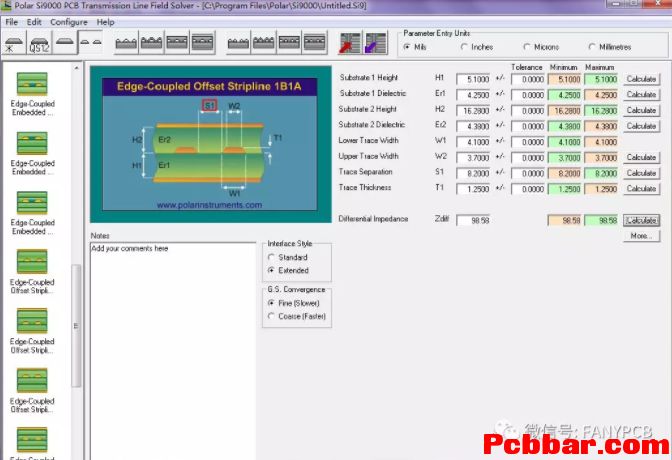

現在,接著疊層好的文件圖三三、從(圖三)我們可以知道各個走線層差分100R阻抗的走線寬度、線間間隙和參考層。其中TOP、BOTTOM層走線寬度為4.5mil,線與線間隙8mil,TOP層參考GND02層,BOTTOM參考PWR07層;ART03、ART04層走線寬度為4.1mil,線與線間隙8.2mil,ART03層參考GND02層,ART04參考GND05層;ART06層走線寬度為4.1mil,線與線間隙8.2mil, ART06參考GND05、PWR07層。具體數值我們可以從Polar SI軟件中計算出來。(1) 表層差分(TOP、BOTTOM):線寬/線距 4.5/8mil; =107.26*0.9+3.2=99.734

(2)內層差分(ART3/ART4層): 線寬/線距 4.1/8.2mil; =99.27

(3) 內層差分(ART6層): 線寬/線距 4.1/8.2mil; =98.58

-

pcb

+關注

關注

4317文章

23002瀏覽量

396233 -

電路板

+關注

關注

140文章

4905瀏覽量

97409 -

疊層

+關注

關注

0文章

28瀏覽量

9827 -

可制造性設計

+關注

關注

10文章

2065瀏覽量

15469 -

華秋DFM

+關注

關注

20文章

3493瀏覽量

4375

原文標題:干貨||3分鐘教你看懂PCB疊層文件

文章出處:【微信號:FANYPCB,微信公眾號:凡億PCB】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

6層PCB疊層設計指南

3分鐘教你看懂PCB疊層文件

3分鐘教你看懂PCB疊層文件

評論