EDA(Vivado)軟件可以很好的幫助我們更好的去學習FPGA相關知識,例如:

記得使用EDA軟件自帶的語言模板;

新建 IO Planning工程初步引腳分配;

EDA中自帶的IP核你會快速用嗎?

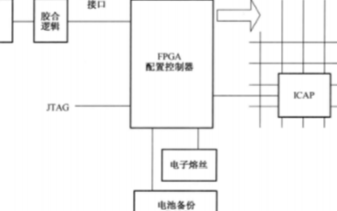

單片機是基于FLASH結構的,所以單片機上電直接從本地FLASH中運行。但SRAM 架構的FPGA是基于SRAM結構的,掉電數據就沒了,所以需要借助外部電路來配置運行的數據,其實我們可以借助Vivado來學習FPGA的各種配置模式。

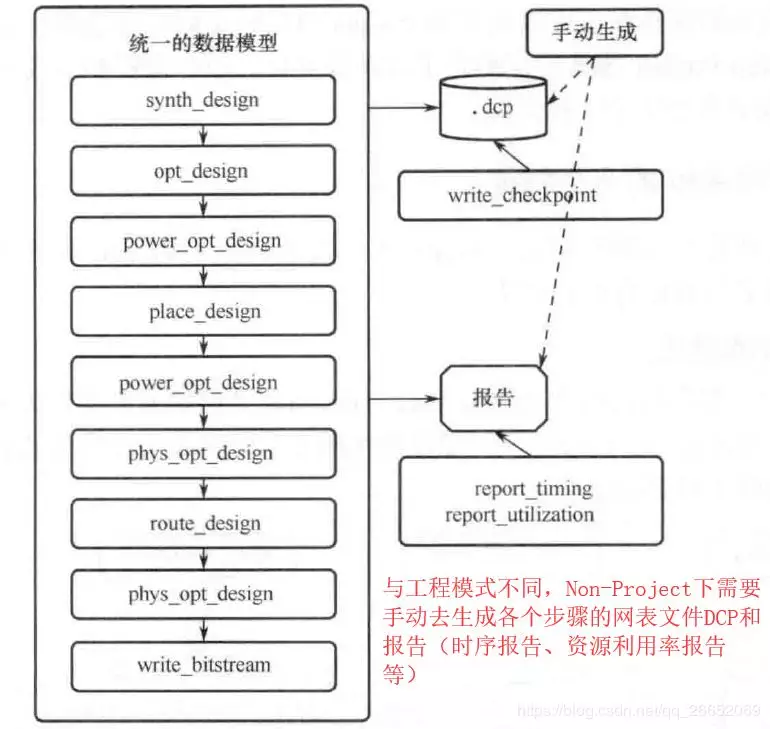

Step1,找到Vivado的設計流程框:

Step2,打開設置菜單,并選擇BitSream子選項。此時,可以看到提示:Open Implemented Design后有更多的設置項可用:

Step3,當我們Open Implemented Design后,再打開這個BitSream設置菜單選項,會發(fā)現(xiàn)提示為Confgure additional bitstream settings,此時可以單擊進入更多的設置菜單:

Step4,當我們單擊進入更詳細的菜單后有很多設置項,當我們打開Configuration Modes這是子設置項后,我們可以看到FPGA的各種配置模式:SPI、SelecMap、Master、Slave等,這里包括這些配置模式的參考電路和其它設置項:

Step5,打開MasterSPIx1,可以看到電路和幫助鏈接(7 Series Configuration User Guide),單擊這個鏈接打開后就可以對應的幫助文檔。至此,我們就可以通過這些電路和鏈接對應的幫助文檔來學習FPGA的配置模式。

我們再打開SlaveSerial模式,在這里,可以看到電路的設計設計是可以通過外部CPLD或者MCU單片機來配置FPGA,所以有些板子你可能很奇怪只看到了FPGA+DSP而沒有看到任何FLASH外設的時候,很可能就是采用DSP來配置FPGA的,F(xiàn)PGA的配置數據就存儲在DSP的FLASH中:

這次就不具體展開FPGA的具體配置相關內容,我們可以通過Vivado讓我們很直觀的看到FPGA的配置模式和對應的電路設計,對我們設計開發(fā)FPGA有很大幫助。另外,F(xiàn)PGA多重配置可參考:

Xilinx FGPA的多重配置功能(1)

Xilinx FPGA的多重配置功能(2)

-

FPGA

+關注

關注

1626文章

21665瀏覽量

601803 -

單片機

+關注

關注

6032文章

44514瀏覽量

632946

原文標題:借助vivado來學習FPGA配置模式

文章出處:【微信號:fpga234,微信公眾號:fpga234】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

借助USB來完成系統(tǒng)配置

如何使用Vivado Device Programmer創(chuàng)建和配置存儲設備

FPGA JTAG的配置模式詳細說明

【FPGA Vivado】基于 FPGA Vivado 的流水燈樣例設計

借助Vivado來學習FPGA的各種配置模式

借助Vivado來學習FPGA的各種配置模式

評論