USB 通用串行總線(Universal Serial Bus),目前我們所說的 USB 一般都是指 USB2.0,USB2.0 接口是目前許多高速數據傳輸設備的首選接口,從 1.1 過渡到 2.O,作為其重要指標的設備傳輸速度,從 1.5 Mbps 的低速和 12 Mbps 的全速,提高到如今的 480 Mbps 的高速。USB 的特點不用多說大家也知道就是:速度快、功耗低、支持即插即用、使用安裝方便。正是因為其以上優點現在很多視頻設備也都采用 USB 傳輸。

對于高速數據傳輸 PCB 板設計最主要的就是差分信號線設計,設計好壞關乎整個設備能否正常運行。

1

USB2.0 接口差分信號線設計

USB2.0 協議定義由兩根差分信號線(D、D-)傳輸高速數字信號,最高的傳輸速率為 480 Mbps。差分信號線上的差分電壓為 400 mV,理想的差分阻抗(Zdiff)為 90(1±O.1)Ω。在設計 PCB 板時,控制差分信號線的差分阻抗對高速數字信號的完整性是非常重要的,因為差分 阻抗影響差分信號的眼圖、信號帶寬、信號抖動和信號線上的干擾電壓。由于不同軟件測量存在一定偏差,所以一般我們都是要求控制在 80Ω 至 100Ω 間。

差分線由兩根平行繪制在PCB板表層(頂層或底層)發生邊緣耦合效應的微帶線(Microstrip)組成的,其阻抗由兩根微帶線的阻抗及其和決定,而微帶線的阻抗(Zo)由微帶線線寬(W)、微帶線走線的銅皮厚度(T)、微帶線到最近參考平面的距離(H)以及PCB板材料的介電常數(Er)決定,其計算公式為:Zo={87/sqrt(Er 1.41)]}ln[5.98H/(0.8W T)]。影響差分線阻抗的主要參數為微帶線阻抗和兩根微帶線的線間距(S)。當兩根微帶線的線間距增加時,差分線的耦合效應減弱,差分阻抗增大;線間距減少時,差分線的耦合效應增強,差分阻抗減小。差分線阻抗的計算公式為:

Zdiff=2Zo(1-0.48exp(-0.96S/H))。微帶線和差分線的計算公式在O.1

?在繪制 USB2.O 設備接口差分線時,應注意以下幾點要求:

①在元件布局時,應將USB2.O 芯片放置在離地層最近的信號層,并盡量靠近 USB 插座,縮短差分 線走線距離。

②差分線上不應加磁珠或者電容等濾波措施,否則會嚴重影響差分線的阻抗。

③如果 USB2.O 接口芯片需串聯端電阻或者 D 線接上拉電阻時,務必將這些電阻盡可能的靠近芯片放置。

④將 USB2.O 差分信號線布在離地層最近的信號層。

⑤在繪制 PCB 板上其他信號線之前,應完成 USB2.0 差分線和其他差分線的布線。

⑥保持 USB2.O 差分線下端地層完整性,如果分割差分線下端的地層,會造成差分線阻抗的不連續性,并會增加外部噪聲對差分線的影響。

⑦在 USB2.0 差分線的布線過程中,應避免在差分線上放置過孔(via),過孔會造成差分線阻抗失調。如果必須要通過放置過孔才能完成差 分線的布線,那么應盡量使用小尺寸的過孔,并保持 USB2.0 差分線在一個信號層上。

⑧保證差分線的線間距在走線過程中的一致性,使用 Cadence 繪圖時可以用shove 保證,但在使用 Protel繪圖時要特別注意。如果在 走線過程中差分線的間距發生改變,會造成差分線阻抗的不連續性。

⑨在繪制差分線的 過程中,使用 45°彎角或圓弧彎角來代替 90°彎角,并盡量在差分線周圍的 150 mil 范圍內不要走其他的信號線,特別是邊沿比較陡峭的數字信號線更加要注意其走線不能影響 USB 差分線。

⑩差分線要盡量等長,如果兩根線長度相差較大時,可以繪制蛇行線增加短線長度。

2

USB2.0 總線接口端電源線和地線設計

USB 接口有 5 個端點,分別為:USB 電源(VBUS)、D-、D 、信號地(GND)和保護地(SHIELD)。上面已經介紹過如何設計 D 、D-差分信號了,正確設計 USB 總線電源、信號地和保護地對USB 系統的正常工作也是同樣重要的。

USB 電源線電壓為 5 V,提供的最大電流為500mA,應將電源線布置在靠近電源層的信號層上,而不是布置在與 USB 差分線所在的相同層上,線寬應在 30mil 以上,以減少它對差分信號線的干擾。現在很多廠家的 USB 從控制芯片工作電壓為 3.3 V,當其工作在總線供電模式時,需要 3.3~5 V 的電源轉換芯片,電源轉換芯片的輸出端應盡量靠近 USB 芯片的電壓輸入端,并且電源轉換芯片的輸入和輸出端都應加大容量電容并聯小容量電容進行濾波。當 USB 從控制芯片工作在自供電的模式時,USB 電源線可以串聯一個大電阻接到地。

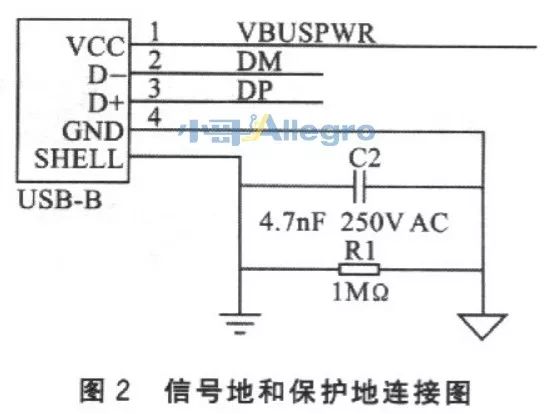

USB 接口的信號地應與 PCB 板上的信號地接觸良好,保護地可以放置在 PCB板的任何一層上,它和信號地分割開,兩個地之間可以用一個大電阻并聯一個耐壓值較高的電容,如圖 2 所示。

保護地和信號地之間的間距不應小于 25mil, 以減少兩個地之間的邊緣耦合作用。保護地不要大面積覆銅,一根 100mli 寬度的銅箔線就已能滿足保護地的功能需要了。

?在繪制 USB 電源線、信號地和保護地時,應注意以下幾點:

①USB 插座的 1、2、3、4 腳應在信號地的包圍范圍內,而不是在保護地的包圍范圍內。

②USB 差分信號線和其他信號線在走線的時候不應與保護地層出現交疊。

③電源層和信號地層在覆銅的時候要注意不應與保護地層出現交疊。

④電源層要比信號地層內縮20D,D 為電源層與信號地層之間的距離。

⑤如果差分線所在層的信號地需要大面積覆銅,注意信號地與差分線之間要保證 35 mil 以上的間距,以免覆銅后降低差分線的阻抗。

⑥在其他信號層可以放置一些具有 信號地屬性的過孔,增加信號地的連接性,縮短信號電流回流路徑。

⑦在 USB 總線的 電源線和 PCB 板的電源線上,可以加磁珠增加電源的抗干擾能力。

3

USB2.0 其他信號的拓撲結構設計

USB2.O 提供高達 480 Mbps 的傳輸速率,因此芯片需要外接一個較高頻率的晶振,例如 Cypress 公司的 CY7C68013 需要外接 1 個 24 MHz 的晶振。晶振應盡量靠近 USB 芯片的時鐘輸入腳,時鐘線不能跨越 USB2.0 的差分線,晶振下不要布置任何信號線,并且在時鐘線周圍應覆有完整的信號地,以降低時鐘線對其他信號線的干擾,特別是對差分線的干擾。在繪制USB 芯片與其他芯片相連的數據線時,應保證線間距不小于 8mil。

按 EMC、EMI 原理和信號完整性要求設計的 USB2.0 設備 PCB 板,傳輸速率可以達到 300 Mbps 以上。高速數字信號傳輸 PCB 板設計是一個比較復雜的領域,對設計人員的要求比較高,設計周期也比較長。

-

pcb

+關注

關注

4295文章

22776瀏覽量

393239 -

usb

+關注

關注

60文章

7773瀏覽量

262389

原文標題:USB_2.0高速PCB走線詳盡要點

文章出處:【微信號:pcb3com,微信公眾號:小哥Allegro】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

USB2.0 PCB布線設計

USB模塊,USB2.0模塊,USB數據采集模塊,USB開發板

USB模塊,USB2.0模塊,USB數據采集模塊,USB開發板

labview難以高速接收USB2.0數據

基于USB2.0的數據傳輸接口轉換系統

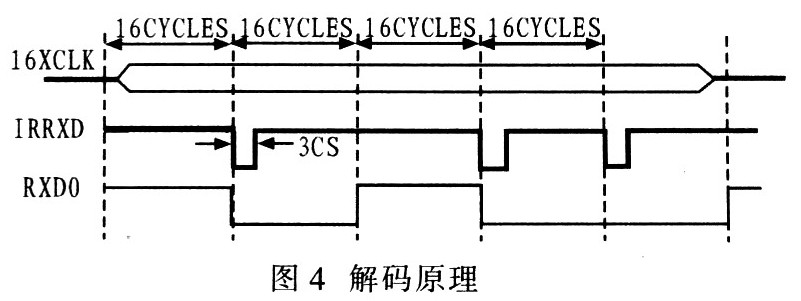

基于USB2.0的紅外數據傳輸系統

基于USB2.0的紅外數據傳輸系統的設計與實現

基于USB2.0的通用數據傳輸模塊實現方案

USB2.0設備高速數據傳輸PCB板設計

USB2.0設備高速數據傳輸PCB板設計

評論