串行外設接口 (SPI) 是微控制器和外圍 IC(如傳感器、ADC、DAC、 移位寄存器、SRAM等)之間使用最廣泛的接口之一。SPI 是一種同步、全雙工、主從式接口。來自主機或從機的數據在時鐘上升沿或下降沿同步。主機和從機可以同時傳輸數據。SPI 接口可以是3線式或4線式。

◆◆接口◆◆

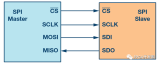

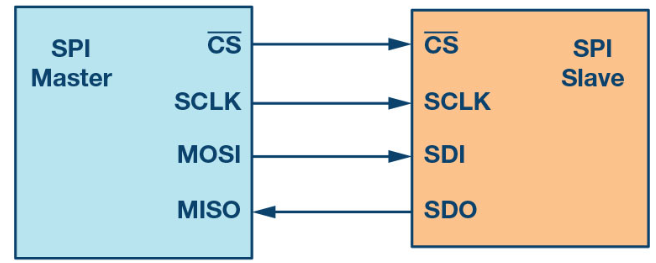

4 線 SPI 器件有四個信號:

時鐘(SPICLK,SCLK)

片選(CS)主機輸出

從機輸入(MOSI)主機輸入

從機輸出(MISO)

產生時鐘信號的器件稱為主機。主機和從機之間傳輸的數據與主機產生的時鐘同步。同I2C接口相比,SPI器件支持更高的時鐘頻率。用戶應查閱產品數據手冊以了解SPI接口的時鐘頻率規格。

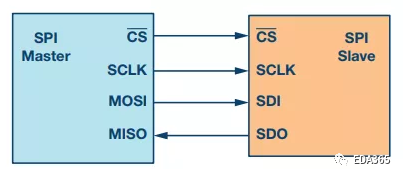

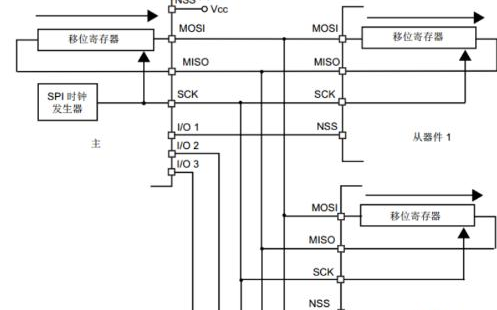

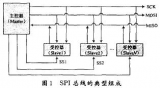

SPI接口只能有一個主機,但可以有一個或多個從機。圖1顯示了主機和從機之間的SPI連接。

圖1. 含主機和從機的SPI配置

來自主機的片選信號用于選擇從機。這通常是一個低電平有效信號,拉高時從機與SPI總線斷開連接。當使用多個從機時,主機需要為每個從機提供單獨的片選信號。本文中的片選信號始終是低電平有效信號。

MOSI和MISO是數據線。MOSI將數據從主機發送到從機,MISO將數據從從機發送到主機。

◆◆數據傳輸◆◆

要開始SPI通信,主機必須發送時鐘信號,并通過使能CS信號選擇從機。片選通常是低電平有效信號。因此,主機必須在該信號上發送邏輯0以選擇從機。

SPI是全雙工接口,主機和從機可以分別通過MOSI和MISO線路同時發送數據。在SPI通信期間,數據的發送(串行移出到MOSI/SDO總線上)和接收(采樣或讀入總線(MISO/SDI)上的數據)同時進行。串行時鐘沿同步數據的移位和采樣。

SPI接口允許用戶靈活選擇時鐘的上升沿或下降沿來采樣和/或移位數據。欲確定使用SPI接口傳輸的數據位數,請參閱器件數據手冊。

◆◆時鐘極性和時鐘相位◆◆

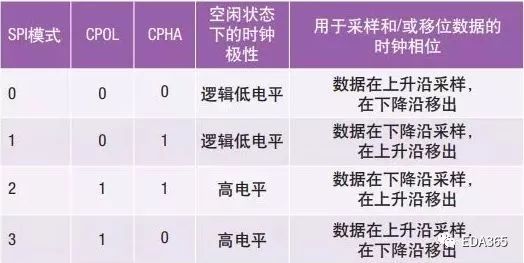

在SPI中,主機可以選擇時鐘極性和時鐘相位。在空閑狀態期間,CPOL位設置時鐘信號的極性。空閑狀態是指傳輸開始時CS為高電平且在向低電平轉變的期間,以及傳輸結束時CS為低電平且在向高電平轉變的期間。CPHA位選擇時鐘相位。

根據CPHA位的狀態,使用時鐘上升沿或下降沿來采樣和/或移位數據。主機必須根據從機的要求選擇時鐘極性和時鐘相位。根據CPOL和CPHA位的選擇,有四種SPI模式可用。表1顯示了這4種SPI模式。

表1.通過CPOL和CPHA選擇SPI模式

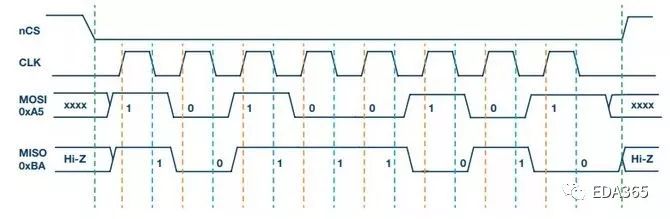

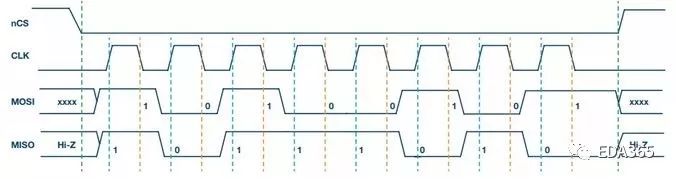

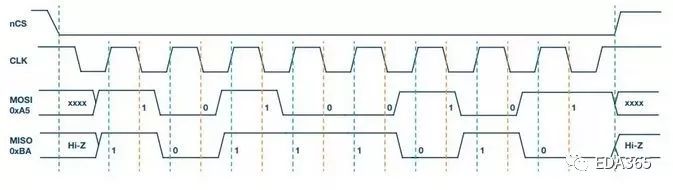

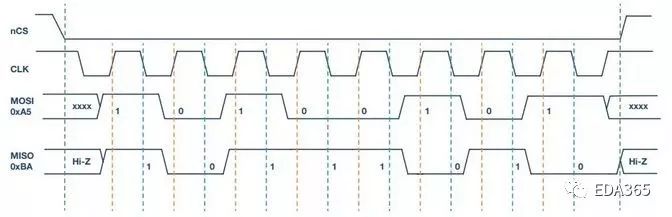

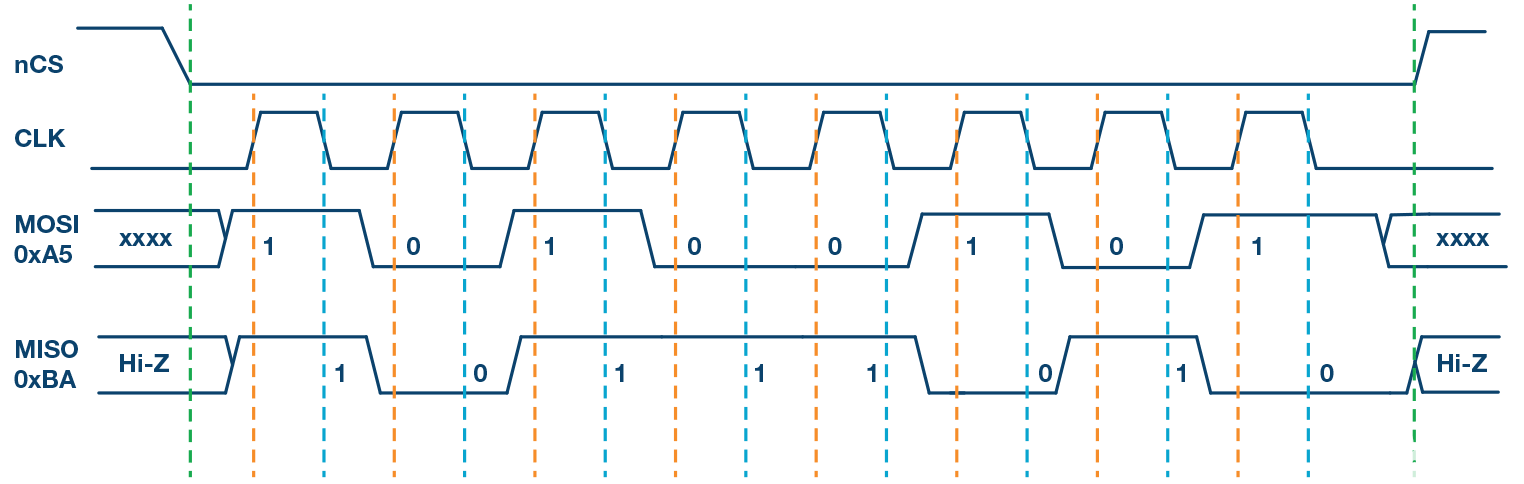

圖2至圖5顯示了四種SPI模式下的通信示例。在這些示例中,數據顯示在MOSI和MISO線上。傳輸的開始和結束用綠色虛線表示,采樣邊沿用橙色虛線表示,移位邊沿用藍色虛線表示。請注意,這些圖形僅供參考。要成功進行SPI通信,用戶須參閱產品數據手冊并確保滿足器件的時序規格。

圖2. SPI模式0,CPOL = 0,CPHA = 0:CLK空閑狀態 = 低電平,數據在上升沿采樣,并在下降沿移出

圖3給出了SPI模式1的時序圖。在此模式下,時鐘極性為0,表示時鐘信號的空閑狀態為低電平。此模式下的時鐘相位為1,表示數據在下降沿采樣(由橙色虛線顯示),并且數據在時鐘信號的上升沿移出(由藍色虛線顯示)。

圖3. SPI模式1,CPOL = 0,CPHA = 1:CLK空閑狀態 = 低電平,數據在下降沿采樣,并在上升沿移出

圖4. SPI模式2,CPOL = 1,CPHA = 1:CLK空閑狀態 = 高電平,數據在下降沿采樣,并在上升沿移出

圖4給出了SPI模式2的時序圖。在此模式下,時鐘極性為1,表示時鐘信號的空閑狀態為高電平。此模式下的時鐘相位為1,表示數據在下降沿采樣(由橙色虛線顯示),并且數據在時鐘信號的上升沿移出(由藍色虛線顯示)。

圖5. SPI模式3,CPOL = 1,CPHA = 0:CLK空閑狀態 = 高電平,數據在上升沿采樣,并在下降沿移出

圖5給出了SPI模式3的時序圖。在此模式下,時鐘極性為1,表示時鐘信號的空閑狀態為高電平。此模式下的時鐘相位為0,表示數據在上升沿采樣(由橙色虛線顯示),并且數據在時鐘信號的下降沿移出(由藍色虛線顯示)。

◆◆多從機配置◆◆

多個從機可與單個SPI主機一起使用。從機可以采用常規模式連接,或采用菊花鏈模式連接。

常規SPI模式

在常規模式下,主機需要為每個從機提供單獨的片選信號。一旦主機使能(拉低)片選信號,MOSI/MISO線上的時鐘和數據便可用于所選的從機。如果使能多個片選信號,則MISO線上的數據會被破壞,因為主機無法識別哪個從機正在傳輸數據。

從圖6可以看出,隨著從機數量的增加,來自主機的片選線的數量也增加。這會快速增加主機需要提供的輸入和輸出數量,并限制可以使用的從機數量。可以使用其他技術來增加常規模式下的從機數量,例如使用多路復用器產生片選信號。

圖6. 多從機SPI配置

菊花鏈模式

在菊花鏈模式下,所有從機的片選信號連接在一起,數據從一個從機傳播到下一個從機。在此配置中,所有從機同時接收同一SPI時鐘。來自主機的數據直接送到第一個從機,該從機將數據提供給下一個從機,依此類推。

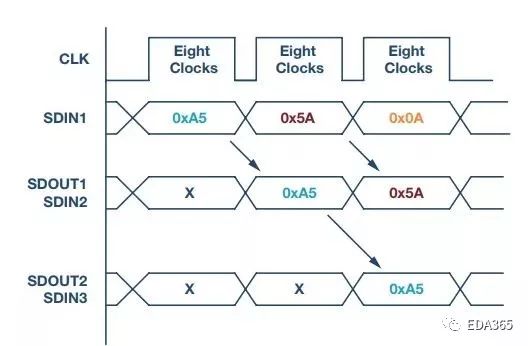

使用該方法時,由于數據是從一個從機傳播到下一個從機,所以傳輸數據所需的時鐘周期數與菊花鏈中的從機位置成比例。例如在圖7所示的8位系統中,為使第3個從機能夠獲得數據,需要24個時鐘脈沖,而常規SPI模式下只需8個時鐘脈沖。

圖7. 多從機SPI菊花鏈配置

圖8顯示了時鐘周期和通過菊花鏈的數據傳播。并非所有SPI器件都支持菊花鏈模式。請參閱產品數據手冊以確認菊花鏈是否可用。

圖8. 菊花鏈配置:數據傳播

ADI公司最新一代支持SPI的開關可在不影響精密開關性能的情況下顯著節省空間。本文的這一部分將討論一個案例研究,說明支持SPI的開關或多路復用器如何能夠大大簡化系統級設計并減少所需的GPIO數量。

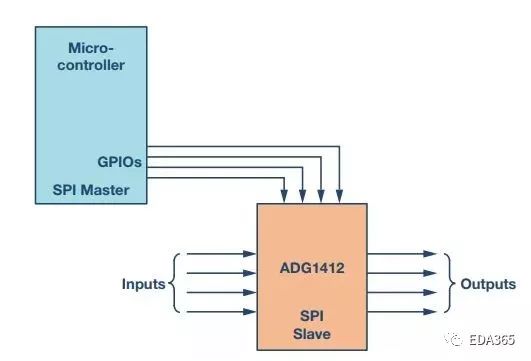

ADG1412是一款四通道、單刀單擲(SPST)開關,需要四個GPIO連接到每個開關的控制輸入。圖9顯示了微控制器和一個ADG1412之間的連接。

圖9. 微控制器GPIO用作開關的控制信號

隨著電路板上開關數量的增加,所需GPIO的數量也會顯著增加。例如,當設計一個測試儀器系統時,會使用大量開關來增加系統中的通道數。在4×4交叉點矩陣配置中,使用四個ADG1412。此系統需要16個GPIO,限制了標準微控制器中的可用GPIO。圖10顯示了使用微控制器的16個GPIO連接四個ADG1412。

圖10. 在多從機配置中,所需GPIO的數量大幅增加

◆◆如何減少 GPIO 數量?◆◆

一種方法是使用串行轉并行轉換器,如圖11所示。該器件輸出的并行信號可連接到開關控制輸入,器件可通過串行接口SPI配置。此方法的缺點是外加器件會導致物料清單增加。

圖11. 使用串行轉并行轉換器的多從機開關

另一種方法是使用SPI控制的開關。此方法的優點是可減少所需GPIO的數量,并且還能消除外加串行轉并行轉換器的開銷。如圖12所示,不需要16個微控制器GPIO,只需要7個微控制器GPIO就可以向4個ADGS1412提供SPI信號。開關可采用菊花鏈配置,以進一步優化GPIO數量。在菊花鏈配置中,無論系統使用多少開關,都只使用主機(微控制器)的四個GPIO。

圖12. 支持SPI的開關節省微控制器GPIO

圖13用于說明目的。ADGS1412數據手冊建議在SDO引腳上使用一個上拉電阻。為簡單起見,此示例使用了四個開關。隨著系統中開關數量的增加,電路板簡單和節省空間的優點很重要。

圖13. 菊花鏈配置的SPI開關可進一步優化GPIO

在6層電路板上放置8個四通道SPST開關,采用4×8交叉點配置時,ADI 公司支持 SPI 的開關可節省20%的總電路板空間。

-

接口

+關注

關注

33文章

8497瀏覽量

150834 -

SPI

+關注

關注

17文章

1700瀏覽量

91319

原文標題:一文讀懂 4 線 SPI

文章出處:【微信號:eda365wx,微信公眾號:EDA365電子論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

介紹常用的4線SPI接口

STM32的SPI接口、cubeMX軟件配置SPI接口和分析SPI相關代碼

SPI接口通信協議詳解:SPI時序、2線、3線、4線SPI及4種常用工作模式

SPI接口如何幫助減少系統板設計中的數字GPIO數量

重點介紹常用的4線SPI接口

重點介紹常用的4線SPI接口

評論