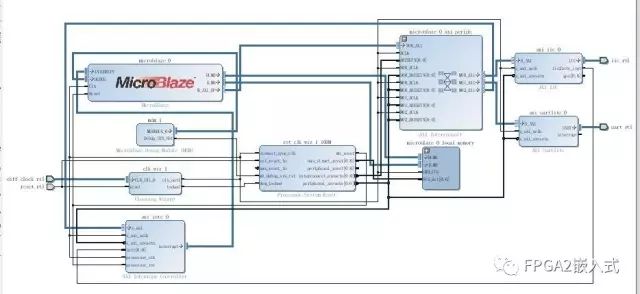

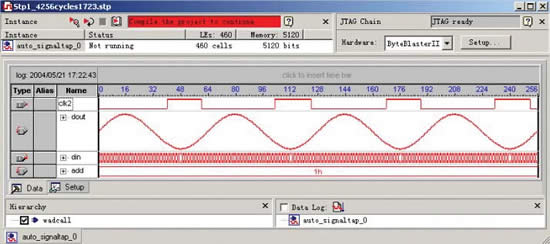

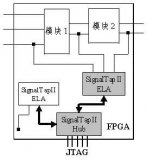

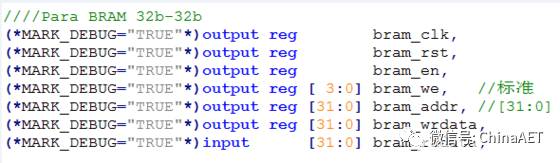

上一篇文章的介紹大家多少對ila核的使用有一些了解吧。在做純邏輯的設(shè)計時,添加ILA核,然后在代碼中進行定義就可以了。但FPGA已經(jīng)不僅僅只是純邏輯這么簡單了,當(dāng)你一個工程做到嵌入式層面,你就會使用軟核,這時就會使用到畫布。如下圖所示,其中Microblaze就是一個處理器,可以看到各模塊都是一個個IP核,我們無法對代碼進行修改,如果這時我們要查看某個模塊的端口改怎么辦呢?不能在代碼中定義一個ILA核呀!

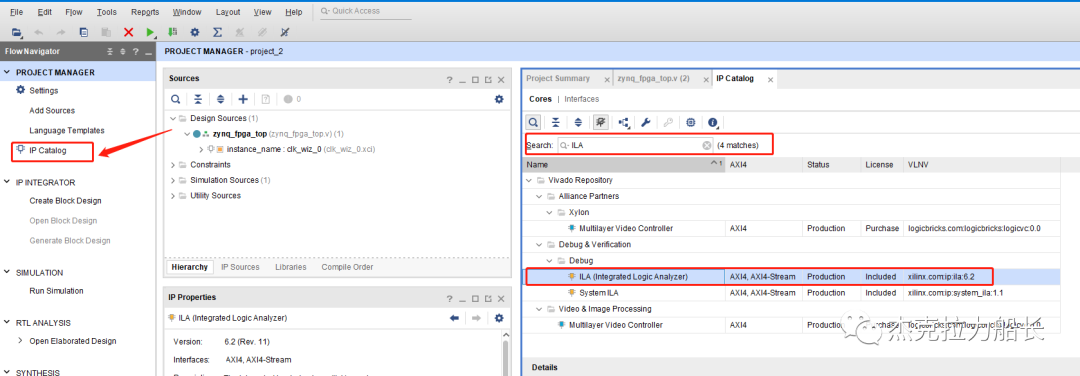

其實這兒便很簡單了,可以直接在畫布上添加一個ILA核,再把想要的信號線連進來就行了呀,都不需要在代碼里定義這個ILA核。不過這樣做就說明你還沒能靈活的使用Xilinx的在線調(diào)試工具了,因為還有更簡單的辦法哈哈。

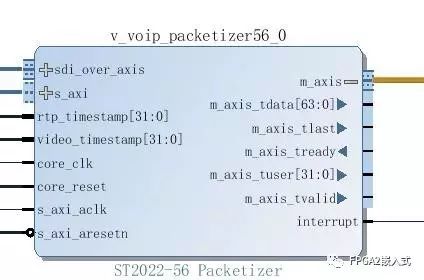

如下圖所示,對于這個IP核,他的輸出是axi_stream,我們?nèi)绻胍榭此墓ぷ鲿r序該怎么做呢?

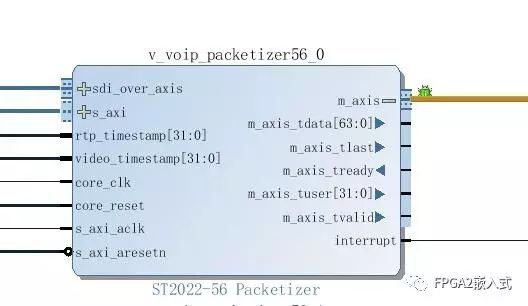

首先我們選擇他的信號線,右鍵,就可以看到一個選項“Mark Debug”,選擇后就會有一個綠色的甲蟲出現(xiàn),這時說明axi_stream所有信號都被引入到ILA中了。

如果我們不想加入這個調(diào)試信號,直接右鍵,會有“Unmark Debug”選項,單擊便會取消了。

然后在Vivado中點擊保存,這樣便完成了調(diào)試信號的添加了,是不是很方便。

這種方式大家先慢慢消化一下吧,后面再給大家介紹另一種調(diào)試方式,嘿嘿。

-

FPGA

+關(guān)注

關(guān)注

1626文章

21665瀏覽量

601818 -

Xilinx

+關(guān)注

關(guān)注

71文章

2163瀏覽量

121005

原文標(biāo)題:FPGA開發(fā)要懂得使用硬件分析儀調(diào)試——ILA(2)

文章出處:【微信號:FPGAer_Club,微信公眾號:FPGAer俱樂部】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

使用邏輯分析儀Acute TravelLogic Analyzer進行SPI NAND驅(qū)動開發(fā)調(diào)試

集成邏輯分析儀(ILA)的使用方法

如何用內(nèi)部邏輯分析儀調(diào)試FPGA?

Vivado邏輯分析儀使用教程

TLA邏輯分析儀原理與應(yīng)用硬件調(diào)試基礎(chǔ)教程

TLA邏輯分析儀原理與應(yīng)用 (硬件調(diào)試基礎(chǔ)教程)

使用SignalTap II邏輯分析儀調(diào)試FPGA

傳統(tǒng)FPGA調(diào)試方案與EXOSTIV Probe硬件調(diào)試儀

SignalTap II的特點、設(shè)置流程及邏輯分析儀的設(shè)計

采用內(nèi)部或者嵌入式邏輯分析儀推動FPGA調(diào)試技術(shù)改變

FPGA設(shè)計與調(diào)試教程說明

Vivado中關(guān)于ILA的詳解

Vivado之ILA詳解

在Vivado中使用邏輯分析儀ILA的過程

如何用內(nèi)部邏輯分析儀調(diào)試FPGA?

FPGA開發(fā)要懂得使用硬件分析儀調(diào)試——ILA

FPGA開發(fā)要懂得使用硬件分析儀調(diào)試——ILA

評論