聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

賽靈思

+關注

關注

32文章

1794瀏覽量

130960 -

C++

+關注

關注

21文章

2085瀏覽量

73301 -

編譯

+關注

關注

0文章

646瀏覽量

32668

發布評論請先 登錄

相關推薦

優化 FPGA HLS 設計

,打開項目文件。當提示要使用的 Vivado 版本時,請使用“相同”的 Vivado 版本。例如,如果使用2017.3 HLS,請使用2017.3

發表于 08-16 19:56

創建Aurix項目失敗怎么解決?

我嘗試創建一個新的 Aurix 項目,但點擊底部的 "完成 "后,沒有創建新文件,工作區仍然是空的。

我在論壇上搜索了這個問題,發現很多人都遇到過這個問題,但仍然沒有解決方案。

發表于 07-23 07:49

如何禁止vivado自動生成 bufg

操作: 打開Vivado工程,并進入項目導航器窗口。 選擇下方的"IP"選項卡,展開"Clocking"選項。在這

AMD-Xilinx的Vitis-HLS編譯指示小結

我們在在 RTL 設計中創建循環主體的多個副本,使得運行這段代碼只耗費1個時鐘周期:

for(int i = 0; i < 8; i++) {

#pragma HLS unroll

a[i

發表于 12-31 21:20

idea怎么創建Java項目

創建Java項目是一個相對較為復雜的過程,需要考慮到各種細節和步驟。本文將詳細介紹如何創建一個Java項目。 一、準備工作 在創建Java

怎么用eclipse創建web項目

使用Eclipse創建Web項目是一種常見的方式,下面將分步驟詳解如何使用Eclipse創建Web項目。在開始之前,請確保已經安裝了Java開發工具包(JDK)和Eclipse集成開發

研討會:利用編譯器指令提升AMD Vitis? HLS 設計性能

AMD Vitis 高層次綜合 ( HLS ) 已成為自適應 SoC 及 FPGA 產品設計領域的一項顛覆性技術,可在創建定制硬件設計時實現更高層次的抽象并提高生產力。Vitis HLS 通過將 C

使用Vivado高層次綜合(HLS)進行FPGA設計的簡介

電子發燒友網站提供《使用Vivado高層次綜合(HLS)進行FPGA設計的簡介.pdf》資料免費下載

發表于 11-16 09:33

?0次下載

Vivado Design Suite 用戶指南:編程和調試

《Vivado Design Suite 用戶指南:編程和調試》 文檔涵蓋了以下設計進程: 硬件、IP 和平臺開發 : 為硬件平臺創建 PL IP 塊、創建 PL 內核、功能仿真以及評估 AMD

【KV260視覺入門套件試用體驗】硬件加速之—使用PL加速矩陣乘法運算(Vitis HLS)

Virtual Cable)調試FPGA邏輯

三、硬件加速之—使用PL加速FFT運算(Vivado)

四、硬件加速之—使用PL加速矩陣乘法運算(Vitis HLS)

后四期測評計劃:

五、Vitis AI

發表于 10-13 20:11

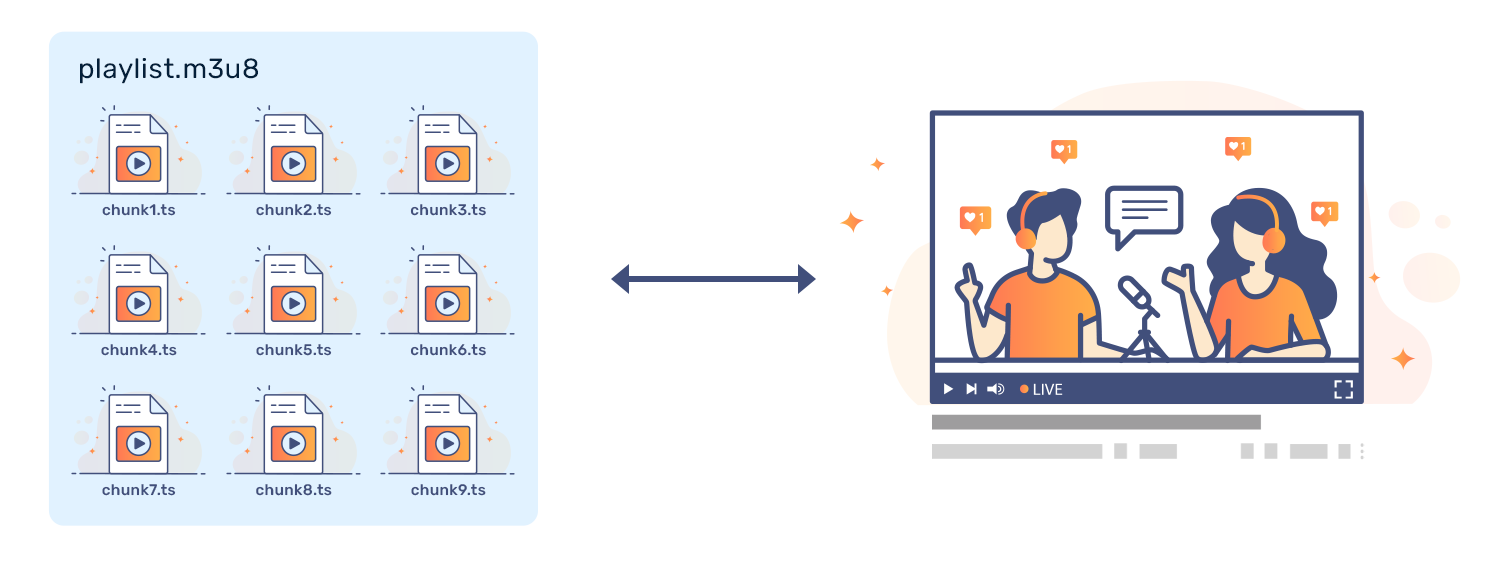

什么是DASH和HLS流?

-自適應流- HTTP) HLS(HTTP- Live-流) 兩種協議的工作方式相似——數據被編碼(分割)成塊并發送到客戶端進行查看。 一、HLS(HTTP直播) HLS(即HTTP Live

【KV260視覺入門套件試用體驗】 硬件加速之—使用PL加速FFT運算(Vivado)

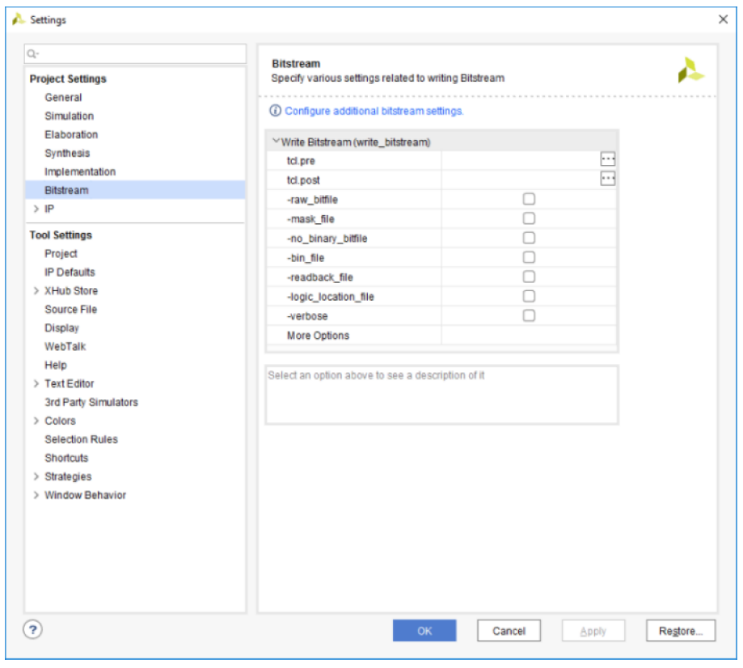

進行配置。

Vivado 工程

創建一個vivado工程,如下:

其中,HLS模塊的功能是將一個32位的無符號整數(ap_uint<32>)從AXI Lite接口讀入,并

發表于 10-02 22:03

HLS中RTL無法導出IP核是為什么?

請教一下,我在HLS里面要將以下程序生成IP核,C Synthesis已經做好了,但是在export RTL的時候一直在運行

int sum_single(int A int B

發表于 09-28 06:03

如何創建Vivado HLS項目

如何創建Vivado HLS項目

評論