簡介

在先進工藝節點中,無源器件和互連結構的電磁仿真對IC設計人員來說是一個巨大的挑戰。而要解決這些挑戰,以下幾個技術是最常被探討的:一個整合的設計環境,使電磁仿真工具能夠無縫接入現有的設計平臺中;在設計階段中實現快速無源器件建模和合成;在簽核sign-off 階段實現精確驗證,同時能把封裝的影響考慮進來。

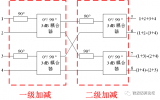

在本文中,演示了IRIS-HFSS整合流程,它無縫地集成在Cadence Virtuoso平臺中(如圖1所示)。在設計階段,IRIS和iModeler采用加速矩量法(MOM)引擎和人工神經網絡(ANN)技術,實現了快速無源器件仿真和合成;在簽核階段,把HFSS集成進來實現精確驗證以及芯片封裝聯合仿真。

Figure1 Combined IRIS-HFSS flow for IC designers

集成在Virtuoso中的IRIS

IRIS為IC設計人員提供了一種在主流設計環境中運行復雜的3D EM分析的簡單方法。IRIS基于加速矩量法(MoM)的全波電磁求解器引擎已在多個先進工藝節點上驗證了其準確性。Virtuoso無縫集成的形式避免了在設計環境和仿真環境之間轉換時可能出現的各種問題,使得IC設計人員可以采用自動化的方式實現EM分析。

Figure2 Virtuoso-integrated IRIS interface

支持先進工藝節點

先進工藝節點對EM精確仿真提出了巨大挑戰。先進工藝中線寬和線距的變化對金屬電阻率(rho-table)和布局效應(bias-table)比較敏感,這對仿真精確度是至關重要的。舉例來說,如果不考慮bias-table效應,momcap的電容值可能被低估超過20%。IRIS支持晶圓廠工藝文件中定義的rho-table和bias-table,以實現無源器件的精確建模和仿真結果。

Figure3 Width-and-spacing effect on a momcap

IRIS-to-HFSS

IRIS-to-HFSS接口為IC設計人員提供了一種途徑,可以使用行業標準的HFSS來驗證他們的無源模型。通過自動化的IRIS-to-HFSS接口,可以簡化HFSS項目的建立,它不僅提供了IRIS內置的功能,如rho-table、bias-table和via defeaturing,而且還提供了HFSS的一些相關特性,如自動薄層合并、端口定義和Q3D去嵌等。通過在HFSS 3D Layout中導出,還可以實現芯片與封裝的協同仿真。IRIS-HFSS流程已通過多個晶圓廠工藝節點認證。

Figure4 IRIS-to-HFSS interface

結論

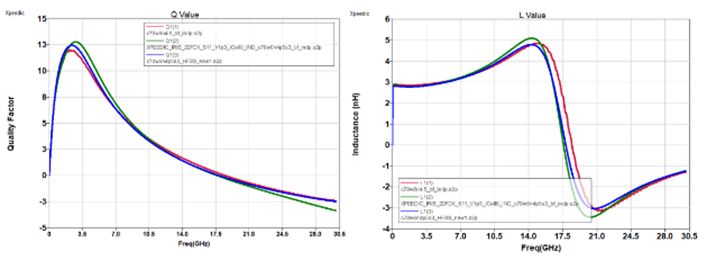

本文演示了IRIS-HFSS整合流程,此流程涵蓋了高級工藝節點上的設計和驗證的整個過程, 它可以顯著縮短IC設計人員的設計周期。

Figure5 IRIS,HFSS and Measurement Correlation

-

神經網絡

+關注

關注

42文章

4765瀏覽量

100556 -

無源器件

+關注

關注

5文章

193瀏覽量

23549

原文標題:IRIS-HFSS整合流程 實現先進工藝節點下的無源建模及驗證

文章出處:【微信號:Xpeedic,微信公眾號:Xpeedic】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Saber軟件功率MOSFET自建模與仿真驗證

專題:光無源器件介紹和種類

什么是光無源器件CCWDM?

業界領先的半導體器件SPICE建模平臺介紹

ADC與DAC工藝節點案例分析

Ansoft HFSS設計流程及應用

一種無源OLED顯示器供電設計

怎樣在先進工藝節點下實現無源器件的精確建模及仿真?

2018TowerJazz全球技術研討會美國站的活動,芯禾科技現場將帶來多項技術演示

IRIS-HFSS整合流程的演示

一種用于先進工藝節點中的無源器件建模和驗證的IRIS-HFSS整合流程

一種用于先進工藝節點中的無源器件建模和驗證的IRIS-HFSS整合流程

評論