聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學習之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

賽靈思

+關注

關注

32文章

1794瀏覽量

131162 -

IP

+關注

關注

5文章

1647瀏覽量

149327 -

Vivado

+關注

關注

19文章

808瀏覽量

66321

發(fā)布評論請先 登錄

相關推薦

AMD Vivado Design Suite 2024.2全新推出

AMD Vivado Design Suite 2024.2 全新推出,使用 AMD Versal Adaptive SoC 進行設計的重大改進。此版本為 AMD Versal 自適應 SoC

vivado導入舊版本的項目,IP核心被鎖。

vivado導入其他版本的項目的時候,IP核被鎖,無法解開,請問該如何解決。

使用軟件:vivado 2019.2

導入項目使用版本:vivado 2018

發(fā)表于 11-08 21:29

Vivado中FFT IP核的使用教程

本文介紹了Vidado中FFT IP核的使用,具體內(nèi)容為:調(diào)用IP核>>配置界面介紹>>IP核端口介紹>>MATLAB生成測試數(shù)據(jù)>>測試verilogHDL>>TestBench仿真>>結(jié)果驗證>>FFT運算。

Vivado使用小技巧

有時我們對時序約束進行了一些調(diào)整,希望能夠快速看到對應的時序報告,而又不希望重新布局布線。這時,我們可以打開布線后的dcp,直接在Vivado Tcl Console里輸入更新后的時序約束。如果調(diào)整

邏輯和轉(zhuǎn)換器件在IP攝像頭中的應用

電子發(fā)燒友網(wǎng)站提供《邏輯和轉(zhuǎn)換器件在IP攝像頭中的應用.pdf》資料免費下載

發(fā)表于 08-30 11:13

?0次下載

如何在服務器上調(diào)試本地FPGA板卡

?》。

簡介

Vivado 可以在功能更強大的服務器上遠程運行,同時可以在本地PC上連接的 FPGA 板卡上進行開發(fā)調(diào)試。在此配置中,服務器和工作站必須安裝相同版本的

發(fā)表于 07-31 17:36

兩個PLC之間如何交互信號

在工業(yè)自動化系統(tǒng)中,PLC(Programmable Logic Controller,可編程邏輯控制器)是核心的控制設備。在許多復雜的應用場景中,需要兩個或多個PLC之間進行信號交互

keil中Logic Analyzer可以在硬件上在線調(diào)試,為什么把全局變量加入Logic Analyzer不顯示波形呢?

keil中Logic Analyzer可以在硬件上在線調(diào)試,按照說明文檔上調(diào)試,用的是SW模式,為什么把全局變量加入Logic

發(fā)表于 05-16 06:47

Cirrus Logic與英特爾和微軟在全新的PC參考設計上進行合作

Cirrus Logic 近日與英特爾和微軟在全新的PC參考設計上進行合作。該設計將采用Cirrus Logic的高性能音頻和電源技術(shù)以及英特爾即將推出的代碼為Lunar Lake的客戶端處理器。

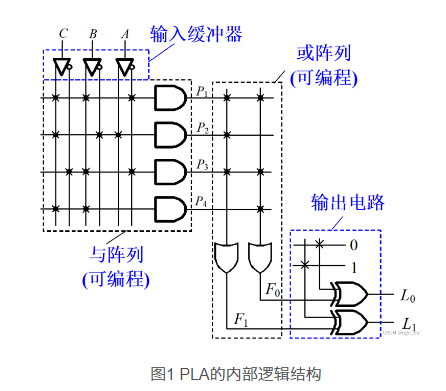

可編程邏輯陣列PLA內(nèi)部邏輯結(jié)構(gòu)示意

可編程邏輯陣列(Programmable Logic Array,PLA)和可編程陣列邏輯(Programmable Array Logic,PAL)都是數(shù)字

發(fā)表于 02-02 11:41

?2448次閱讀

如何禁止vivado自動生成 bufg

定和可靠。Vivado在編譯設計過程中會自動檢測到時鐘信號,并自動生成BUFG來緩沖時鐘。然而,在某些情況下,我們可能希望手動管理時鐘信號。 要禁止Vivado自動生成BUFG,可以按照以下步驟進行

如何用內(nèi)部邏輯分析儀調(diào)試FPGA?

1 推動FPGA調(diào)試技術(shù)改變的原因 進行硬件設計的功能調(diào)試時,F(xiàn)PGA的再編程能力是關鍵的優(yōu)點。CPLD和FPGA早期使用時,如果發(fā)現(xiàn)設計不能正常工作,工程師就使用“調(diào)試鉤”的方法。先

FPGA實現(xiàn)基于Vivado的BRAM IP核的使用

文章是基于Vivado的 2017.1的版本,其他版本都大同小異。 首先在Vivado界面的右側(cè)選擇IP Catalog 選項。

Vivado與ISE同時運行出現(xiàn)的奇怪現(xiàn)象

近幾天調(diào)試開發(fā)板,主芯片是XC7A100T,用Vivado給開發(fā)板下載bit文件,正常工作。

如何使用Vivado Logic Analyzer與邏輯調(diào)試IP進行交互

如何使用Vivado Logic Analyzer與邏輯調(diào)試IP進行交互

評論