DeePhi Tech是面向無人機,機器人,監(jiān)控攝像機和數(shù)據(jù)中心應用的FPGA深度學習平臺提供商.DeePhi平臺基于賽靈思所有可編程FPGA和SoC,提供靈活性,高性能,低延遲和低功耗 的理想組合。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

FPGA

+關注

關注

1620文章

21510瀏覽量

598978 -

賽靈思

+關注

關注

32文章

1794瀏覽量

130964 -

soc

+關注

關注

38文章

4021瀏覽量

217043 -

深度學習

+關注

關注

73文章

5422瀏覽量

120593

發(fā)布評論請先 登錄

相關推薦

可編程電源使用方法

可編程電源使用方法 可編程電源使用方法 摘要:本文詳細介紹了可編程電源的使用方法,包括其基本概念、主要功能、選擇原則、操作步驟、注意事項以及實際應用案例,旨在幫助讀者全面了解

可編程電源如何編程

可編程電源如何編程? 可編程電源是一種可以調節(jié)輸出電壓和電流的電源設備,廣泛應用于電子設備測試、研發(fā)和生產等領域。通過編程,用戶可以根據(jù)需要設置電源的輸出參數(shù),實現(xiàn)自動化測試和控制。本

給我一個FPGA,可以撬起所有顯示的接口和面板

FPGA開發(fā)了針對視頻領域的各種專用傳輸接口,針對8K應用的HDMI2.1,DP1.4等,我們利用FPGA可編程快速迭代的特點,最早給出解決方案,可以比競爭對手,或者ASIC方案,更快的推出新產品。”

當然,在未來,酆毅稱,

發(fā)表于 04-25 18:10

FPGA零基礎學習系列精選:半導體存儲器和可編程邏輯器件簡介

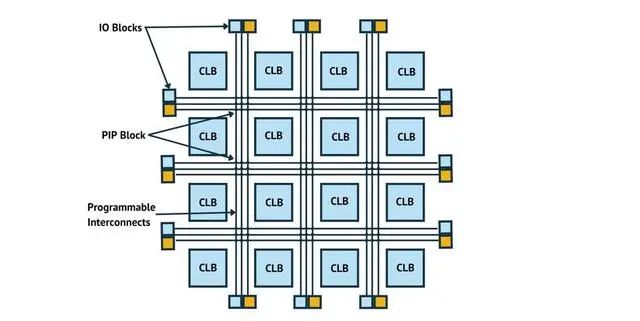

決定了PLD內部的互連關系和邏輯功能,改變這些數(shù)據(jù),也就改變了器件的邏輯功能。

下面我們介紹兩種常用的PLD器件:CPLD和FPGA;

CPLD:復雜可編程邏輯器件,CPLD主要由邏輯塊

發(fā)表于 03-28 17:41

現(xiàn)場可編程門陣列的原理和應用

FPGA是一種可編程的硬件邏輯器件,其核心組成部分是可編程邏輯單元(PLU)和可編程互連資源(Interconnect Resources)。PLU是一組

FPGA在深度學習應用中或將取代GPU

現(xiàn)場可編程門陣列 (FPGA) 解決了 GPU 在運行深度學習模型時面臨的許多問題

在過去的十年里,人工智能的再一次興起使顯卡行業(yè)受益匪淺。英偉達 (Nvidia) 和 AMD 等公

發(fā)表于 03-21 15:19

現(xiàn)場可編程門陣列設計流程

現(xiàn)場可編程門陣列(FPGA)設計流程是一個綜合性的過程,它涵蓋了從需求分析到最終實現(xiàn)的各個環(huán)節(jié)。下面將詳細介紹FPGA設計流程的主要步驟。

現(xiàn)場可編程門陣列是什么

現(xiàn)場可編程門陣列(Field Programmable Gate Array,簡稱FPGA)是一種超大規(guī)模可編程邏輯器件,由可編程邏輯資源、可編程

AMD停產CPLD和FPGA芯片,未來或棄用舊款FPGA

值得注意的是,FPGA(現(xiàn)場可編程門陣列)是一種專為某些特殊場景而設計的集成電路,能有效解決全定制電路的不足之處;CPLD(復雜可編程邏輯器件)則適合完成各類數(shù)學計算與組合邏輯任務。二者皆為賽

基于FPGA的可編程AES加解密IP

可編程AES加解密IP內建密鑰擴展功能,使用初始密鑰產生擴展密鑰,用于加解密過程。可編程AES加解密IP處理128-bit分組數(shù)據(jù),并且支持可編程的密鑰長度:128-bit,192-bit和256-bit。

發(fā)表于 01-09 10:49

?362次閱讀

簡單認識現(xiàn)場可編程門陣列

現(xiàn)場可編程門陣列 (Field Programmable Gate Array, FPGA)也稱為現(xiàn)場可編程器件,是在 PROM ( Programmable Read Only Memory

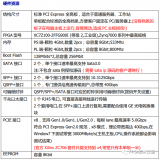

基于賽靈思所有可編程FPGA和SoC的DeePhi深度學習平臺介紹

基于賽靈思所有可編程FPGA和SoC的DeePhi深度學習平臺介紹

評論