Zynq? UltraScale+? MPSoC 器件不僅提供 64 位處理器可擴(kuò)展性,同時還將實時控制與軟硬件引擎相結(jié)合,支持圖形、視頻、波形與數(shù)據(jù)包處理。置于包含通用實時處理器和可編程邏輯的平臺上,三個不同變體包括雙應(yīng)用處理器 (CG) 器件、四核應(yīng)用處理器和 GPU (EG) 器件、以及視頻編解碼器 (EV) 器件, 為 5G 無線、下一代 ADAS 和工業(yè)物聯(lián)網(wǎng)創(chuàng)造了無限可能性。

該視頻顯示了Zynq?UltraScale+?MPSoC處理系統(tǒng)中硬化控制器的性能如何,LPDDR4以2.4Gbps運行48小時以上,在壓力下,具有低抖動和大量余量。

-

處理器

+關(guān)注

關(guān)注

68文章

19160瀏覽量

229121 -

賽靈思

+關(guān)注

關(guān)注

32文章

1794瀏覽量

131164 -

可編程邏輯

+關(guān)注

關(guān)注

7文章

514瀏覽量

44072

發(fā)布評論請先 登錄

相關(guān)推薦

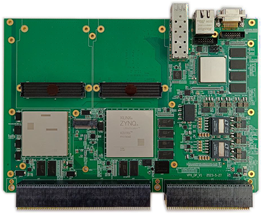

AMD/Xilinx Zynq? UltraScale+ ? MPSoC ZCU102 評估套件

基于PYNQ和機(jī)器學(xué)習(xí)探索MPSOC筆記

在米爾電子MPSOC實現(xiàn)12G SDI視頻采集H.265壓縮SGMII萬兆以太網(wǎng)推流

12G-SDI高清視頻開發(fā)案例,讓4K視頻采集更便捷!基于Xilinx MPSoC高性能平臺

在米爾電子MPSOC實現(xiàn)12G SDI視頻采集H.265壓縮SGMII萬兆以太網(wǎng)推流

為Xilinx? Zynq?UltraScale?系列多處理器中的VCCINT_VCU軌供電

使用TPS65086x PMIC為Xilinx Zynq UltraScale MPSoC供電

一個更適合工程師和研究僧的FPGA提升課程

KU115+ZU19EG+DSP6678的雙FMC 6U VPX處理板

AMD推出全新Spartan UltraScale+ FPGA系列

在FPGA上為FPGA設(shè)計PCB的步驟詳解

采用UltraScale/UltraScale+芯片的DFX設(shè)計注意事項

針對UltraScale/UltraScale+芯片DFX應(yīng)考慮的因素有哪些(2)

針對UltraScale/UltraScale+芯片DFX應(yīng)考慮的因素有哪些(1)

Zynq UltraScale+ MPSoC LPDDR器件中硬化控制器的性能介紹

Zynq UltraScale+ MPSoC LPDDR器件中硬化控制器的性能介紹

評論