在電機驅動的FOC控制開發過程中,您是否遇到過電機噪聲過大、效率偏低甚至無法運轉的情況?這一切有可能源于相電流的采樣異常,從而導致FOC算法中無法重建正確的三相電流!小編這里給大家分析影響電流采樣的一個因素——延遲源!1

引言

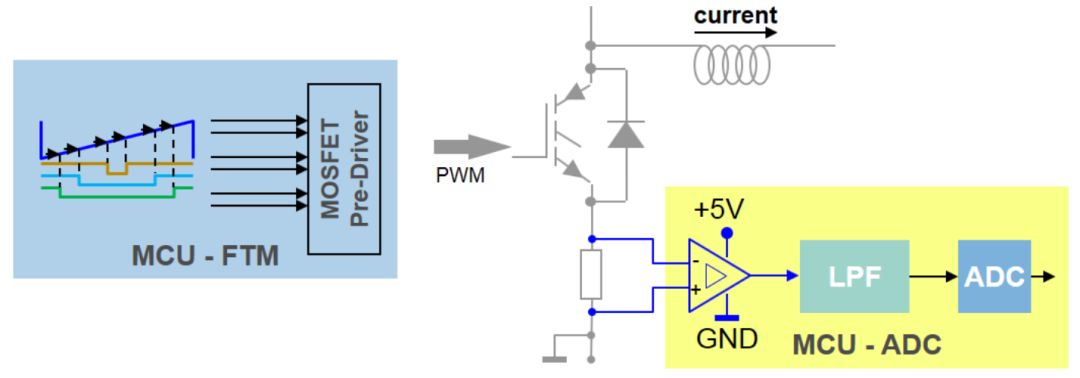

在雙電阻采樣的電機驅動FOC控制中,采樣點設置為驅動橋下管打開的中間時刻。注意,這里是驅動橋下管打開的中間時刻,而不是MCU輸出的PWM周期中間時刻。因為從MCU計算生成PWM到電流信號送入MCU的ADC模塊,這個典型的驅動拓撲中,存在多達七個延遲源!

2

延遲類型及典型時間

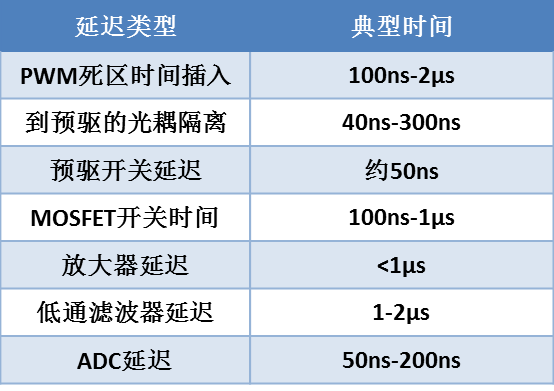

下面表格詳細指明了電機驅動系統拓撲中存在的七個延遲源及其典型的時間。這些延遲將疊加在一起,產生的影響是:實際輸出PWM波形滯后于MCU計算預期輸出的PWM波形,按照這個計算,相電流采樣點需要滯后于MCU計算預期輸出的PWM波形的中間時刻。

3

延遲源詳細分析

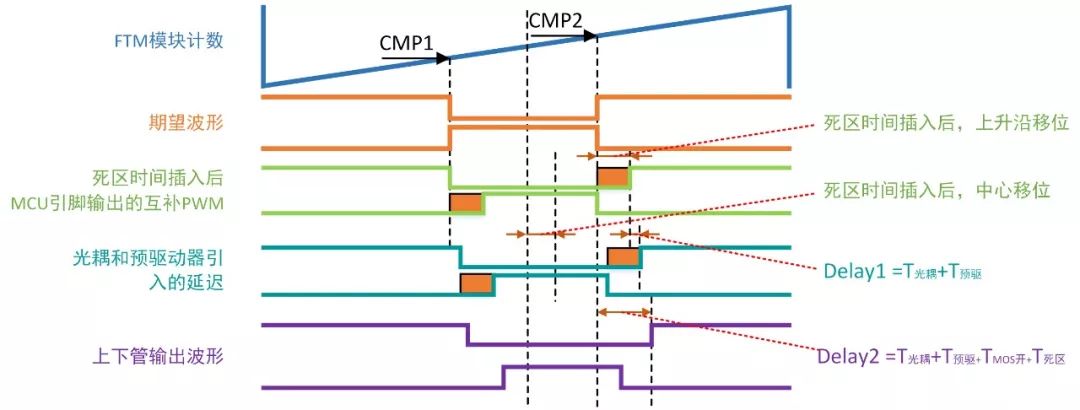

3.1PWM死區時間插入

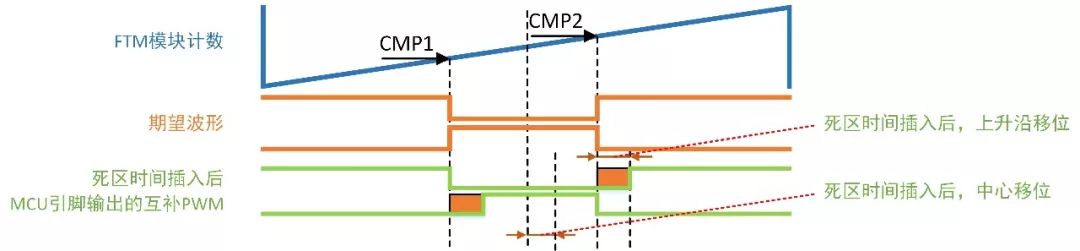

在三相無刷電機驅動系統中,需要三個橋臂來控制相線電流流向,在每個橋臂上有兩個功率器件,如MOSFET、IGBT。這一對功率器件不能同時導通,否則就會出現短路的情況。這里以MOSFET作為功率器件來說明。在控制中,必須插入死區時間以確保上部和下部MOSFET不會同時處于打開狀態。死區時間的典型值可能在100ns到2μs之間,具體取決于系統中的各種因素,如MOSFET驅動電壓、MOSFET型號。

在所需的PWM波形插入死區時間之后,我們得到的是PWM中點和上升沿都向右移動。因此,在FOC控制算法計算出適當的PWM之后,我們立即開始看到第一個延遲,即死區時間。

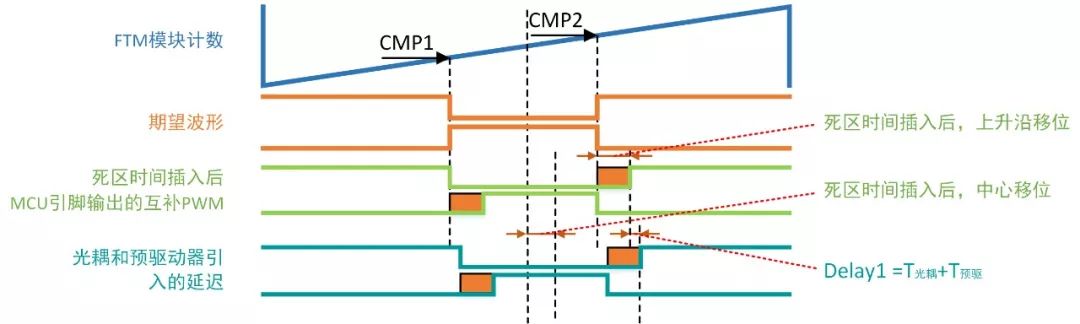

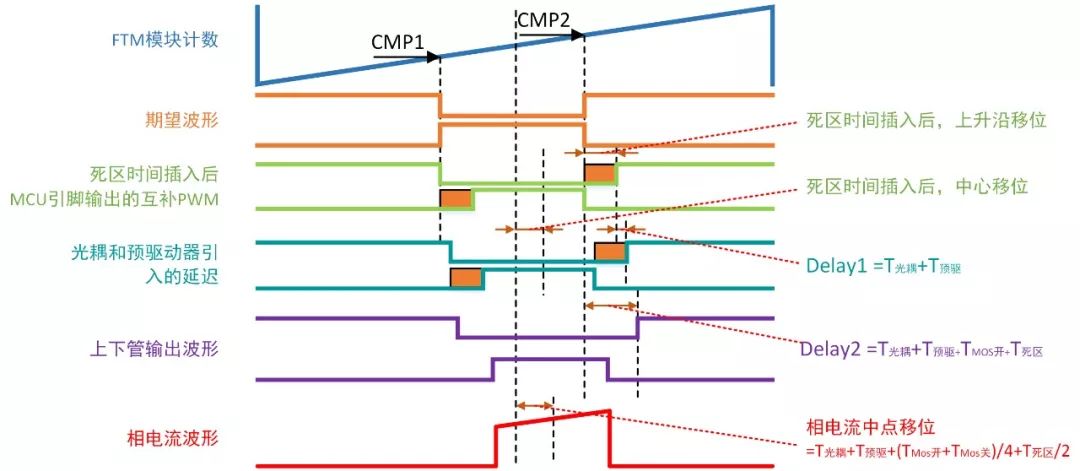

在MCU控制FTM模塊輸出PWM波形到MOSFET柵極受控制的那一刻之間,各種光電耦合器和預驅動器的信號響應導致了額外的延遲。

與MCU引腳輸出的波形相比,預驅動器的輸出延遲了一段時間(Delay1)。

3.3晶體管開關延遲

經過預驅動器后,PWM波形到達MOSFET晶體管,但由于其固有特性,所有晶體管都需要一定的時間導通和截止。根據晶體管類別及導通/截止之間切換所需要的電壓電平,此延遲時間有所不同。

Delay2為相線電壓理論切換點(CMP2)與實際切換點的時刻之間的整個延遲。

最后,柵極電壓到達了能令晶體管導通的程度,電流通過相線和采樣電阻,在采樣電阻兩端產生電壓差,紅色波形為理想狀態下的相電流波形。此時與MCU計算生成的PWM周期中點存在延遲總時間如圖中“相電流中點移位”。

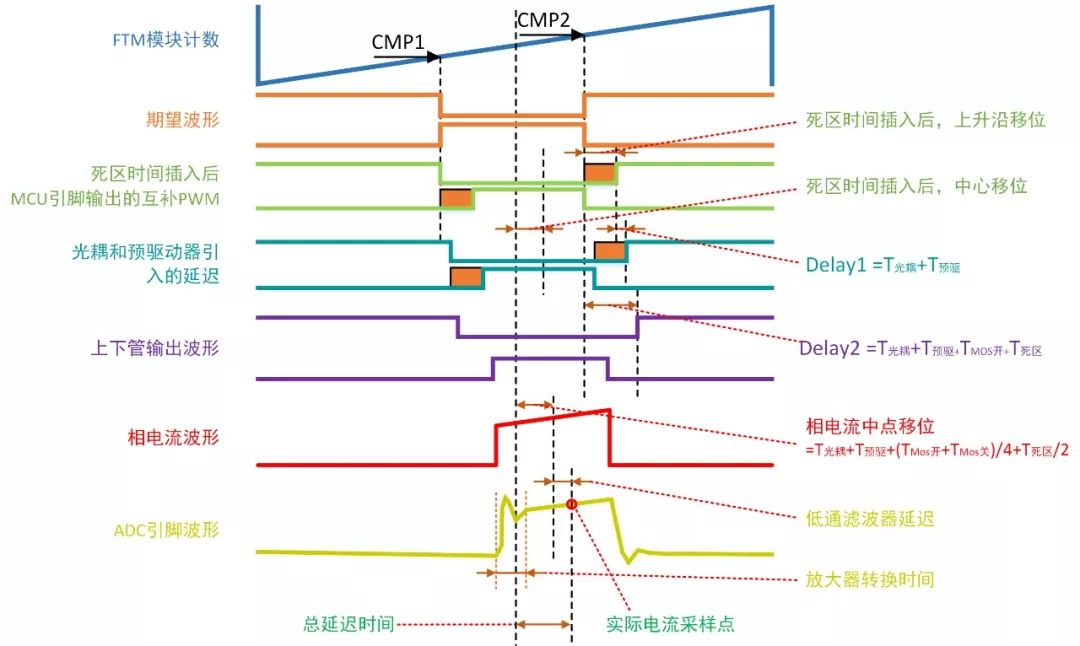

3.4其他延遲

如下圖所示,影響電流采樣的最后延遲鏈是由放大器轉換速率、MCU引腳上的低通濾波器和ADC轉換速率構成的。圖中用紅色圓圈標記的時刻為正確的電流采樣時刻,可以看出,與FTM輸出的PWM中點相比,相電流采樣點大大延遲。

4

結語

所有的電子電路中,都會存在信號的延遲問題。信號延遲不可能被完全消除,但可通過選用低延遲的器件以減小影響。

在電機驅動中,除了選用合適的器件外,還需要對信號延遲進行軟件補償。文中提及的這些延遲源的精確延遲時間,我們可以通過示波器和計算得出,在軟件上補償這些延遲,才可得出正確的電流采樣時刻。這樣在正確的時刻采集到的數據才能作為FOC控制中重建電機三相電流的數據來源。

-

PWM

+關注

關注

114文章

5056瀏覽量

212166 -

電機驅動

+關注

關注

60文章

1163瀏覽量

86281

原文標題:FOC電流采樣為什么不準?你忽略了這個細節

文章出處:【微信號:Zlgmcu7890,微信公眾號:周立功單片機】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

影響電流采樣的一個因素——延遲源!

影響電流采樣的一個因素——延遲源!

評論