眾所周知,SDRAM從開始工作伊始,一直伴隨著64ms刷新一遍的最基本規定(假設該SDRAM有4096行,那么必須大約15us的時間就要發出一次自刷新命令),這是為了保持SDRAM內數據能夠在上電以后一直保持的原因,具體原因就不多解釋了,我們還是以實際操作為主。

正常情況下,我們要不斷地對SDRAM進行讀或者寫操作,這樣才能實現fpga和SDRAM之間的數據交流傳遞。假如我們在進行寫操作時,15us的時間計時已經到了,發出了自刷新使能信號,這時候難道我們要打斷寫操作嗎?顯然這是不文明的野蠻的,理想的操作就是等待本次的寫操作完成,SDRAM的內部狀態機進入到了休閑狀態,這時候才正式發出自刷新命令。

可能大家會認為這樣實際經過的時間是超過15us的,假如4096次每次都是超過15us的話,那么總時間豈不是超過64ms了,現在想起來感覺當初自己的問題真傻。因為實際上每發出一次刷新命令的周期是64ms/4096=15.625us,當初設置15us為周期就已經考慮到了這個余量,而一個寫周期(假如突發長度=4)本身的時間遠遠小于0.625us,所以這樣設計是合理的。

但是,如果突發寫長度是全頁的話,要考慮SDRAM的工作頻率、突發長度重新計算這個寫周期時間,那么設置15us的計時時間是有問題的,應該調的更小一點。

總結:自刷新要保證64ms內一遍,合理設置自刷新周期計時器,考慮讀寫一個周期所花的時間,使得在發出自刷新信號的時候,等待本次正在進行的讀寫周期完成后,再寫入自刷新命令。

以上內容是我如何對自刷新操作和讀寫操作進行合理安排的一種解決方案,后來細想其實可以更加的合理,微調后的方案::15us的定時計數器不斷地進行,沒計到15us發出刷新請求信號,同時計數器重新計數(上個方案是等到正式發出刷新命令以后才開始重新計數),本次微調的技巧應該更加理想些(因為讀寫周期即使是全頁的,也就是10us以內完全在15us的范圍以內)。

-

SDRAM

+關注

關注

7文章

420瀏覽量

55047 -

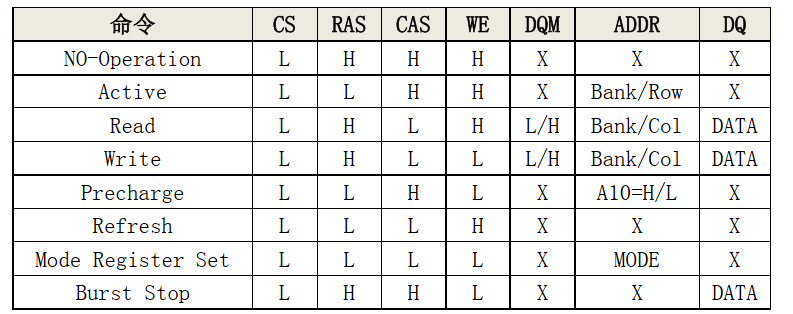

命令

+關注

關注

5文章

658瀏覽量

21928

原文標題:如何操作SDRAM的自刷新命令而不影響正常讀寫操作?

文章出處:【微信號:FPGAer_Club,微信公眾號:FPGAer俱樂部】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

如何操作SDRAM的自刷新命令

如何操作SDRAM的自刷新命令

評論