Vivado HLS的輸入可以是C、C++或者System C,從而繼承了這些語(yǔ)言本身就具有的數(shù)據(jù)類(lèi)型,例如char、short int、int等整型或float、double等浮點(diǎn)數(shù)據(jù)類(lèi)型。不難發(fā)現(xiàn),對(duì)于整型,其表示的字長(zhǎng)是以8為邊界的,這實(shí)際上和真實(shí)的硬件模型不完全匹配。這一點(diǎn)也不難理解,例如HDL中會(huì)根據(jù)設(shè)計(jì)需求設(shè)定位寬,而這些位寬很多情形下并不是8-bit、16-bit或者32-bit。因此,HLS引入了任意精度(ArbitraryPrecision)的數(shù)據(jù)類(lèi)型(對(duì)于SystemC,可查看Table 1-7, ug902)。以C++為例說(shuō)明。

整數(shù)

1

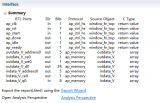

對(duì)于任意精度整型數(shù)據(jù)類(lèi)型,可通過(guò)ap_int

定點(diǎn)數(shù)

2

對(duì)于任意精度的定點(diǎn)小數(shù),可通過(guò)ap_fixed

浮點(diǎn)數(shù)

3

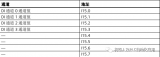

對(duì)于浮點(diǎn)數(shù)據(jù)類(lèi)型,除了float和double之外,Vivado HLS還引入了半精度浮點(diǎn)數(shù)half,需要添加頭文件hls_half.h。該浮點(diǎn)數(shù)據(jù)類(lèi)型為16-bit。

技巧

多種數(shù)據(jù)類(lèi)型給用戶提供了更多的選擇,用戶可根據(jù)實(shí)際需求選擇可最佳匹配于硬件的數(shù)據(jù)類(lèi)型。一個(gè)小的技巧是,把數(shù)據(jù)類(lèi)型通過(guò)typedef定義在用戶的頭文件中。此外,在仿真時(shí)可采用float或double類(lèi)型,以防止數(shù)據(jù)溢出,盡快完成算法功能的驗(yàn)證;之后再將設(shè)定為整型,觀察是否有溢出,完成C綜合。

結(jié)論

任意精度的數(shù)據(jù)類(lèi)型可以完美地匹配硬件需求,同時(shí)還繼承了原有數(shù)據(jù)類(lèi)型所允許的操作。例如,對(duì)于兩個(gè)13-bit的有符號(hào)整數(shù)相乘,不必把其定義為int類(lèi)型,而是直接定義為ap_int<13>,且可直接使用乘法運(yùn)算符。這樣做的最大好處就是更準(zhǔn)確地獲取資源利用率信息。注意在使用任意精度數(shù)據(jù)類(lèi)型時(shí)要添加相應(yīng)的頭文件。

-

C++

+關(guān)注

關(guān)注

22文章

2104瀏覽量

73503 -

數(shù)據(jù)類(lèi)型

+關(guān)注

關(guān)注

0文章

236瀏覽量

13610 -

HLS

+關(guān)注

關(guān)注

1文章

128瀏覽量

24043

原文標(biāo)題:一篇文章看懂HLS中的數(shù)據(jù)類(lèi)型

文章出處:【微信號(hào):Lauren_FPGA,微信公眾號(hào):FPGA技術(shù)驛站】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

GaussDB 數(shù)據(jù)類(lèi)型介紹

如何利用Vivado HLS處理許多位準(zhǔn)確或任意精度數(shù)據(jù)類(lèi)型

HLS系列– HLS中的數(shù)據(jù)類(lèi)型1

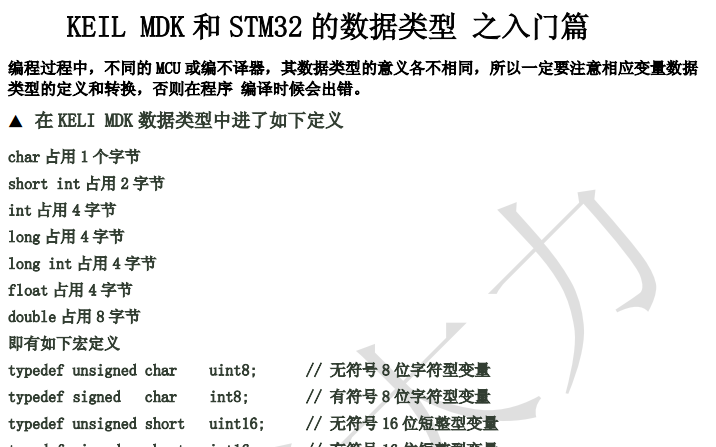

51單片機(jī)中的數(shù)據(jù)類(lèi)型解析

vhdl數(shù)據(jù)類(lèi)型

KEIL-MDK和STM32的數(shù)據(jù)類(lèi)型-之入門(mén)篇pdf資料下載

重視變量的數(shù)據(jù)類(lèi)型

Struct結(jié)構(gòu)數(shù)據(jù)類(lèi)型

結(jié)構(gòu)數(shù)據(jù)類(lèi)型(Struct)及應(yīng)用案例

什么是數(shù)據(jù)類(lèi)型轉(zhuǎn)換

定義數(shù)據(jù)類(lèi)型

ARRAY 數(shù)據(jù)類(lèi)型的變量

F型PLC數(shù)據(jù)類(lèi)型與標(biāo)準(zhǔn)PLC數(shù)據(jù)類(lèi)型(UDT)之間的差別在哪?

一篇文章看懂HLS中的數(shù)據(jù)類(lèi)型

一篇文章看懂HLS中的數(shù)據(jù)類(lèi)型

評(píng)論