FPGA的設計就是將自己想要實現的邏輯通過計算機能夠理解的語言描述出來,并讓計算機根據FPGA內部的資源生成可以進行資源配置并在加電以后能夠執行的過程。

人的邏輯和計算機之間的橋梁就是HDL - 硬件描述語言,目前有兩個比較流行的語言Verilog和VHDL,其中Verilog用的更多,在我們的小腳丫FPGA平臺上也選用了Verilog。

語言就是一個工具,不同的語言只是語法、規則不同而已,稍加了解這些語法、規則應該就可以方便地切換到不同語言上。因此在FPGA設計時,無論是Verilog、VHDL還是其它更高級的語言,這都不是FPGA的實質,我們在使用的時候也沒有必要糾結用的是何種語言。

很多做FPGA設計的工程師都買過某著名教授的Verilog的教程,非常厚,但普遍反應看不懂,從頭到尾看了好幾遍,仍然不會做FPGA設計。

我翻看過基本英文版的FPGA設計的教程,沒有一本是專門講Verilog的語言的,多數是將Verilog的語法和規則作為附錄放在書的后面供查閱。

因為Verilog實在太簡單,所有的語法和規則匯總起來也就兩個頁面,對于學習FPGA的初學者來講了解這些已經足夠,更重要的是在實際的項目中通過具體的使用和調試來深刻掌握。

Verilog看起來跟C++比較像,但由于它是一門用于描述硬件的語言,因此它跟MCU上運行的程序不同,它有一些跟硬件高度相關的特性需要格外注意。如果把FPGA的邏輯用MCU程序的思路去寫,那就大錯特錯了。

下面是我們www.stepfpga.com的Wiki系統里對Verilog的簡要介紹(詳細的語法和規則可以點擊左下角的“閱讀原文”指向的頁面):

Verilog 是 Verilog HDL 的簡稱,Verilog HDL 是一種硬件描述語言(HDL:Hardware Description Language),硬件描述語言是電子系統硬件行為描述、結構描述、數據流描述的語言。利用這種語言,數字電路系統的設計可以從頂層到底層(從抽象到具體)逐層描述自己的設計思想,用一系列分層次的模塊來表示極其復雜的數字系統。然后,利用電子設計自動化(EDA)工具,逐層進行仿真驗證,再把其中需要變為實際電路的模塊組合,經過自動綜合工具轉換到門級電路網表。接下去,再用專用集成電路 ASIC 或現場可編程門陣列 FPGA 自動布局布線工具,把網表轉換為要實現的具體電路布線結構。

在 FPGA 的設計中,我們有多種設計方式,如繪制原理圖、編寫描述語言代碼等。早期的工程師對原理圖的設計方式情有獨鐘,這種輸入方式能夠很直觀的看出電路的結構并快速理解電路。隨著邏輯規模的不斷攀升,邏輯電路也越來越復雜,這種輸入方式就會顯得力不從心,應付簡單的邏輯電路還算實用,應付起復雜的邏輯電路就不行了。因此取而代之的便是編寫描述語言代碼的方式,現今的絕大多數設計都是采用代碼來完成的。

簡單地講在Verilog編程中需要注意以下幾點:

所有的Verilog程序都以Module(模塊、組件)的方式存在,一個簡單的邏輯可以由一個Module組成,復雜的邏輯可以包含多個Modules,每個Module有獨立的功能,并由輸入、輸出端口被其它module調用。通過Module的方式可以將一些比較獨立、可以復用的功能進行模塊化,代碼閱讀起來也比較直觀;

Verilog的信號分為wire和register兩種類型,wire可以看成直接的連接,而register具有對某一個時間點狀態進行保持的功能,因此在設計邏輯的時候要明確定義每個信號是wire還是reg屬性;

并行執行:Verilog描述的主要是硬件而不是軟件,因此也就意味著其描述的各個功能之間可以并行執行,比如在你的設計中你有3個計數器,每一個計數器都連接到不同的時鐘上,這是沒有問題的,每一個時鐘都干自己的事。不像MCU,只有一個線程按照順序執行。

由于篇幅所限,我們就不對這個語言的具體語法、規則進行展開,在此借用Stanford大學的Paul Hartke教授的Verilog課程的PPT頁面來對Verilog的語法和規則做個簡單的介紹(正好可以借此提升一下自己的專業英語閱讀能力),可以看到斯坦福大學的學生學習Verilog也就十幾個頁面的內容。

使用Verilog設計FPGA的流程

Module是Verilog最基本構成方式

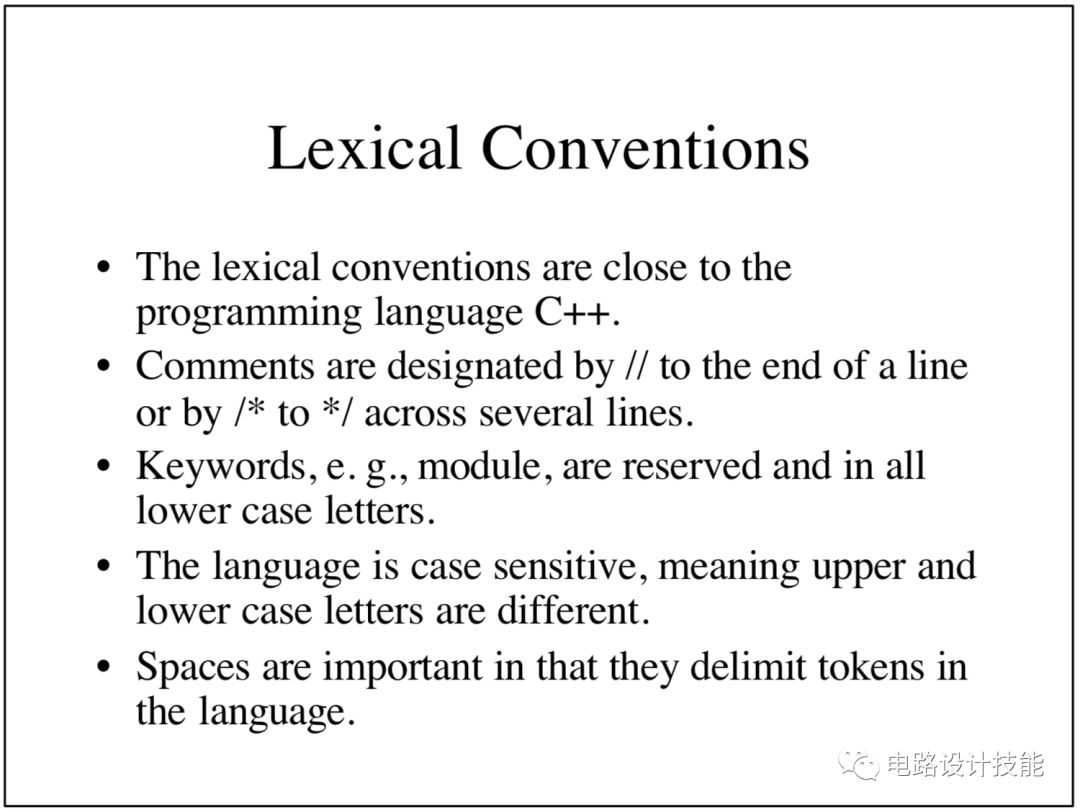

Verilog的語法規定跟C++比較接近

數值規范

按位/邏輯操作符

混合操作符

一元減數操作符(教授說它從來沒有在實際的應用中看到過、用過)

連續賦值

過程賦值

if-else條件過程賦值

邏輯操作符

關系操作符

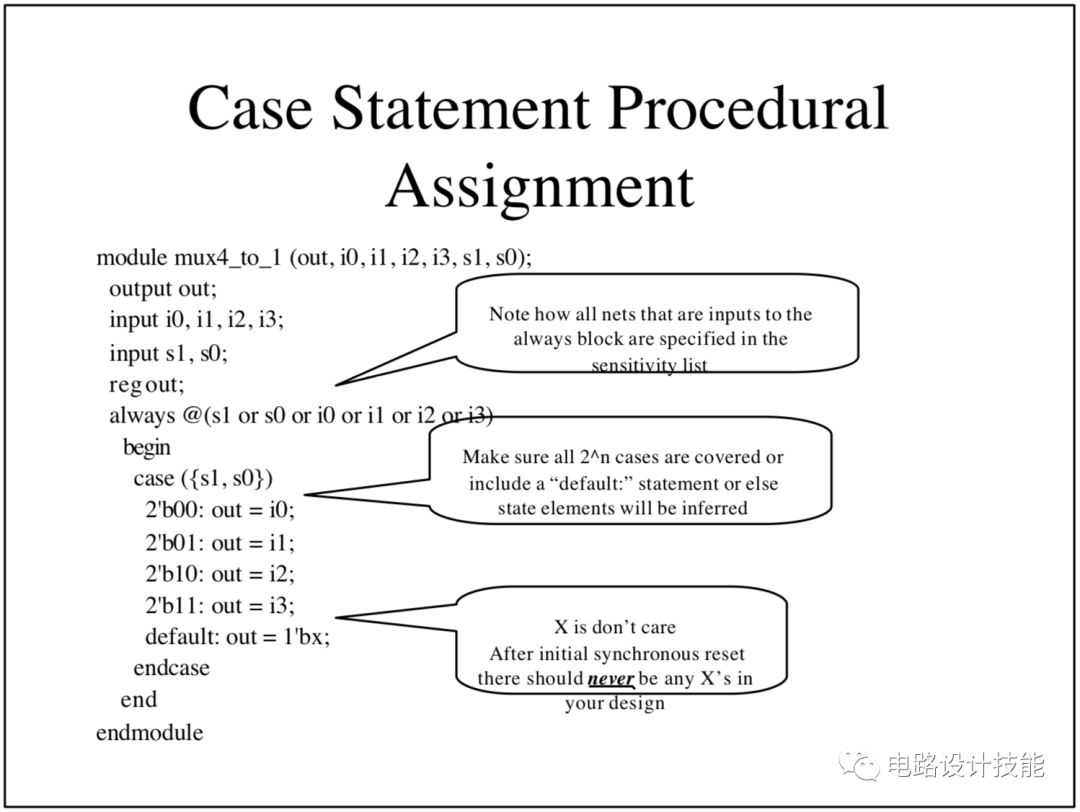

Case Statement過程賦值

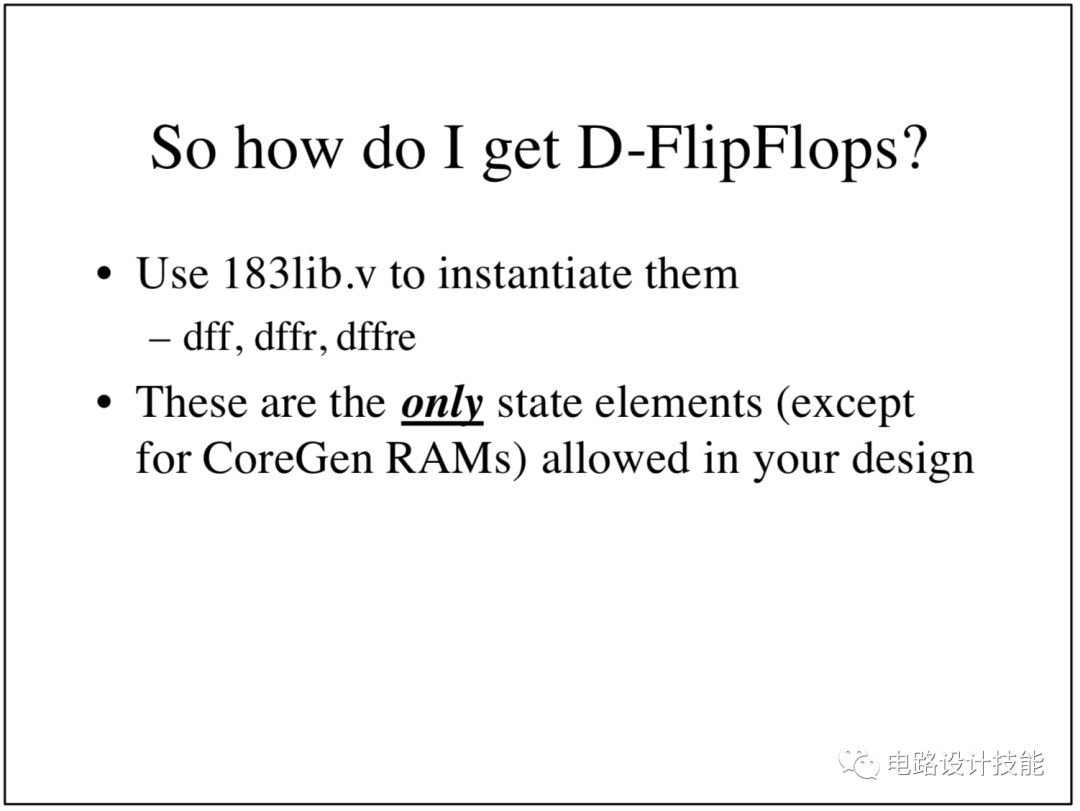

如何得到一個D觸發器?

在有限狀態機(FSM)中使用Case Statement

-

FPGA

+關注

關注

1626文章

21667瀏覽量

601858 -

Verilog

+關注

關注

28文章

1343瀏覽量

109986 -

編程

+關注

關注

88文章

3592瀏覽量

93596

原文標題:Verilog編程的要點

文章出處:【微信號:xiaojiaoyafpga,微信公眾號:電子森林】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

【信盈達】C語言知識點的總結

《Verilog HDL數字系統設計教程》(第四版)學習筆記 part1 Verilog數字設計基礎——第一章知識點總結

Verilog編程語言界面入門知識簡介

使用C語言進行單片機編程的基本知識點和編程規范資料總結

Verilog是編程語言嗎

開關電源模塊知識點總結

Verilog設計過程中的一些經驗與知識點

Verilog系統函數和邊沿檢測

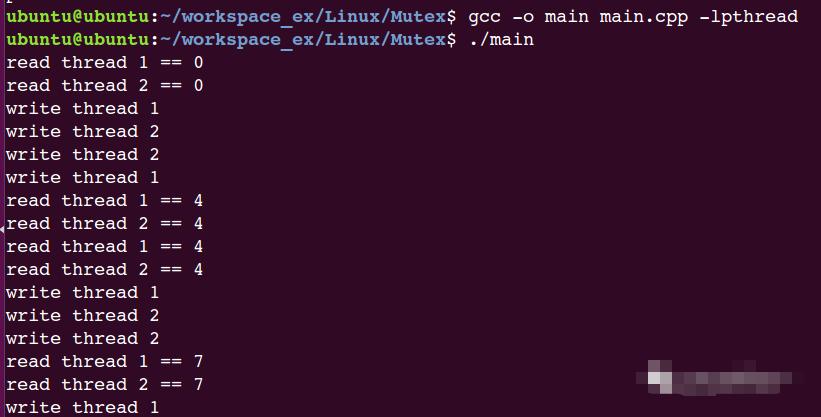

Linux中多線程編程的知識點

Verilog如何編程?Verilog編程知識點總結

Verilog如何編程?Verilog編程知識點總結

評論