比如覆銅間距16mil,其他安全間距8mil,過孔到過孔間距100mil,焊盤到過孔間距100mil,頂層地覆銅0.8mm,頂層VCC3.3與VCC1.8覆銅間距0.5mm等。

Altium Designer的間距規則默認為一個1Omil間距,沒有區分焊盤到焊盤,過孔至撾孔,走線到覆銅等的間距,想要高級規則,必須自己建立。

在PCB設訛不境下Design>Rules>Elecvical>Clearance,同樣右鍵新建一個間距規則并重命名為Poly, Where The First Object Matche選Adcanced (Query), Full Query輸入in polygpon, Constraints 把默認的1Omil修改為2Omil,優先級 Poly 比默認的Clearance 的10mil高,這2個間距規則共同構成覆銅間距為20mil,其他間距,例如走線到走線,走線到焊盤過孔間距為10mil的規則,如下圖:

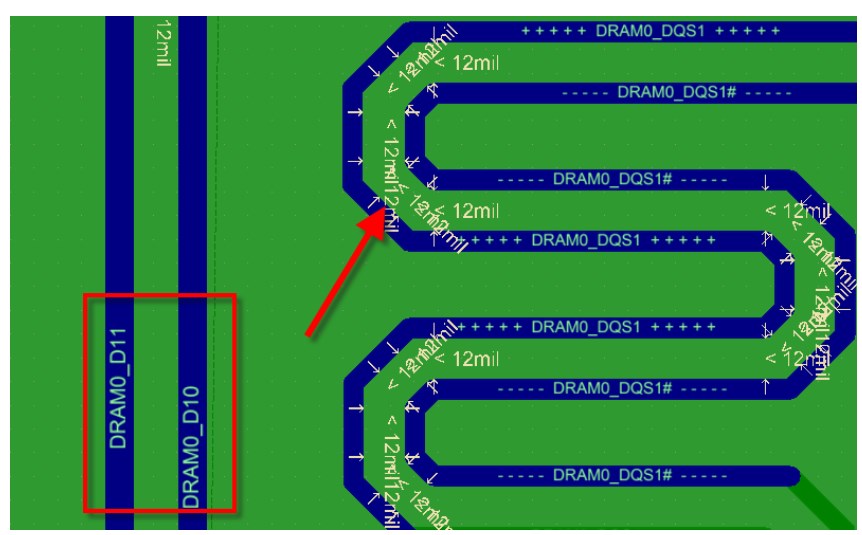

下2圖是過孔覆銅全連接?viaconnect,默認安全間距clearance?8mil,覆銅間距16mil?規則的覆銅,inpolygon是所有的覆銅,如果想要其他覆銅間距,則需要在新建覆銅規則,比如VCC3.3?覆銅0.5mm,VCC1.8?覆銅間距0.6mm,其他覆銅0.4mm;優先級16mil的最低;覆一片銅到VCC3.3網絡同時起名該覆銅為VCC3.3-ALL;?覆一片銅到VCC1.8網絡同時起名該覆銅為VCC1.8-ALL;同樣要興建間距規則,見下面第3-6張圖:

下圖是過孔到過子幽間距規則, Where The First Object Matches Where The Second Object Match的Full Query,只有這2個參數一個是is via,另一個是is pad即可;如果一個是is pad另一個是isvia,那就是過孔到焊盤的間距;如果一個是is pad另一個是is pad,那就his焊盤到焊盤的間距;隨后填入具體的數據就可以了。Where The Second Object Match的默認是All,修改它就是第一個和第二個間距規則,is via和All就是via到其他的間距規則,is via 和is via 就是過孔到過孔的間距規則。

過孔到過孔間距沒有到2.54mm的在線DRC檢查出來綠色顯示;

注:設置小間距管腳間距:一些FPGA芯片等很多焊盤間距多達到了0.2mm,默認的10mil(0.254mm)間距顯然是沖突的,上述問題可以通過HasFootprint('PQ208')或IsPad?and?InComponent('U1');?(IsPad?and?InComponent('JP4'))?or(IsPad?and?InComponent('JP3'))?HasFootprint('PQ208'),封裝為PQ208的元件;sPad?and?InComponent('U1'),元件U1的管腳間的間距;

如果你想了解更全面的pcb規則設置,

可查看我們的實戰124講視頻

上面2個規則只是管腳間距,從上面拉出來的線的間距是其他的規則值.當然不能太大:比如上面的P0208 焊盤0.3mm. 焊盤間距 0.2mm.布線0.2mm。那拉出來的間距就是0.4mm,如果把布線的間距設置為0.5mm,1mm,要么拉布出來。要么綠色。

{IsPad?and?InComponent('JP4')} Or{IsPad?and?InComponent('JP3')}元件JP3, JP4的間距規則:見下面3張圖:

下圖是一個定位孔間距為3mm的間距規則:常用一個內孔=等于外孔的焊盤做定位孔。該孔不連接到任何網絡(不進行電氣連接),只擰螺絲用。我們在PCB上4個腳上放4個定位孔不連接到任何網絡,焊盤名稱起為HOLE,內孔=外孔大小;free-hole含義free不連接到任何網絡,Hole焊盤名稱;可以是free-0,fret-1, free-2等等;

下圖為一個在toplaye層覆銅名為SVANA 的間距規則,當然Toplayer可以換成其他層,SVANA可以換成其他覆銅的名稱:

下圖為DM到DP網絡間距為20mil的間距規則:

下圖為MSCLKI網絡到其他間距為16mil的間距規則;

-

pcb

+關注

關注

4317文章

23002瀏覽量

396234 -

AD

+關注

關注

27文章

868瀏覽量

150166

原文標題:PCB規則 —— AD高級間距規則

文章出處:【微信號:FANYPCB,微信公眾號:凡億PCB】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

AD_PCB高級規則 altium designer pcb advance rule

Altium Designer高級規則語法參考PCB查詢功能的詳細資料說明

PCB設計之電氣(Electrical)規則設置

PCB規則之AD高級間距規則

PCB規則之AD高級間距規則

評論