1.引言

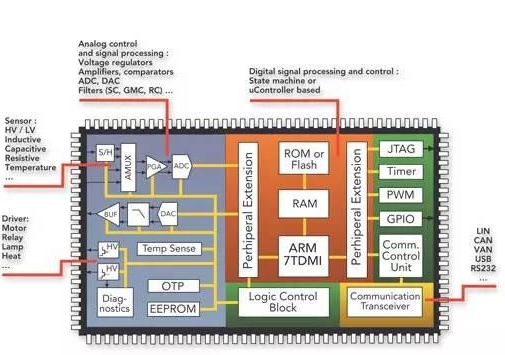

集成電路相關技術作為最具發展前景的技術,已經成為世界最具發展前景的高科技技術,一個國家的集成電路發展水平最能衡量整體的科技水平,目前受到國家的高度重視,特別是關于集成電路的芯片研發領域。

近年來,國內越來越多的科研機構、高校院所、IC企業研發部門等逐步關注和從事集成電路的電磁兼容性(IC EMC)研究。

目前關于IC EMC的相關研究國外起步較早,發展較快,已經形成比較完善的理論體系以及先進的測試研究設備,像歐洲的法國、德國、美國等,亞洲的韓國、日本,新加坡。

國內的相關的IC EMC研究目前集中于高校院所,如國防科技大學、浙江大學、解放軍信息工程大學、中科院微電子所等,近年來也取得了重要成果。

2. 電磁敏感度

電磁兼容性分為電磁干擾(EMI)和電磁敏感度(EMS)。簡單的說,EMI指的是待測設備影響其它設備正常工作產生的電磁輻射,EMS指的是設備抵御外界電磁輻射干擾的能力。

目前關于電磁敏感度測試分為多個項目,如傳導、輻射、靜電放電、電快速脈沖群、浪涌等。本文介紹其中兩種測試方法。

3. 電磁敏感度測試方法

3.1傳導抗擾度

傳導抗擾度測試主要分為直接功率注入法、大電流注入法。這里介紹直接功率注入法。

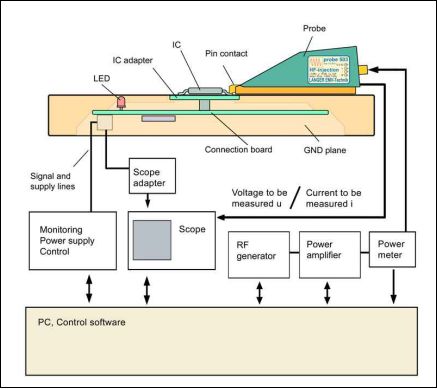

直接功率注入法,通過干擾源產生干擾脈沖,經過功放、定向耦合器、注入網絡,進而注入測試設備。通過失效判據來判斷設備的功能狀態,確定注入電壓的大小,測試框圖如圖1所示,圖2為實際設備的配置,具體配置參考IEC 62132。

圖1 測試框圖

圖2 測試設備

測試過程中,需要注意盡量按照測試標準進行測試,另外,相關測試板的設計要充分考慮接地設置。

3.2 靜電放電

靜電放電測試是設備抗擾度測試的重要項目,目前關于ESD的研究,國內起步較早,取得了不錯的研究成果。但是ESD相關測試設備過于昂貴, 一般小型研究機構無法從事進一步研究,其研究成果大多集中于測試設備完備的大型科研機構。

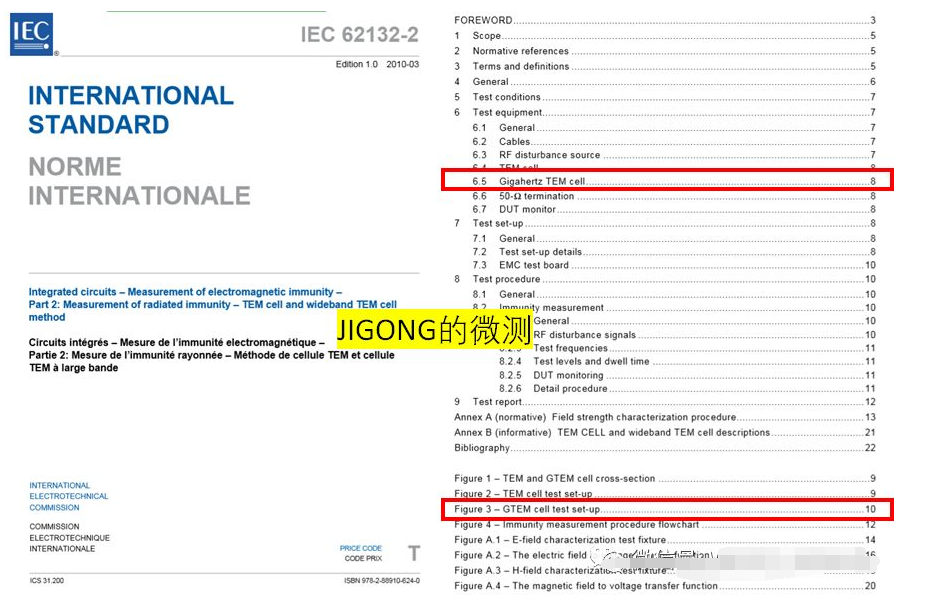

目前國際上有關于ESD測試的通用標準IEC 61000,規定了ESD脈沖的幅值和上升時間,如圖3所示,圖4為標準的ESD發生器模型。

圖3 ESD脈沖波形

圖4 ESD發生器模型

ESD測試方法簡單,只需把測試探頭壓上測試引腳注入脈沖波形即可,在測試過程中,測試人員要全程穿戴接地手環,防止人體自身靜電造成干擾。

-

集成電路

+關注

關注

5381文章

11385瀏覽量

360876 -

電磁兼容

+關注

關注

54文章

1847瀏覽量

97805

原文標題:兩種集成電路電磁敏感度測試方法介紹

文章出處:【微信號:EMC_EMI,微信公眾號:電磁兼容EMC】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

集成電路的電磁兼容測試概述

電磁兼容性分析的方法

混合集成電路的電磁兼容設計

交流穩壓電源的電磁兼容要求與測試方法詳細介紹

集成電路電磁兼容性設計應遵循的原則和方法

汽車設計中的電磁兼容性和集成電路IC問題解決方案

集成電路IC的EMC測試標準

如何設計混合集成電路的電磁兼容

介紹集成電路電磁兼容測試的兩種方法

介紹集成電路電磁兼容測試的兩種方法

評論