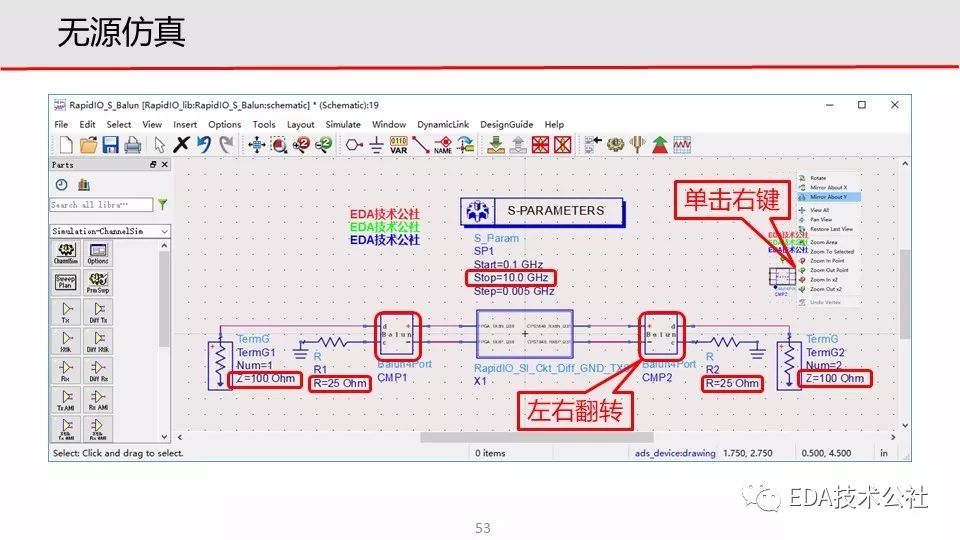

一、參考前文的前仿真S參數無源鏈路搭建方法,使用SIPro/PIPro提取的走線S參數符號,搭建后仿真無源仿真鏈路原理圖,并按下圖所示修改相關參數。

二、單擊快捷圖標欄的齒輪圖標啟動仿真,仿真完畢后,參考前文的前仿真中回波損耗和TDR阻抗曲線圖提取方法提取后仿真的回波損耗和TDR阻抗曲線圖。

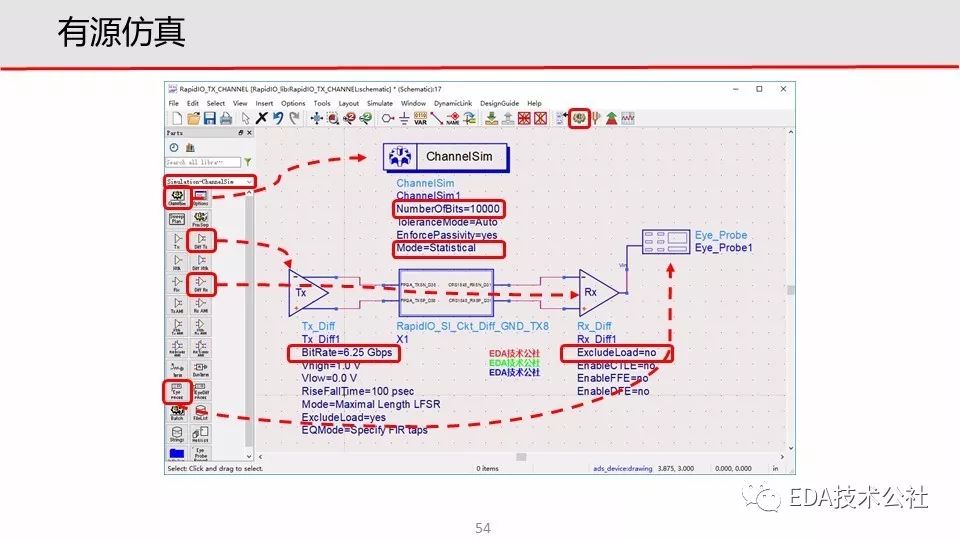

三、參考前文的前仿真有源鏈路搭建方法,搭建后仿真有源鏈路原理圖,并按下圖所示修改相關參數,眼圖模板的設置方法一并參考前文。

四、單擊快捷圖標欄的齒輪圖標啟動仿真,仿真完畢后,參考前文的前仿真中眼圖的提取方法提取后仿真的眼圖。

至此,一個簡單的串行鏈路后仿真就完成了,根據不同信號的標準規范要求,對曲線圖進行分析,并留有一定的余量,如有不滿足,則需要優化PCB文件上的走線、過孔或器件參數。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

pcb

+關注

關注

4296文章

22778瀏覽量

393368 -

串行

+關注

關注

0文章

235瀏覽量

33692

原文標題:ADS操作系列之串行鏈路后仿真

文章出處:【微信號:eda365wx,微信公眾號:EDA365電子論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

構建JESD204B鏈路的步驟

是:代碼組同步 (CGS)、初始信道對齊序列 (ILAS) 和用戶數據。今天我將探討在 TX 與 RX 之間必然會出現的信號發送技術,完成構建有效鏈路所需的必要步驟。假設您已經在 TX 與 RX 之間

發表于 09-13 09:55

基于高速串行數字技術的JESD204B鏈路延時設計

描述JESD204B 鏈路是數據轉換器數字接口的最新趨勢。這些鏈路利用高速串行數字技術提供很大的益處(包括增大的信道密度)。此參考設計解決了

發表于 11-21 16:51

高速時鐘如何驅動串行鏈路?

的時鐘)。高速時鐘如何驅動串行鏈路?我應該在哪里連接?以上來自于谷歌翻譯以下為原文Hi all, I want to connect twoFreeware ML605 boards

發表于 02-13 06:22

構建JESD204B鏈路的步驟

(CGS)、初始信道對齊序列 (ILAS) 和用戶數據。今天我將探討在 TX 與 RX 之間必然會出現的信號發送技術,完成構建有效鏈路所需的必要步驟。假設您已經在 TX 與 RX 之間建立了所需的電氣

發表于 11-21 07:18

MAX9249 吉比特多媒體串行鏈路串行器,具有LVDS系統

MAX9249 吉比特多媒體串行鏈路串行器,具有LVDS系統接口

概述

MAX9249串行器帶有LVDS系統接口,采用Maxim吉比特

發表于 03-28 09:17

?1120次閱讀

MAX9249 吉比特多媒體串行鏈路串行器,具有LVDS系統

MAX9249 吉比特多媒體串行鏈路串行器,具有LVDS系統接口

概述

MAX9249串行器帶有LVDS系統接口,采

發表于 05-20 08:51

?821次閱讀

MAX9265吉比特多媒體串行鏈路串行器

在MAX9265串行鏈路(GMSL)串行接口功能的LVDS系統和高帶寬數字內容保護(HDCP)的DVD和藍光™視頻和音頻數據加密千兆多媒體內容保護。與任何支持HDCP GM

發表于 01-19 09:37

?1129次閱讀

JNEye鏈路分析工具支持迅速評估高速Altera FPGA和SoC中的高速串行鏈路性能

Altera公司今天發布JNEye鏈路分析工具,提供驗證和電路板級全套設計工具。JNEye支持設計人員迅速方便的評估高速Altera FPGA和SoC中的高速串行鏈

發表于 09-14 15:10

?1360次閱讀

串行鏈路后仿真操作步驟

串行鏈路后仿真操作步驟

評論