DDS廣泛應用于雷達系統、數字通信、電子對抗、電子測量等民用軍用設備中。

它的優點:

?工作頻率范圍很寬

?極高的頻率分辨率

?極短的頻率轉換時間

?數字調制性能好

?頻率轉換連續

DDS基本原理

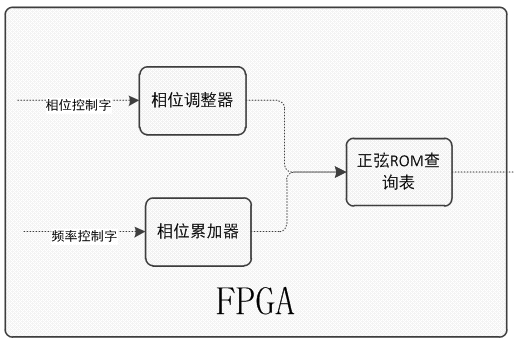

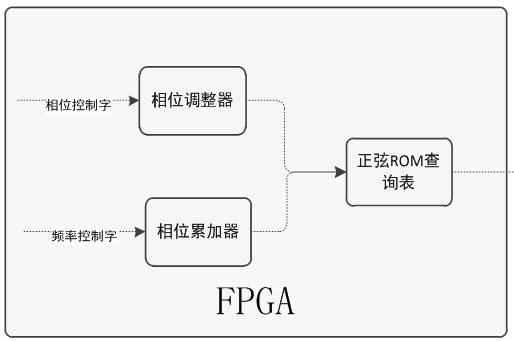

1.原理框圖

圖1. FPGA產生DDS框圖

上圖就是DDS的的FPGA實現框圖,完整的DDS還應該在外面有DAC和低通濾波器的,然而很多時候我們是不需要這兩個的,因為上圖的DDS輸出的信號就在數字域,凡是數學域的信號都可以用它參與處理了,所以正弦ROM查找表出來后的信號可以直接給到其他的邏輯使用。只有要在模擬域參與處理才會把DDS的數字信號用DAC和低通濾波變換成模擬信號。

2.DDS正弦波產生原理

正弦ROM查找表里面就是按地址存放的一個周期的正弦波,可以根據幅值精度要求分成256,1024,等點數,點數越多,波形越精細,越接近真實的模擬正弦波。但是由于FPGA資源有限,選擇一個能夠滿足要求的點數就足夠了。

相位調整器是控制輸出波形的初相位,也就是波形輸出起點從哪里開始。

相位累加器是控制ROM地址跳變的。相位累加器在每個時鐘脈沖輸入時,把頻率控制字累加一次,相位累加器的輸出數據就是信號的相位,也就是ROM的地址。由于相位累加器字長的限制,相位累加器累加到一定值后,其輸出將會溢出,這樣波形存儲器的地址就會循環一次,即意味著輸出波形循環一周。故改變頻率控制字即相位增量,就可以改變相位累加器的溢出時間,在時鐘頻率不變的條件下就可以改變輸出頻率。改變查表尋址的時鐘頻率,同樣也可以改變輸出波形的頻率。

也就是說通過相位調整器和相位累加器就可以控制你輸出波形的相位和頻率!

DDS實例說明

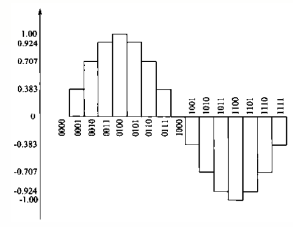

1. 16點DDS舉例

下圖是一個16點的DDS ROM存取示意圖,橫軸是二進制的ROM地址,縱軸是每個地址對應的幅值。

如果頻率控制字K=1,相位控制字是0,那么ROM輸出就是從0開始+1,一直到15再次歸0,如此循環。如果DDS工作時鐘是Fc,那么這種情況下,輸出正弦波頻率Fout就是Fc/(2^4)=Fc/16。如果K=2,輸出則是一半的時間就輸出完成整個周期所以是Fc/(2^4)*2=Fc/8。以此類推可以得到如下公式,N是ROM地址位寬,也就是頻率控制字的二進制位寬:

圖2. DDS輸出 波形示意圖

頻率分辨率,也就是頻率控制字每變化1,頻率變化的大小,公式如下:

本質上也就是K=1和0的時候的輸出頻率之差,這個計算起來是最簡單的。

2. 提高頻率分辨率的方法

根據公式2我們可以得到:N越大,也就是頻率控制字位寬越大,那么分辨率越高,我們設置的任意頻率都可以做到更接近,頻譜上就越看不出差別。而且我們可以知道,這和輸出波形的位寬是無關的,輸出位寬只和幅值精度有關。也就是說,我們可以用一個ROM存1024個點,每個點16bit精度,但是頻率控制字是32bit,累加結果只用最高10bit,這樣,就可以讓ROM存儲少,但是頻率分辨率確很高。這種方法在實際中也是很實用的方法。

這里我寫了一個高分辨率的DDS的例程,僅供參考,百度云鏈接如下:

源碼:

鏈接:https://pan.baidu.com/s/18TSmRoSLG678bNnYYfZl5A

提取碼:loie

tb:

鏈接:https://pan.baidu.com/s/1K8pvF8i9N6KL935KmXcbGA

提取碼:ahig

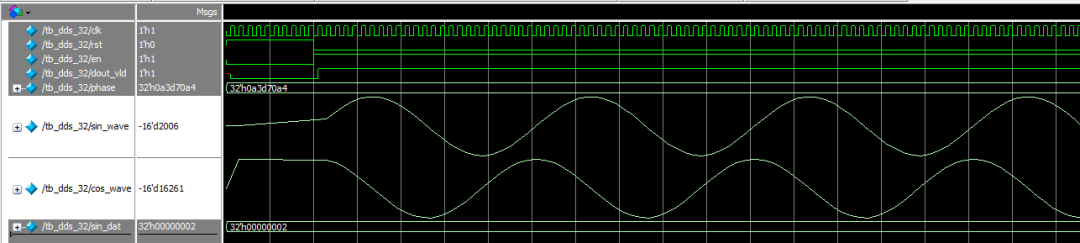

仿真結果說明

如下圖所示,rst為高電平時復位整個模塊,en為高電平整個模塊才會工作,dout_vld為高電平的時候輸出數據才是有效的點。所以輸出可以根據dout_vld為1的時候打印到文件里面,用matlab分析頻譜。由于輸出數字信號一定是離散的所以一定會有高頻分量,只是占比多少的問題,后面的模擬濾波器如果設置合理是可以把基頻分量取出來的,這樣就可以實現DA功能。DDS輸出頻率越高,三角函數畸變也就越嚴重,但是實際處理過程中往往不需要他的波形多么接近正弦波,只要頻譜的譜線足夠干凈就可以。詳見下一節MATLAB分析。

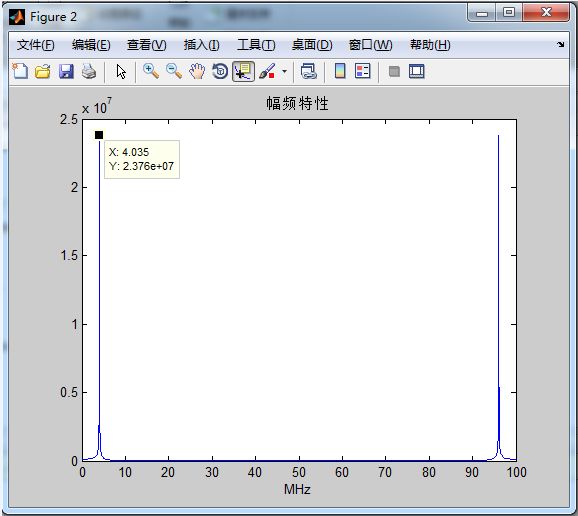

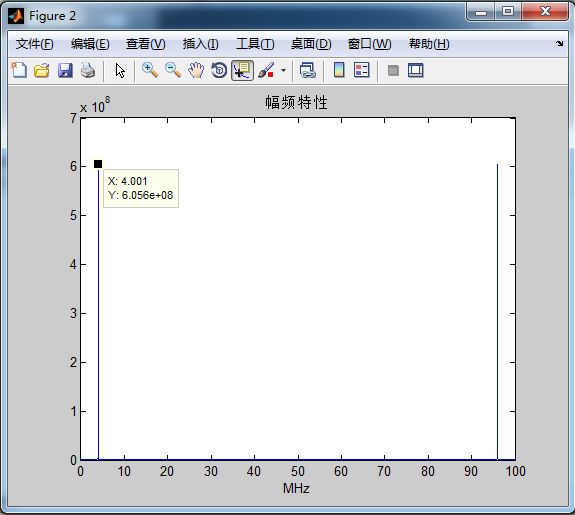

matlab結果說明

tb默認設置DDS工作在100M時鐘下,產生4M正弦波,輸出2048點后用這些點去做FFT,結果如下圖所示,結果顯示正弦波頻率是4.035M,和理論預測相差35KHz,準確度為0.875%。然而按照32bit的位寬精度應該比這個精確的多的。那么為什么會有這種差距呢?原因是100M的采樣率,1024點FFT分辨率只有0.1M左右,遠遠大于DDS的輸出頻率分辨率,所以,即便DDS輸出頻率很準確,FFT也不會認為有那么準確,必須要FFT分辨率大于DDS分辨率的時候才能準確的計算出DDS的頻譜。

那么按照以上理論,只需要提高FFT點數,DDS的結果應該更接近理想結果,于是我們輸出131072點之后我們做FFT,結果如下:

頻譜顯示為4.001MHz,準確度為0.025%,確實比2048點精準了很多倍。然而這里的FFT分辨率其實還是不夠的,只不過輸出太多點數需要花時間,有興趣的讀者可以繼續增大點數看看分辨率究竟有多高,可能會讓你嚇一跳哦!

這里其實也體現了DDS的優點,輸出頻率精度非常高,而且相位穩定可靠,消耗資源又少!

-

Verilog

+關注

關注

28文章

1345瀏覽量

109988 -

DDS

+關注

關注

21文章

631瀏覽量

152544 -

調整器

+關注

關注

3文章

74瀏覽量

19708

原文標題:verilog輕松實現高分辨率DDS

文章出處:【微信號:HaveFunFPGA,微信公眾號:玩兒轉FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

增強高分辨率圖像捕獲的選擇

單片機內置ADC實現高分辨率采樣的方法

垂直分辨率與使用高分辨率示波器測量微小信號的介紹

太秀了!單片機內置ADC實現高分辨率采樣?

教你如何利用verilog輕松實現高分辨率DDS

verilog輕松實現高分辨率DDS

verilog輕松實現高分辨率DDS

評論