微控制器的封裝在系統(tǒng)的小型化中起著關(guān)鍵作用。芯片上外設(shè)選擇,焊盤數(shù)量和芯片尺寸的權(quán)衡都限制了縮小微控制器尺寸的能力,但仍然有助于減小終端設(shè)備的整體尺寸。

散熱問題也很重要考慮微控制器的尺寸變小。隨著小型芯片上的晶體管越來越多,以更高的頻率運行,功耗是一個關(guān)鍵考慮因素。在降低電壓和選通不同外圍設(shè)備以使未使用的元件不消耗功率的同時可以降低總熱負荷,然后必須有效地去除產(chǎn)生的多余熱量或者微控制器將降級并最終失效。這是微控制器系統(tǒng)小型化時必須考慮的一個關(guān)鍵可靠性問題。

這是引腳與尺寸之間的折衷所在。封裝上的附加引腳可用于連接散熱通孔,以消除多余的熱量來自微控制器和其他可能對高溫敏感的設(shè)備,如無線接口。

雖然最新的芯片級封裝可以減少具有特定功能的設(shè)備的總體占用空間,但占用的面積減少了四分之一,將更多外設(shè)集成到器件中并擁有更多引腳進行散熱的機會可能更為重要。

設(shè)計人員還必須意識到小型化的目標(biāo)。 ARM 32位內(nèi)核,例如Cortex-M0 +甚至M4,小于1平方毫米的硅片 - 芯片尺寸更多地取決于芯片上的內(nèi)存量,對于封裝考慮至關(guān)重要,需要連接外部世界的外圍設(shè)備。最小的M0器件,例如飛思卡爾的Kinetis KL02,在芯片級封裝中可以小到1.9 x 2.0 mm,幾乎不比芯片本身大。在不到4平方毫米的情況下,與球柵陣列或LGA封裝相比,PCB面積減少了25%,但GPIO的數(shù)量增加了60%,最多可達28行。這一舉措幾乎是“硅塵”,使設(shè)計人員能夠大幅減小電路板尺寸,同時不會影響最終產(chǎn)品的性能,功能集成和功耗。

圖1:Kinetis KL02采用芯片級封裝的系列產(chǎn)品可提供幾平方毫米的完整微控制器。

在這種尺寸下,功耗和散熱考慮是關(guān)鍵,芯片上可以做很多事情來降低整體功耗并允許一個較小的包裹。該內(nèi)核以48 MHz的頻率運行,有助于在整個-40°C至+ 105°C的溫度范圍內(nèi)保持功率下降,并允許器件在盡可能多的不同環(huán)境中使用。還有多種低功耗模式,例如新的計算模式,通過將外設(shè)置于異步停止模式來降低動態(tài)功耗。低功耗UART(LPUART),SPI,I2C,數(shù)據(jù)轉(zhuǎn)換器,低功耗定時器和DMA引擎均支持低功耗模式操作,無需喚醒內(nèi)核即可運行。

但是,這并不一定反映硅的實際用途。如果需要單獨的掩模,制造具有各種外圍設(shè)備和存儲器選項的微控制器的許多不同版本實際上是昂貴的。相反,實現(xiàn)和制造具有超集功能的單一設(shè)計,并且僅連接一組特定功能。這使得硅供應(yīng)商能夠提供廣泛的產(chǎn)品,同時最大限度地降低制造成本并從規(guī)模經(jīng)濟中獲益。

下一個發(fā)展階段是創(chuàng)建更靈活的I/O配置。正如內(nèi)部總線矩陣連接外設(shè)一樣(如Atmel 4S系列),供應(yīng)商也在推出帶有連接I/O引腳的矩陣的設(shè)計。這允許任何外設(shè)連接到任何I/O引腳,為供應(yīng)商提供更大的靈活性,以提供一系列引腳兼容的器件,其中相同的I/O始終位于同一位置。由于存在備用硅,這有助于系統(tǒng)設(shè)計人員在不影響整體尺寸的情況下實現(xiàn)可擴展性能的設(shè)計。

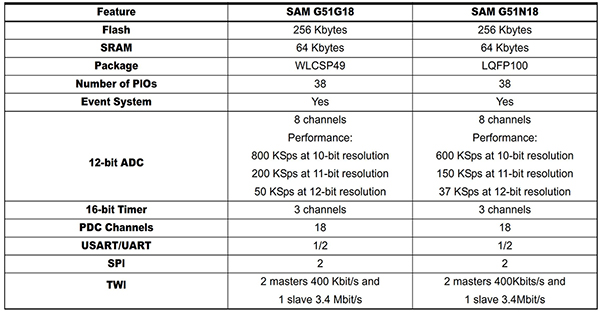

這一切都意味著封裝技術(shù)是微控制器小型化的關(guān)鍵。 Atmel開發(fā)了SAM G51系列閃存微控制器,它也基于具有浮點支持的M4內(nèi)核。它還可以以48 MHz的最高速度運行,具有高達256 KB的閃存和高達64 KB的SRAM。外設(shè)集包括一個USART,兩個UART,兩個TWI,一個高速TWI,最多兩個SPI,一個三通道通用16位定時器,一個RTT和一個8通道,12位ADC,提高引腳數(shù)要求。

圖2:Atmel SAM G51系列微控制器顯示了封裝選項范圍。

該外設(shè)集允許SAM G51系列針對a廣泛的應(yīng)用包括消費者,工業(yè)控制和PC外圍設(shè)備,只有兩種封裝類型 - 49球WLCSP芯片級封裝或100引腳LQFP封裝。

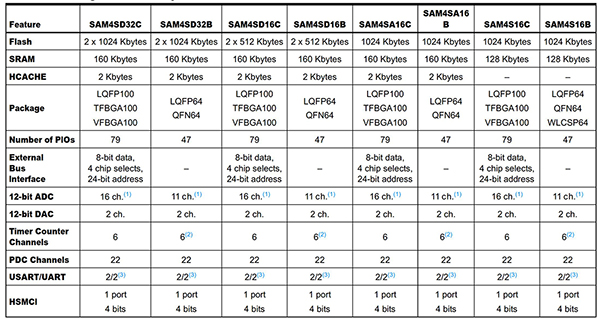

與此同時,Atmel的SAM4S系列也基于ARM Cortex-M4處理器內(nèi)核。它的最高運行速度為120 MHz,具有高達2048 KB的閃存,可選的雙存儲區(qū)實現(xiàn)和高速緩存,以及高達160 KB的SRAM。外設(shè)包括帶嵌入式收發(fā)器的全速USB設(shè)備端口,用于SDIO/SD/MMC的高速MCI,帶存儲器控制器的外部總線接口,兩個USART,兩個UART,兩個TWI,三個SPI,一個I2S,以及一個PWM定時器,兩個三通道通用16位定時器(具有步進電機和正交解碼器邏輯支持),一個RTC,一個12位ADC,一個12位DAC和一個模擬比較器。 》所有這些都對包裝和引腳數(shù)量提出了更高的要求。該系列具有多達79個I/O線,具有外部中斷功能(邊沿或電平靈敏度),去抖,毛刺濾波和片上串聯(lián)電阻終端,以及3個32位并行輸入/輸出控制器。 》這導(dǎo)致了一系列封裝,從100引腳到48引腳,但使用更傳統(tǒng)的技術(shù):

100引腳封裝

LQFP,14 x 14 mm,間距0.5 mm

TFBGA,9 x 9 mm,間距0.8 mm

VFBGA,7 x 7 mm ,間距0.65 mm

64引腳封裝

LQFP,10 x 10 mm,間距0.5 mm

QFN,9 x 9 mm,間距0.5 mm

WLCSP,4.42 x 3.42 mm,間距0.4 mm(SAM4S16/S8)

WLCSP,3.32 x 3.32 mm,間距0.4 mm(SAM4S4/S2)

48引腳封裝

LQFP,7 x 7 mm,間距0.5 mm

QFN,7 x 7 mm,間距0.5 mm

圖3:Atmel SAM4S系列具有更廣泛的外設(shè)選項,可實現(xiàn)更大的封裝。

未來趨勢

在同一封裝中疊加芯片的新封裝技術(shù)也有助于減少整體足跡。微控制器芯片不是在微控制器旁邊有一個單獨的存儲芯片,而是安裝在一個封裝中的存儲器芯片或大型FPGA的頂部。這種方法通常稱為2.5D,需要硅中介層和硅通孔(TSV),這是一種相對較新的技術(shù),現(xiàn)在正在逐漸成熟并變得越來越普遍。這用于需要大量存儲器的高端設(shè)備,這些設(shè)備無法經(jīng)濟高效地集成在單個芯片上。

全3D封裝可將多個芯片直接堆疊在一起;也許邊緣上有I/O焊盤,以允許不同器件之間的互連。雖然這是小型化的長期目標(biāo),將印刷電路板上的所有元件從微控制器到存儲器和無線接口整合到一個封裝器件中,但它仍然需要克服許多成本,可靠性和散熱問題。 br》結(jié)論

來自多個供應(yīng)商的各種微控制器隱藏了這種設(shè)備小型化的策略。來自一個供應(yīng)商的不同系列的封裝范圍,都在同一個核心,展示了封裝,外設(shè)組合,功耗和系統(tǒng)尺寸之間的復(fù)雜權(quán)衡。在性能曲線的下游,具有復(fù)雜外設(shè)的32位控制器現(xiàn)在只有幾平方毫米,成為滲透到物聯(lián)網(wǎng)中的“硅塵”。

-

微控制器

+關(guān)注

關(guān)注

48文章

7489瀏覽量

151055 -

芯片

+關(guān)注

關(guān)注

453文章

50417瀏覽量

421850 -

封裝

+關(guān)注

關(guān)注

126文章

7785瀏覽量

142727

發(fā)布評論請先 登錄

相關(guān)推薦

微控制器小型化給系統(tǒng)設(shè)計帶來的挑戰(zhàn)

電源的小型化輕量化設(shè)計方案

小型化醫(yī)療電子設(shè)備

微電子技術(shù)有什么重要性?

怎樣去解決小型化DC/DC應(yīng)用設(shè)計的問題?

加載技術(shù)在天線小型化設(shè)計中的應(yīng)用是什么?

電源對電子設(shè)備的重要性

論調(diào)節(jié)閥的重要性

基于CPLD的機載小型化控制與保護

封裝技術(shù)對于微控制器小型化的重要性

封裝技術(shù)對于微控制器小型化的重要性

評論