現代MCU具有各種存儲元件,了解其組織,性能限制和功耗對于有效實施應用程序至關重要。特別是,用于代碼存儲的片上閃存的特性,用于數據存儲的片上SRAM的組織以及片外存儲器的訪問特性將對整體處理效率產生巨大影響。讓我們分析一下這些關鍵的存儲器元件,以便更好地了解如何最有效地使用它們來最大限度地提高性能,降低功耗并優化系統成本。

片上閃存

片上閃存可能是最關鍵的任何應用程序中的內存元素,因為它通常是處理器的所有指令的源。如果沒有有效地獲取指令,則整體MCU性能將受到影響。向CPU提供指令有兩種不同的方法。在一種方法中,存儲器根據需要快速操作以匹配CPU的指令周期。例如,瑞薩RX600群使用先進的閃存技術,提供對指令存儲器的高性能零等待狀態訪問。這種方法可以簡化CPU架構和確定性時序。

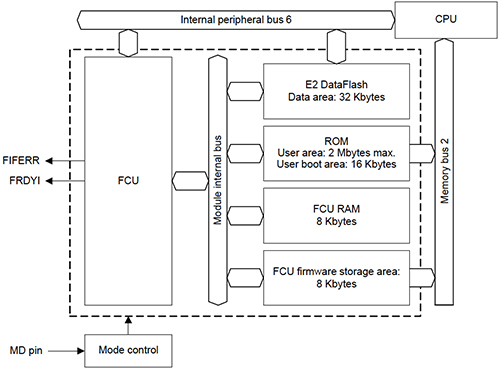

訪問閃存通常使用雙端口方式進行CPU訪問,通過高速總線進行讀取操作和更慢訪問,使用閃存控制器進行寫入操作。 RX600的閃存接口如圖1所示。請注意,閃存進一步分為數據閃存部分,用于存儲經常修改的非易失性信息,以及指令部分,通常被視為讀取僅存儲器(ROM),即使它使用Flash技術,并且可以在制造期間或通過系統更新由用戶多次重新編程。閃存控制單元(FCU)是一個獨立的專用處理器,可管理閃存寫入并具有自己的RAM和固件存儲器塊。 CPU可以啟動FCU操作;這是使用圖1頂部所示的外設總線實現的。

圖1:瑞薩RX600 MCU的閃存接口(由Renesas提供)。

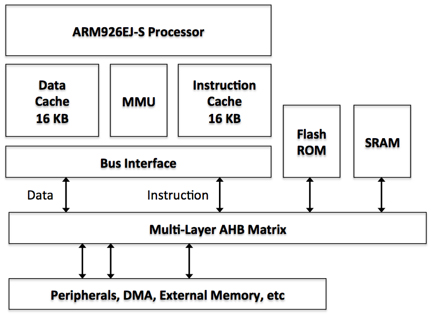

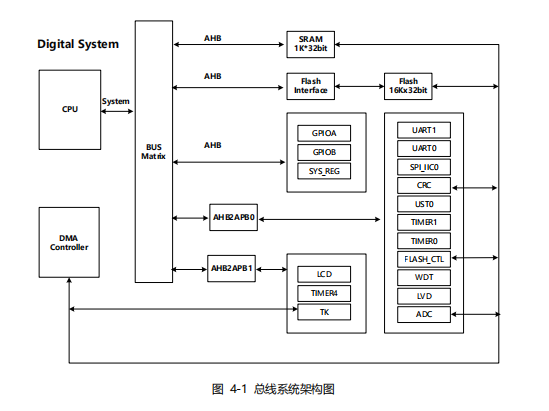

另一種架構使用比CPU時鐘慢的指令存儲器,可能需要插入等待狀態。這可以顯著降低處理性能,因此通常在CPU和較慢的指令和數據存儲器塊之間插入高速緩沖存儲器。高速緩存存儲最近的存儲器訪問,并且如果再次需要相同的指令或數據元素,則可以在不必訪問較慢的主存儲器塊的情況下使用它。 Atmel SAM9G MCU的數據和指令高速緩沖存儲器的組織如圖2所示.16 KB存儲器提供快速的本地存儲,減少了CPU通過多路復用訪問大型Flash ROM或SRAM塊所需的次數。層AHB矩陣。請注意,使用本地高速緩存存儲器的能力也減少了總線矩陣流量,因此DMA或外設訪問將具有額外的總線帶寬。

圖2:Atmel的SAM9G MCU的高速緩存存儲器接口。

如果高速緩存存儲器是高效的,整個“內部循環”可以適應高速緩存,這可能導致應用程序的最關鍵部分幾乎為零等待狀態性能。注意,在該方法中執行定時可能更難以估計,因為高速緩存“未命中”導致意外的處理減速。另外,如果一個小的內部循環不可用,或者數據的組織方式使得緩存算法所依賴的“位置”被違反,則處理可能變得非常低效。然而,一般而言,由于大多數算法的局部特性,緩存算法已被證明可以提高效率。

更復雜的緩存架構

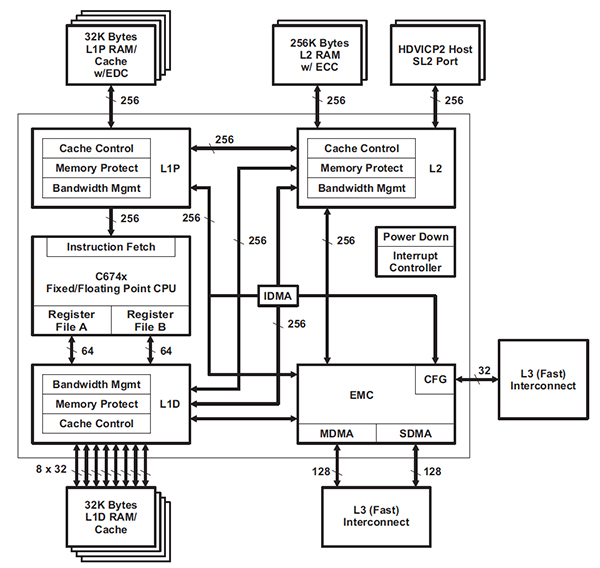

高帶寬計算密集型MCU,如德州儀器面向DSP的TMS320DM814x視頻處理器,高速緩沖存儲器系統可以具有額外的復雜程度。 TMS320DM814x的處理器到存儲器接口(圖3)具有三種不同級別的存儲器層次結構。最接近處理器的是兩個1級(L1)高速緩存存儲器,一個用于指令,一個用于數據。當所需數據不在L1高速緩存中時,向2級(L2)存儲器發出請求。 L2存儲器是多端口存儲器,具有多個存儲區以進一步組織數據。帶寬管理用于每個高速緩存控制器,以管理存儲器訪問的優先級,以保持數據順暢地流入和流出處理器。最多可提供9個優先級,如果低優先級訪問被阻止時間過長(超過Max_Wait周期),則可以優先考慮優先級。

這種多級內存架構在高帶寬時并不少見是必需的,包含優先級和其他高級管理功能對于減輕優化帶寬的負擔至關重要。嘗試識別包含高效緩存,智能帶寬管理功能和多個內存端口的MCU,以自動優化內存帶寬。

圖3:德州儀器的TMS320DM814x DSP內存接口架構(圖片提供)德州儀器(TI))。片上SRAM

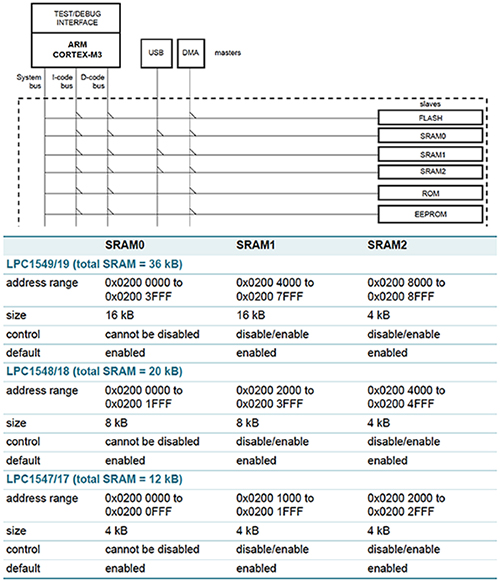

需要了解片上SRAM的組織,以便在應用中組織數據元素以獲得最佳效率。在許多情況下,MCU將SRAM組織成單獨的塊,可以由總線主機獨立訪問以重疊并提高數據傳輸效率。恩智浦半導體LPC15xx MCU將SRAM分成三個不同的模塊,每個模塊通過多級AHB矩陣可用于處理器,USB或DMA主設備,如圖4頂部所示。圖中底部顯示了SRAM模塊的特性,如SRAM模塊的特性。作為大小,地址范圍,以及是否可以禁用它以節省每個LPC15xx系列成員的電源分配不同大小的SRAM模塊并不罕見,無論是從處理角度還是從功率角度來看,都可以幫助您以最有效的方式對設計進行分區。讓我們更詳細地了解如何智能地將您的算法要求與SRAM塊組織相匹配,從而提高處理能力和功率效率。

圖4:通過AHB矩陣將NXP LPC15xx SRAM連接到總線主控器和SRAM模塊特性(恩智浦提供)。

提高處理效率

基于MCU的設計中最常見的效率改進之一是使用DMA功能從CPU卸載簡單的數據傳輸功能。如果CPU可以進入休眠模式或與數據傳輸并行處理,則整體效率得到提高。多個SRAM塊的存在可以成為支持無沖突并行操作的重要元素。此外,同樣具有多級總線接口的高級MCU,如NXP LPC15xx,可以提供對共享資源的優先訪問,以自動提高處理效率。例如,如果算法必須通過USB接口接收數據,則處理數據,存儲數據,當有足夠的數據可用時,通過另一個接口發送結果,各種數據緩沖區的位置對整體性能至關重要。最好將輸入和輸出緩沖區分成不同的SRAM塊,因此來自CPU,DMA和USB端口的主控請求不會同時嘗試訪問同一個塊。為主訪問建立正確的優先級設置將有助于消除算法停頓。確保在數據處理中以更高的優先級捕獲接收的數據對于消除數據接收錯誤和冗長的重試周期至關重要。了解算法的數據流要求是有效利用內存塊的關鍵要求。

如上圖4的下半部分所示,可以啟用或禁用某些NXP LPC15xx SRAM模塊以降低功耗。組織數據以利用這一點可以有助于實現積極的電力目標。例如,許多算法在CPU計算期間使用數據緩沖區來存儲大數據。計算完成后,無需保存該數據,并且可以禁用相關的存儲器塊以節省電量。如果SRAM存儲器塊在使用之前需要一些額外的時間來“喚醒”,則始終啟用的SRAM塊中的較小緩沖區可以存儲數據,直到新啟用的塊準備就緒。在某些情況下,需要進行詳細的計算以確定這些電源管理技術可以產生的節能量(如果有的話);但是具有多個具有省電選項的SRAM模塊通常可以提高功率效率。

外部存儲器接口

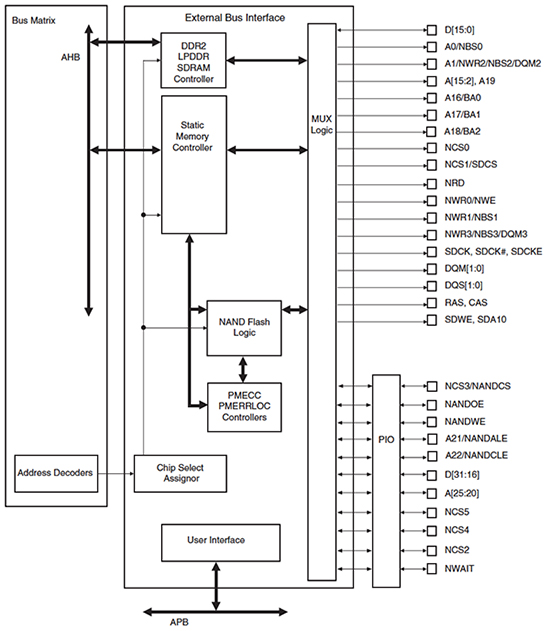

訪問片外存儲器資源會增加顯著的延遲,因此尋找緩沖片內數據和預取存儲器的機會從片外可以顯著提高整體帶寬。將片上存儲器緩沖器匹配到適當的片上SRAM塊是重要的考慮因素,并且可以被認為是先前描述的技術的擴展。但是,外部存儲器接口通常組合多種類型的訪問。了解如何在訪問多個外部存儲器時避免沖突同樣重要。例如,Atmel SAM9G上的外部存儲器接口(如圖5所示)支持組合的DDR,LPDDR和SDRAM控制器,靜態存儲器控制器和NAND閃存控制器。雙從屬接口連接到多級總線矩陣,以便在由不同總線主控器啟動時傳輸可以重疊。請注意,靜態存儲器控制器和NAND控制器共享一個公共從端口。嘗試重疊NAND和靜態存儲器訪問可能效率低于重疊DDR2和NAND訪問。同樣需要注意在內部存儲器塊中分配數據以避免影響效率

圖5:Atmel SAM9G MCU上的外部存儲器接口(由Atmel提供)。許多存儲器接口子系統還提供緩存或本地存儲器緩沖區以減少訪問延遲。一些高級DDR控制器還可以自動優先考慮訪問并組合操作,以利用DDR內存架構的塊性質。如果外部存儲器流量是算法的重要組成部分,則必須檢查MCU上包含的存儲器控制器功能的詳細信息,以便更好地估計您可以預期的傳輸效率類型。

-

處理器

+關注

關注

68文章

19178瀏覽量

229202 -

mcu

+關注

關注

146文章

17019瀏覽量

350376 -

存儲器

+關注

關注

38文章

7455瀏覽量

163624

發布評論請先 登錄

相關推薦

怎樣使移動電話存儲子系統的功耗降至最低

KeyStone存儲器架構

8個超低功耗 MCU 的設計指導原則

采用低功耗28nm FPGA降低系統總成本

基于FRAM的MCU在低功耗的應用

超低功耗的嵌入式應用的實現:降低系統中電池功耗

超低功耗MCU如何降低功耗

Ramtron推出最低功耗非易失性存儲器FM25P16

可提高性能并降低功耗的UltraScale架構

低功耗藍牙芯片的應用可顯著降低功耗和成本

電磁突破可以降低功耗,提高數字存儲器的速度

華大電子MCU-CIU32F011x3、CIU32F031x5系統及存儲器架構

使用MCU的存儲器架構降低功耗并優化系統成本

使用MCU的存儲器架構降低功耗并優化系統成本

評論