電磁兼容EMC(Electromagnetic Compatibility)是指設(shè)備或系統(tǒng)在所處的電磁環(huán)境中能正常工作且不對該環(huán)境中任何其他事物構(gòu)成不能承受的電磁干擾的能力。

經(jīng)過這幾十年半導(dǎo)體技術(shù)的不斷發(fā)展,集成電路(IC)的規(guī)模不斷擴(kuò)大,從1947年第一只鍺晶體管在貝爾實(shí)驗(yàn)室誕生,1961年第一片包含了4只晶體管的硅集成電路產(chǎn)品出現(xiàn),之后集成電路按照摩爾定律每12個(gè)月晶體管的數(shù)量翻一番發(fā)展,規(guī)模從SSI、LSI、VLSI、ULSI到現(xiàn)在一片芯片上包含上億只晶體管,形成片上系統(tǒng)(SoC);集成電路的工作頻率越來越高,頻率帶寬從1 MHz迅速提升到1 GHz;集成電路的應(yīng)用范圍也越來越廣,滲透到整個(gè)社會(huì)的各個(gè)角落。然而,隨著電子設(shè)備數(shù)量的逐漸增加,功能的不斷增強(qiáng)以及應(yīng)用領(lǐng)域不斷擴(kuò)展,電磁環(huán)境越來越復(fù)雜[1],電磁干擾問題日益突出,作為電子設(shè)備或系統(tǒng)必不可少的組成部分——集成電路能否在這樣的電磁環(huán)境中安全的工作,并且不對其他器件或設(shè)備造成干擾,即集成電路自身的電磁發(fā)射和抗干擾問題,已成為集成電路設(shè)計(jì)、制造業(yè)關(guān)注的課題。本文將著重對集成電路的電磁兼容性進(jìn)行研究,包括電磁兼容的基本理論、集成電路電磁兼容性的基本概念以及滿足電磁兼容要求的設(shè)計(jì)方法。

1 電磁兼容的基本理論

1.1 基本概念

電磁兼容主要研究的是如何使在同一環(huán)境下工作的各種電氣電子系統(tǒng)、分系統(tǒng)、設(shè)備和元器件都能正常工作、互不干擾,達(dá)到兼容狀態(tài)[2]。在某種程度上也可以說是研究干擾和抗干擾的問題。電磁兼容分為電磁干擾和電磁敏感度。

電磁干擾EMI(Electromagnetic Interference)是指任何能中斷、阻礙、降低或限制電子設(shè)備有效性能的電磁能量。電磁干擾按干擾的類型分為傳導(dǎo)干擾和輻射干擾;按頻帶分為寬帶和窄帶干擾。傳導(dǎo)干擾又分為共模干擾和差模干擾;輻射干擾也分為共模干擾和差模干擾。

電磁敏感度EMS(Electromagnetic Susceptibility)是指存在電磁騷擾的情況下,電子設(shè)備或系統(tǒng)能夠不降低其運(yùn)行能力的性能。敏感度越高,其抗干擾能力越差。

圖1給出了電磁兼容性包含的內(nèi)容。設(shè)備的電磁兼容性包含了兩方面,一方面,設(shè)備要有抗電磁干擾的能力,即具有能夠在電磁干擾的環(huán)境中正常工作的能力;另一方面,設(shè)備工作中自身產(chǎn)生的電磁騷擾應(yīng)在一定水平之下,不能對同處于一個(gè)電磁環(huán)境中的任何事物構(gòu)成不能承受的電磁騷擾。衡量一種電子設(shè)備抗電磁干擾能力的指標(biāo)為抗擾性和敏感度。抗擾性是指在存在電磁騷擾的環(huán)境下,電子產(chǎn)品具有不降低其運(yùn)行性能的能力。敏感度是指電子產(chǎn)品受電磁干擾而被中斷或破壞趨勢的估量,它是由抗擾性不足引起的。電子產(chǎn)品對外界環(huán)境產(chǎn)生的干擾定義為電磁發(fā)射,即從源向外發(fā)出電磁能的現(xiàn)象。而這里的“發(fā)射”與通信學(xué)科中的“發(fā)射”含義是不太相同的,它既包括傳導(dǎo)發(fā)射,又包括輻射發(fā)射。

1.2.1 電磁干擾源

電磁干擾源是客觀存在的,是指產(chǎn)生EMI的組件、器件、設(shè)備、系統(tǒng)或自然現(xiàn)象。在一個(gè)微控制器系統(tǒng)里,時(shí)鐘電路通常是最大的寬帶噪聲發(fā)生器,而這個(gè)噪聲被分散到了整個(gè)頻譜,隨著大量的高速半導(dǎo)體器件的應(yīng)用,其邊沿跳變速率非常快,這種電路可以產(chǎn)生高達(dá)300 MHz的諧波干擾。

1.2.2 耦合路徑

耦合路徑指把能量從干擾源耦合(或傳輸)到敏感設(shè)備。根據(jù)耦合路徑的不同,干擾可分為傳導(dǎo)干擾和輻射干擾。傳導(dǎo)干擾是通過導(dǎo)線進(jìn)行傳播的,如果一條導(dǎo)線在一個(gè)有噪聲的環(huán)境中經(jīng)過,這條導(dǎo)線通過感應(yīng)將接收這個(gè)噪聲并將它傳遞到電路的其他部分,比如噪聲通過電源線進(jìn)入系統(tǒng)。傳導(dǎo)干擾方式必須在干擾源和感應(yīng)設(shè)備之間有完整的電路連接,干擾信號沿著連接電路傳遞到敏感器,發(fā)生干擾現(xiàn)象,傳輸電路導(dǎo)線、供電電源、公共阻抗、接地平板、電阻、電感、電容和互感元件等。輻射干擾是通過“場”進(jìn)行傳播的,每個(gè)電路都共享的電磁場,當(dāng)電路改變時(shí),就會(huì)產(chǎn)生電磁波,這些電磁波能耦合到附近的導(dǎo)體中并干擾電路中的其他信號。在集成電路設(shè)計(jì)中常見的輻射耦合有:大電流變化引起的電磁場經(jīng)導(dǎo)線感應(yīng)耦合形成的干擾;平行導(dǎo)線高頻信號之間的感應(yīng)以及高頻信號與周圍靠近的信號線之間的感應(yīng)耦合形成干擾。在實(shí)際工程中,兩個(gè)設(shè)備之間的干擾通常包含多種途徑的耦和形式。

1.2.3 敏感設(shè)備

敏感設(shè)備是指受到電磁騷擾源發(fā)射的電磁能量的作用時(shí),會(huì)受到傷害的人或其他生物,以及會(huì)發(fā)生電磁危害,導(dǎo)致性能降低或失效的器件、設(shè)備或系統(tǒng)。在數(shù)字電路中,臨近信號最容易受到電子干擾的影響,比如復(fù)位信號和中斷信號等;模擬的低級放大器、控制電路和電源調(diào)整電路也很容易受到噪聲的影響。

通過分析電磁干擾產(chǎn)生的三要素,可知消除電磁干擾要從去掉或隔離電磁干擾源、阻斷耦合路徑、提高設(shè)備的抗干擾能力3個(gè)方面入手,即很容易得到抑制電磁干擾的方法:一是設(shè)法降低電磁波輻射源或干擾源;二是設(shè)法切斷電磁耦合路徑;三是降低敏感設(shè)備的敏感度。

2 集成電路電磁兼容性分析

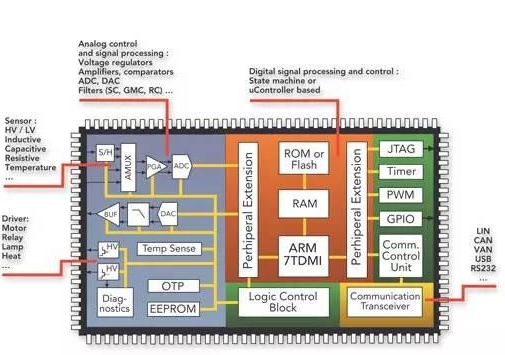

集成電路在電子設(shè)備的電磁兼容性方面起著非常重要的作用。通常,集成電路是產(chǎn)生信號和噪聲干擾的根源。將提供給它們的直流電源通過發(fā)射或耦合轉(zhuǎn)換成高頻電流、電壓,產(chǎn)生輻射,同樣它們自身也是受害者。一個(gè)典型電子系統(tǒng)的所有元器件當(dāng)中,IC是最容易受到過流和過壓損害的,即使它們沒有被毀壞,耦合到輸入端和電源端的噪聲也會(huì)使這些IC發(fā)生故障。由此可以看出,IC是EMC的根源,要提高電子系統(tǒng)的電磁兼容性,必須首先從根源入手,即在進(jìn)行IC設(shè)計(jì)時(shí)就要考慮到EMC問題。

集成電路的電磁兼容問題可分為芯片內(nèi)部EMC和芯片外部EMC兩大類。片內(nèi)EMC是指同一芯片內(nèi)一個(gè)電路或一些電路所產(chǎn)生信號或噪聲干擾其他電路的工作。片外EMC是指IC所產(chǎn)生的信號或噪聲影響芯片外的器件或電路,或者是IC的正常工作受到外部電路信號的干擾。

2.1 片內(nèi)EMC問題

最常見的兩種片內(nèi)EMC問題是串?dāng)_和同步開關(guān)噪聲。當(dāng)一個(gè)電路中的電壓或電流無意地耦合到另一個(gè)電路中時(shí),就產(chǎn)生了串?dāng)_。如果耦合足夠強(qiáng),耦合的信號還會(huì)影響被干擾電路接收到的信號幅度,從而引起電路故障或使其功能異常。

2.1.1 串?dāng)_

串?dāng)_可以定義為來自鄰近信號通路對某個(gè)信號通路的干擾,也可以描述為有意信號或噪聲對一個(gè)信號的耦合情況[4]。

如上所述,在集成電路中,一般有3種導(dǎo)致串?dāng)_的耦合機(jī)制:公共阻抗、電場耦合和磁場耦合。集成電路設(shè)計(jì)中可以通過遵循布線的基本準(zhǔn)則以及根據(jù)各種耦合機(jī)制及其產(chǎn)生的條件采取相應(yīng)的解決措施,同時(shí)跟蹤每個(gè)信號的電流路徑和電壓是非常重要的[5]。比如,對于公共阻抗耦合,其產(chǎn)生的條件是低頻率和低阻抗,可以采取隔離電流路徑、減小公共路徑阻抗等方法;對于電場耦合,其產(chǎn)生條件是高頻率和高阻抗,可以采取分離電路,用地導(dǎo)體隔離電路,減小信號電壓等措施。

2.1.2 同步開關(guān)噪聲

同步開關(guān)噪聲是由于在一個(gè)集成電路中各種電路共享同一個(gè)電源分布總線產(chǎn)生的。當(dāng)一個(gè)電路從電源總線吸納電流時(shí),在總線上會(huì)產(chǎn)生一個(gè)小的電壓降。電源總線上的這個(gè)電壓降會(huì)影響與總線相連的所有電路。同步開關(guān)噪聲可以通過在IC上提供低阻抗電源分布總線來減小。高速VLSI設(shè)計(jì)也使用芯片上的去耦電容來防止同步開關(guān)產(chǎn)生的問題。芯片上的去耦電容是連接在VDD和VSS之間的電容,為附近電路同時(shí)切換所需電流提供暫時(shí)的電荷來源。

2.2 片外EMC問題

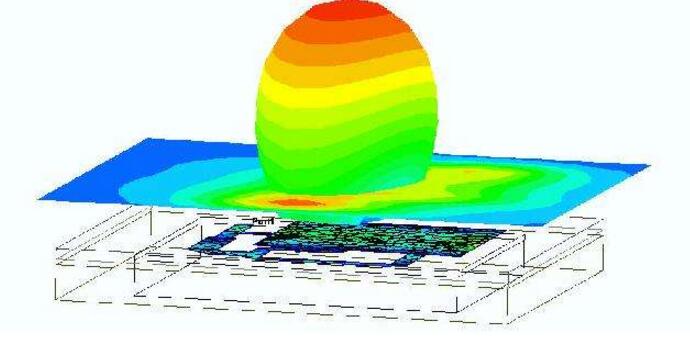

片外EMC問題通常有傳導(dǎo)耦合、電場耦合、磁場耦合和輻射場耦合4種類型。(1)傳導(dǎo)耦合。傳導(dǎo)耦合進(jìn)或出集成電路最明顯的途徑是封裝引腳或引線。(2)電場耦合。當(dāng)一個(gè)電壓跨過一個(gè)器件,引起兩個(gè)外導(dǎo)體上出現(xiàn)電壓時(shí),就發(fā)生了電場耦合。通常,當(dāng)金屬物體(如散熱片或電纜)非常靠近芯片封裝表面時(shí),這類耦合就會(huì)發(fā)生。(3)磁場耦合。當(dāng)器件的封裝內(nèi)包含高頻電流環(huán)時(shí),能量也能夠通過磁場耦合出器件。器件內(nèi)電流環(huán)的磁通量可能會(huì)連接到器件外的電路環(huán)上。可以采用使功率和信號環(huán)路面積盡可能小的方法來將磁場耦合減到最小。(4)輻射場耦合,指電磁能量通過空間轉(zhuǎn)移,空間距離一般大于幾個(gè)波長。集成電路器件的輻射,實(shí)際上是指噪聲耦合出集成電路,然后被其他東西輻射出去。通過提供更好的芯片上或封裝上的去耦,可以減小從電源端子吸入的高頻電流,從而能夠減小噪聲源的幅度[6]。

3 集成電路電磁兼容性設(shè)計(jì)方法研究

集成電路電磁兼容性的研究不僅涉及集成電路自身的電磁發(fā)射、抗擾動(dòng)測試和設(shè)計(jì)方法研究,而且有必要和集成電路的應(yīng)用相結(jié)合,將強(qiáng)制性標(biāo)準(zhǔn)對設(shè)備和系統(tǒng)的電磁兼容要求結(jié)合到集成電路的設(shè)計(jì)中,使得更易于設(shè)計(jì)出符合標(biāo)準(zhǔn)的最終產(chǎn)品。

目前,集成電路的工作頻率已達(dá)到吉赫茲,上升、下降時(shí)間僅為幾皮秒。高傳輸速率以及電路復(fù)雜性的增加,使得如果設(shè)計(jì)不合理,IC將會(huì)產(chǎn)生較大的電磁發(fā)射和傳導(dǎo)發(fā)射,同時(shí)抗擾動(dòng)能力也會(huì)下降,致使現(xiàn)代電子產(chǎn)品將無法滿足EMC要求,這也是當(dāng)前集成電路設(shè)計(jì)工程師們所面臨的難題:要求集成電路既具有低的電磁發(fā)射,又具有高的抗干擾能力。根據(jù)上述對集成電路設(shè)計(jì)所提出的要求,本文列出了下面幾種集成電路電磁兼容性設(shè)計(jì)方法。

3.1 降低集成電路電磁發(fā)射的設(shè)計(jì)方法

元件的電磁發(fā)射與制造工藝、封裝、開關(guān)門數(shù)、I/O口和數(shù)字同步核心模塊等的參數(shù)有關(guān)。減小電磁發(fā)射最重要的是要控制供電通路的阻抗,具體的措施如下。(1)減小寄生電感。(2)采用合適的電源策略。(3)增加去耦電容,已證明增加大的嵌入電容(1 nF~50 nF)可以有效地減小輻射發(fā)射。嵌入大電容的方法是:在最大耦合作用的每個(gè)電源和地環(huán)路的上方放置片上去耦電容,并且在布線通道下面的空間連上結(jié)電容,通常薄柵介質(zhì)電容或金屬-絕緣體-金屬電容可以產(chǎn)生大電容(幾納法)。(4)電源線、地線上增加小的串聯(lián)電阻。(5)核心電路模塊和I/O區(qū)分開,并獨(dú)立供電。(6)采用異步設(shè)計(jì)。來自數(shù)字電路的噪聲與該模塊是同步設(shè)計(jì)的本質(zhì)有關(guān),可以通過控制時(shí)鐘信號波形,擴(kuò)展頻譜來減小電路的電磁發(fā)射,另一種方法是集成電路核心模塊采用異步設(shè)計(jì),異步電路所產(chǎn)生的電磁輻射比同步電路要小得多。(7)仔細(xì)設(shè)計(jì)外部和芯片的版圖。例如,采用雙絞線的差分輸出信號產(chǎn)生的電磁發(fā)射(EME)較低,且不易受EME的影響。(8)直接在電路或封裝級采用吸收材料,比如采用鐵氧體,特別是頻率在300 MHz以上發(fā)射頻譜包絡(luò)可以減小3 dB~20 dB。

3.2 提高集成電路抗擾動(dòng)度的設(shè)計(jì)方法

提高集成電路的抗擾動(dòng)度,即減小集成電路的電磁易感性(EMS)。整流/泵、寄生元件、電流及功耗太大是EMS的4個(gè)最主要干擾效應(yīng)。將EMS效應(yīng)減到最小的主要辦法如下。(1)通過特殊的設(shè)計(jì)可以提高集成電路的抗擾動(dòng)能力,如施密特觸發(fā)器。(2)采用差分電路拓?fù)浜桶鎴D設(shè)計(jì)使電路設(shè)計(jì)勻稱,避免可能出現(xiàn)的整流現(xiàn)象。在頻率范圍為1 MHz~10 MHz,這種方法可以將電路的抗擾電平從1.5 V提高到5 V;(3)通過濾波限制進(jìn)入敏感器件的頻率范圍;(4)采取高共模抑制比(CMRR)和電源抑制比設(shè)計(jì)(PSRR)也可以使電路免受整流干擾,并保持內(nèi)部節(jié)點(diǎn)阻抗低且所有敏感節(jié)點(diǎn)都在片上。(5)采用保護(hù)器件將大于所要求的EMS抑制電平的部分鉗位掉是很重要的。(6)異步電路、增加片上電容也可以改善電路的抗擾度[6]。

對于微電子學(xué)行業(yè)來說,集成電路電磁兼容性的描述已經(jīng)成為一個(gè)非常重要的主題。實(shí)際上,如果不對集成電路電磁輻射及抗擾度方面進(jìn)行深入研究,就很難滿足電子設(shè)備電磁兼容性方面的要求。隨著工作頻率及芯片復(fù)雜度的不斷增加,具有低電磁輻射和高抗干擾度的集成電路設(shè)計(jì)研究具有非常重要的意義。

-

集成電路

+關(guān)注

關(guān)注

5381文章

11381瀏覽量

360850 -

電磁兼容

+關(guān)注

關(guān)注

54文章

1845瀏覽量

97804

原文標(biāo)題:干貨 | 集成電路的電磁兼容性分析與設(shè)計(jì)研究

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

系統(tǒng)的電磁兼容性分析模型及設(shè)計(jì)方法

集成電路的電磁兼容測試概述

電磁兼容性分析的方法

怎么提高電磁兼容性

提升電路板電磁兼容性的方法

混合集成電路電磁干擾產(chǎn)生的原因是什么

集成電路電磁兼容性標(biāo)準(zhǔn)與測試

通信開關(guān)電源的電磁兼容性

電磁兼容性定性測量方法

汽車電子電磁兼容性設(shè)計(jì)

一文看懂電磁兼容性原理與方法及設(shè)計(jì)

汽車設(shè)計(jì)中的電磁兼容性和集成電路IC問題解決方案

如何才能提高電磁兼容性有哪些方法

如何設(shè)計(jì)混合集成電路的電磁兼容

集成電路電磁兼容性設(shè)計(jì)應(yīng)遵循的原則和方法

集成電路電磁兼容性設(shè)計(jì)應(yīng)遵循的原則和方法

評論