一、原理圖網絡命名

原理圖網絡命名時,字母必須為大寫字母,不可以使用字母“O”;可以使用下劃線和左斜線“/”;禁止使用小寫字母、短橫線、*等;

電源網絡命名建議:10V以上命名舉例,12V、36V等,數字在字母V前;10V以下電源命名舉例,V33或者3V3、V18或者1V8、V09或者0V9;模擬電源命名舉例,V33_AVDD_FPGA或者3V3_AVDD_FPGA ;可以增加后綴說明電源使用對象;

時鐘網絡命名規則:時鐘網絡命名以CLK開頭,后接頻率,可以增加使用對象說明,舉例 CLK_50M_CPU;

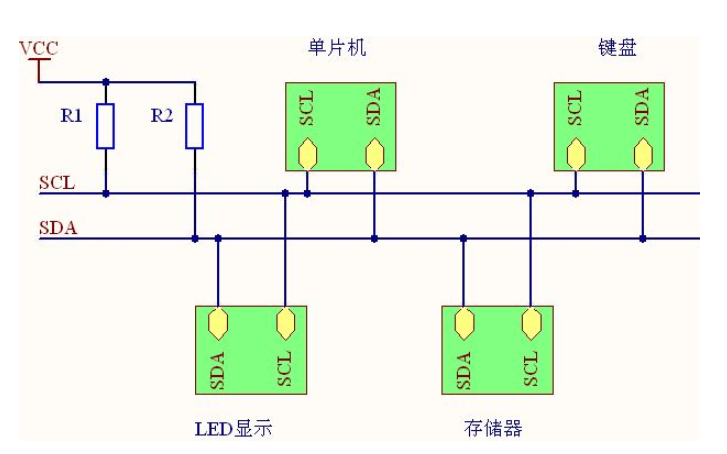

總線網絡命名規則:總線類型開頭,后接使用對象或者總線方向,舉例 SGMII_CPU_PHY、JTAG_TDI_CPU、PCIE_CPU_FPGA、IIC_SCL_EEPROM等;

使能網絡命名中包含EN,中斷網絡命名包含INT;

低有效信號命名規則,以“/”開頭,例如 /RST_CPU、/INT_PHY、/SPI_CS 等;

指示燈信號命名規則,以LED開頭,增加功能說明,舉例 LED_CPU_RUN、LED_CPU_ALARM、LED_FPGA_DEBUG、LED_V33 等;

差分信號命名規則,以P N表示差分信號的+ -信號,舉例 PCIE_CPU_FPGA_0_P、PCIE_CPU_FPGA_0_N,經過電阻、電容前或者后的信號,建議增加R C說明,舉例 PCIE_CPU_FPGA_0_C_P、PCIE_CPU_FPGA_0_C_N。禁止使用+ -符號表示差分信號;差分信號網絡必須全部標識,禁止使用自動生成網絡名稱;

二、原理圖圖表文字說明

對復雜器件的配置、上電啟動等要進行圖表說明。例如CPU的上電配置、PHY的地址配置等;

對開關或者有功能選擇通道的器件,需要增加圖表說明;

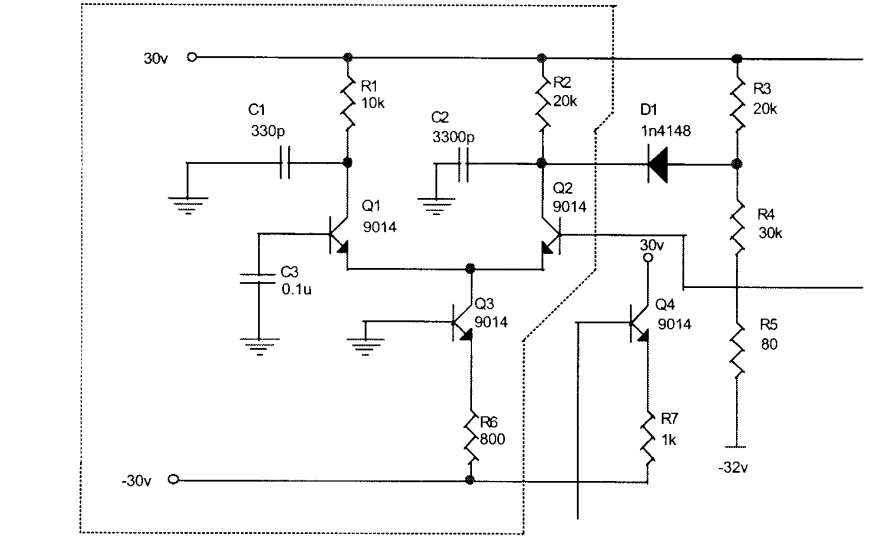

電源設計時,需要增加文字說明,例如輸出電壓公式、最大電流值,需求電流值;

電源限流設計時,需要增加文字說明,限流公式、限流大小、實際需要電流大小;

三、原理圖CBB化設計

原理圖設計時,對常用的功能模塊,建議進行CBB化,例如電源、CPU、PHY等器件;

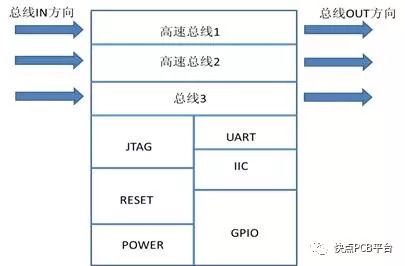

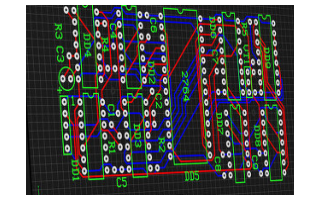

原理圖功能模塊CBB化時,總線IN的方向在左側,OUT的方向在右側,其他功能按區塊進行放置,舉例如下:

-

原理圖

+關注

關注

1293文章

6310瀏覽量

232929 -

硬件

+關注

關注

11文章

3252瀏覽量

66114 -

PHY

+關注

關注

2文章

301瀏覽量

51695

原文標題:盤他|硬件開發中原理圖設計規范

文章出處:【微信號:cn_maxwell,微信公眾號:快點PCB平臺】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

硬件原理圖設計規范

【設計規范】orcad原理圖

如何設計電路原理圖詳細設計規范說明

硬件開發的原理圖設計規范詳細說明

硬件開發的原理圖設計規范詳細說明

評論