我們在高速PCB設計當中,經常對高速信號線做特征阻抗控制來優化信號質量。那特征阻抗是什么東西呢?

1.傳輸線原理

介紹特征阻抗之前,我們復習下《信號完整性視頻》介紹的傳輸線基本原理。如下圖左邊是低頻電路采用集總參數的RLGC模型,右邊高頻電路采用分布參數的RLGC模型。

求解傳輸線微積分方程對你們來說都是輕輕松松的事情,這里同樣不介紹。方程的結果是我們可以得到PCB傳輸線的衰減常數,特征阻抗,相移常數等。具體含義的在《信號完整性視頻》有詳細介紹。我們這里主要介紹PCB特征阻抗的應用。下面就是求解方程得到的特征阻抗的公式,但用處不大,因為你無法知道單位長度對應的R,L,G,C。

2.特征阻抗不匹配的影響

傳輸線的特征阻抗是指高速信號在PCB線上傳輸時,在線上每個點處對應的阻抗。我們希望傳輸線特征阻抗不要突變,因為突變的的傳輸線會造成信號的反射,從而影響了信號質量。

3.特征阻抗的選值

PCB特征阻抗阻值是由負載端匹配電阻ZL決定,具體要看各種接口的規范定義。特征阻抗誤差主要是由PCB板廠工藝影響,一般能控制在5%-10%。下面是常見的接口PCB阻抗控制。

USB差分線90Ω

PCIE差分線100Ω

RF單端傳輸線50Ω

普通單端傳輸線 50Ω

4.PCB特征阻抗設計

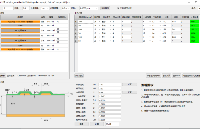

目前PCB生產廠家經常使用polar si9000軟件來計算特征阻抗。下面以單端信號線為例。設置參數有4個:介電常數、介質厚度、線寬和銅箔厚度。

介電常數Er1:板材的介電常數,一般FR4板材4.2-4.5。

介質厚度H1:板材或PP的厚度。

線寬W1/W2:PCB布線的線寬。

銅箔厚度:根據實際情況,有0.5/1/2 OZ等。

從上面50Ω單端信號線的例子計算大家應該清楚可以知道,為什么2層板的信號線很難做50Ω阻抗匹配?

5.特征阻抗OK就OK了嗎?

通過上面的原理介紹和軟件操作,大家基本上能輕輕松松設計出特征阻抗匹配的PCB。

但大家回顧下《PCIE 3.0仿真視頻》的例子,評估傳輸鏈路的關鍵指標主要有S11和S21。特征阻抗匹配只保證了S11。而對于長距離,GHZ以上的PCB布線,S21的影響更重要。所以在保證特征阻抗的同時,讓S21也滿足要求,才能說明你的PCB設計是OK的。

-

PCB設計

+關注

關注

394文章

4670瀏覽量

85294 -

華強pcb線路板打樣

+關注

關注

5文章

14629瀏覽量

42983

發布評論請先 登錄

相關推薦

PCB阻抗匹配過孔的多個因素你知道哪些?

PCB阻抗設計12問,輕松帶你搞懂阻抗!

高速pcb的定義是什么

深度論證-高速走線控制100歐姆阻抗一定是最好的選擇嗎?

PCB設計阻抗不連續的原因及解決方法

pcb阻抗測試方法有哪些 影響PCB阻抗的六大因素

PCB阻抗線怎么走線?多層PCB阻抗線走線技巧分享

高速PCB的特征阻抗怎樣來設計

高速PCB的特征阻抗怎樣來設計

評論