當面對一個項目計劃時,你最后一次聽到“需要多長時間就花多長時間”或者“如果第一次不成功,不要擔心,你總能搞定的”這些話大概是什么時候的事?很可能從來就沒有過。隨著FPGA變得越來越強大,處理的任務范圍也越來越廣,縮短設計周期并且最小化風險變得前所未有的重要。

Pentek公司作為一家商用現(xiàn)貨(COTS)FPGA的數(shù)據(jù)處理和采集產品制造商,通常是FPGA技術與最終用戶應用之間的接口。這使得Pentek處于支持客戶作為工程合作伙伴的獨特位置,其最終共同目標是解決他們的最終需求。 Pentek已經學到了很多關于如何縮短設計周期和最小化客戶風險的知識。 以下是Pentek及其客戶發(fā)現(xiàn)的有價值的一系列策略。

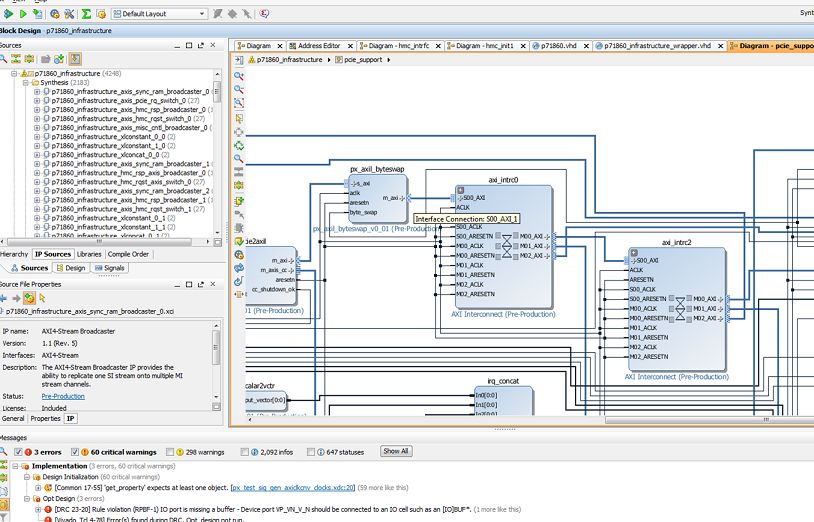

1. 利用FPGA設計工具Pentek公司推出的每一款基于FPGA的產品交付時都附帶一整套功能包,作為IP來進行安裝。盡管這些產品可以直接用來實現(xiàn)數(shù)據(jù)采集和處理的解決方案,但是大多數(shù)用戶都會安裝自己自定義的IP來進行特定應用的處理。Pentek公司推出的FPGA設計工具集搭配Zynq UltraScale+ RFSoC會提供所有生產用的IP以及一些通用功能的IP庫,用戶在搭建自己設計時可以用到。這些IP集成模塊可以輕松的導入Xilinx Vivado設計工具,所有IP都支持AXI4協(xié)議并且可以無縫對接Xilinx提供的IP資源。這可以讓我們快速訪問整個設計,不用再去學習新的工具或者了解IP設計定義,從而節(jié)省了項目啟動時間。

圖1:利用Xilinx和Pentek向導模塊組合開展的FPGA設計

2. 使用廠家提供的IP功能雖然每個用戶的設計都是不同的,但是所需的許多功能都是相似的,每一款硬件產品所提供的IP不僅支持硬件特性,比如A/D轉換板卡的數(shù)據(jù)采集或者D/A轉換板卡的波形發(fā)生器,而且還支持一些比較常見的高級功能,原本這些功能可能是由硬件來處理的。Pentek公司推出的基于Zynq UltraScale+ RFSoCs的產品支持以下功能庫:? 數(shù)據(jù)采集用于抓取和傳輸A/D數(shù)據(jù)? 波形生成,將數(shù)據(jù)傳輸給D/A或者讀取存儲在內存中的波形數(shù)據(jù)? 用于雷達測試應用的雷達啁啾聲和信號發(fā)生器? A/D校正功能? 100GigE UDP引擎? DMA引擎用于高速數(shù)據(jù)流設計

在每種情況下用戶都可以通過編輯提供的VHDL源代碼來使用這些IP功能,在所有情況下從競爭的角度來看經過測試的IP加速了產品開發(fā)并且降低了風險。

3. 簡化從開發(fā)到部署的流程Pentek公司推出的Quartz系列采用的是Zynq UltraScale+ RFSoCs,而且都是基于QuartzXM,它是一款緊湊的模塊系統(tǒng),包括了Zynq UltraScale+ RFSoC所需的所有電路設計。

圖2:Model 6001 QuartzXM RFSoC模塊化系統(tǒng)

這個設計背后的想法很簡單:解決模塊電路設計和PCB方面面臨的最大挑戰(zhàn),并且保證Zynq UltraScale+ RFSoC最佳的模擬和數(shù)字性能。當這款模塊設計完成并且經過驗證,Pentek公司可以擴展為各種接口形式的模塊,比如PCIe和3U VPX。

圖3:Model 5950,3U VPX RFSoC模塊板卡(拆下蓋子顯示的是QuartzXM)

雖然以標準的形式提供這種設計非常重要,但是用戶所能看到的最大好處是可以在有限的空間或者不滿足標準形式應用部署Zynq UltraScale+ RFSoC。Pentek公司提供的工具集包含所需的電氣、機械和散熱設計指導,讓客戶能夠為QuartzXM設計自己的承載板卡。將如此多的功能封裝在QuartzXM模塊中,用戶可以從一款經過驗證的Zynq UltraScale+ RFSoC平臺開始,專注于更簡單的承載板卡設計。此外它還提供了一套標準的、低成本的、易于操作的原型開發(fā)流程,用戶可以根據(jù)自己情況選擇PCIe接口的Quartz模塊,或者使用3U VPX形式的模塊,還提供低成本的Model 8257開發(fā)模塊共用戶選擇。開發(fā)好應用程序IP和軟件之后,在需要時可以通過設計定制的載板將解決方案部署到系統(tǒng)中,因為這兩個系統(tǒng)的硬件核心是相同的,所有IP和軟件可以在不做任何更改的情況下從開發(fā)移植到部署系統(tǒng)中,所以這些設計技術都大大降低了風險,縮短了開發(fā)時間。

4. 提供工程師對工程師的支持方式,確保產品的成功即使提供最好的產品文檔也抵不上工程師對工程師的對話交流,這對于設計的整個周期可以最小化風險同時節(jié)省時間。Pentek公司推出的所有產品都提供免費的終身技術支持服務,如果出現(xiàn)問題客戶可以隨時聯(lián)系到Pentek公司的工程師。

設計周期時間和降低風險是整個項目過程中非常真實重要的一部分,盡管風險永遠是開發(fā)創(chuàng)新過程中固有的一部分,Pentek公司的態(tài)度是認為降低風險縮短設計周期與為客戶提供最高性能和創(chuàng)新產品是同等重要的事情。

-

FPGA

+關注

關注

1626文章

21665瀏覽量

601803 -

Xilinx

+關注

關注

71文章

2163瀏覽量

121000 -

Zynq-7000

+關注

關注

3文章

144瀏覽量

36792

原文標題:借助Zynq UltraScale+ RFSoCs縮短設計周期同時最小化風險

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發(fā)圈】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

安森美系統(tǒng)設計工具介紹

優(yōu)化 FPGA HLS 設計

晶振頻率、脈沖、時鐘周期與機械周期的關系

【《軟件開發(fā)珠璣》閱讀體驗】居安思危之風險

如何有效減少PCBA的打樣時間

FPGA開發(fā)如何降低成本,比如利用免費的IP內核

脈沖電源的三個主要參數(shù) 脈沖電源和直流電源區(qū)別

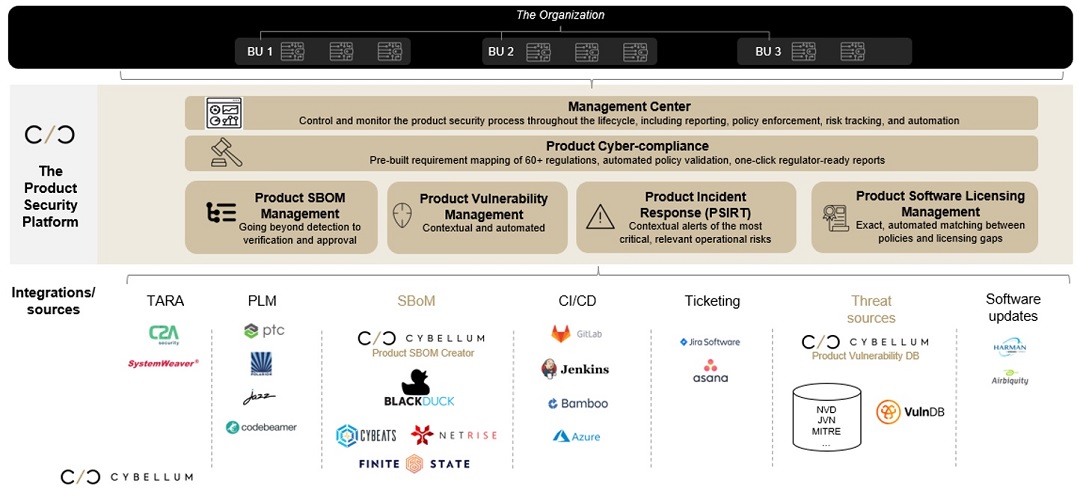

Cybellum—信息安全測試工具

減少靜電產生和降低擊穿風險的方法和材料

數(shù)字控制器IC利用黑盒工具和在線診斷大幅降低返修率

利用FPGA設計工具減少設計周期時間和降低風險

利用FPGA設計工具減少設計周期時間和降低風險

評論