2.5D異構和3D晶圓級堆疊正在重塑封裝產業。

堆疊:一種摩爾定律以外的高度集成替代方案

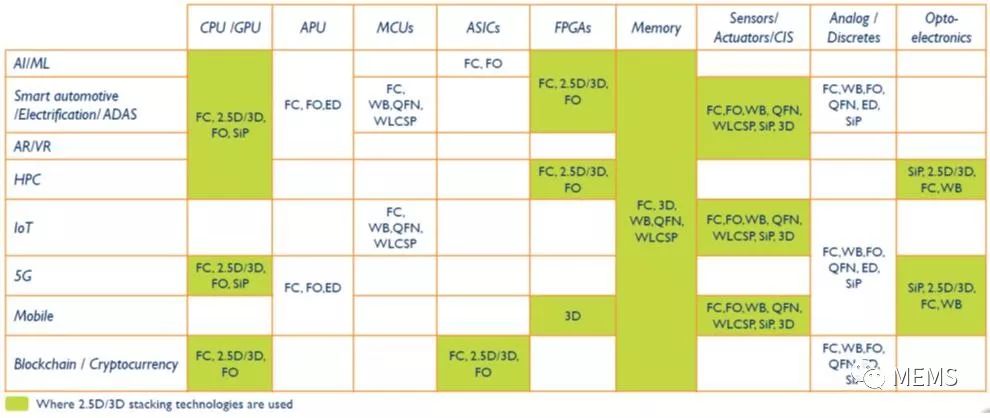

摩爾定律的放緩,為滿足行業大趨勢嚴格指標要求的新發明開辟了道路。在封裝領域,許多半導體廠商傾向于2.5D和3D堆疊技術,而硅通孔(TSV)是最早的堆疊技術之一。經過數年的發展和對MEMS的關注,它最終進入了許多應用領域。如今,2.5D和3D堆疊技術已成為能夠滿足當前人工智能(AI)和數據中心等應用性能需求的唯一解決方案。堆疊技術已被應用于高、中、低端市場的各種硬件,包括3D堆疊存儲、圖形處理單元(GPU)、現場可編程門陣列(FPGA)和CMOS圖像傳感器(CIS)等。

各種應用中先進堆疊封裝技術的市場機遇

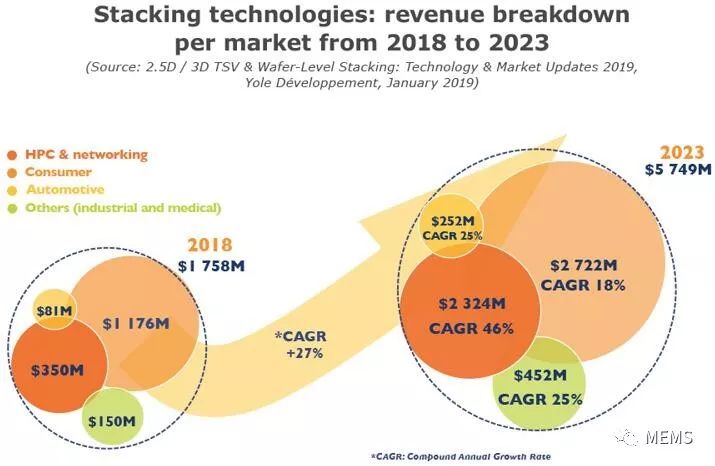

高帶寬存儲(HBM)和CMOS圖像傳感器等硬件占據了TSV市場的大部分營收。堆疊技術整體市場規模將在2023年超過55億美元,在此期間的復合年增長率(CAGR)可達27%。對于目前來說,消費類市場是最大的細分市場,其市場份額超過了65%。但矛盾的是,這并不意味著消費類市場就是這些技術的主要驅動因素。事實上,高性能計算(HPC)是堆疊技術的真正驅動因素,在2019~2023年期間將呈現最快的增長速度,市場份額預計將從2018年的20%增長到2023年的40%,就封裝營收而言,這相當于2018年營收的6倍以上增長。相應的,消費類市場份額將減少,而汽車、醫療和工業等其他市場將維持目前的市場份額。

2018~2023年按市場細分的堆疊技術營收

從TSV到晶圓級堆疊,封裝技術正在蓬勃發展

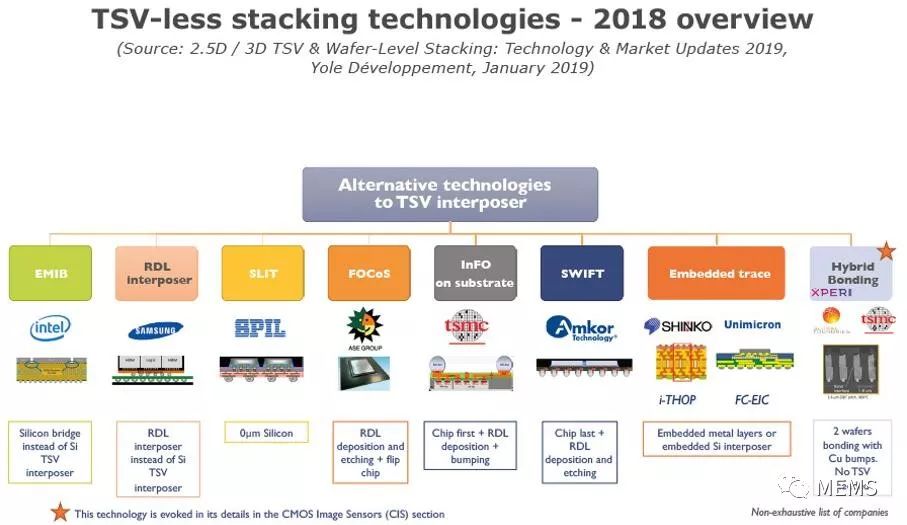

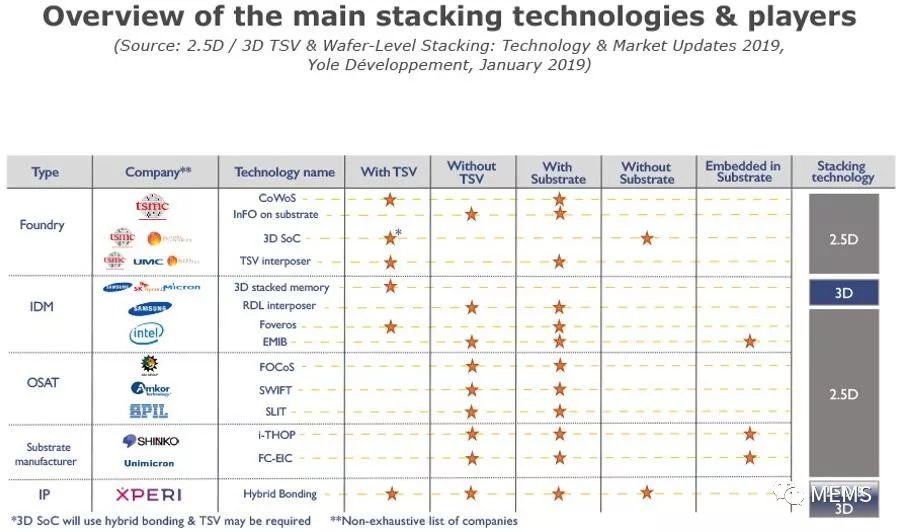

由于堆疊技術競爭主要集中在“TSV”和“無TSV(TSV-less)”之間進行,因此Yole在本報告中針對這兩類技術進行了分析。

對于目前的高端市場,市場上最流行的2.5D和3D集成技術為3D堆疊存儲TSV,以及異構堆疊TSV中介層。Chip-on-Wafer-on-Substrate(CoWos)技術已經廣泛用于高性能計算應用,新的TSV技術將于2019年上市,即來自英特爾(Intel)的Foveros(基于“有源”TSV中介層和3D SoC技術,具有混合鍵合和TSV互連(可能)技術)。Foveros的出現表明,雖然“TSV”受到了來自“無TSV”技術的挑戰,但廠商仍然對它很有信心。

我們不能忽視“無TSV”技術在市場上的興起。這些創新可以劃分為“帶基板型(with substrate)”和“嵌入基板(embedded in substrate)”兩組。嵌入式多芯片互連橋接(EMIB)技術已經商業化,是“嵌入基板”組的一種,其Si橋在基板中較深的位置。其他基板技術也正在開發中,但仍未上市,例如集成薄膜高密度有機封裝(I-THOP)和倒裝芯片-嵌入式中介層載具(FC-EIC)等。

左邊是業界標準2.5D封裝的芯片,右邊是英特爾EMIB封裝的芯片

圖片來源:《英特爾嵌入式多芯片互連橋接(EMIB)》

“帶基板型”技術也用于TSV替代,例如基板上集成扇出型封裝(InFO),它廣泛用于蘋果公司(Apple)的處理器。此外,再分配層(RDL)中介層技術目前正在開發中,預計將在2020年上市。最后同樣需要注意的是,基板上扇出型芯片(Fan Out Chip on Substrate, FOCoS)于2016年開發并商業化,但似乎訂單并不多。

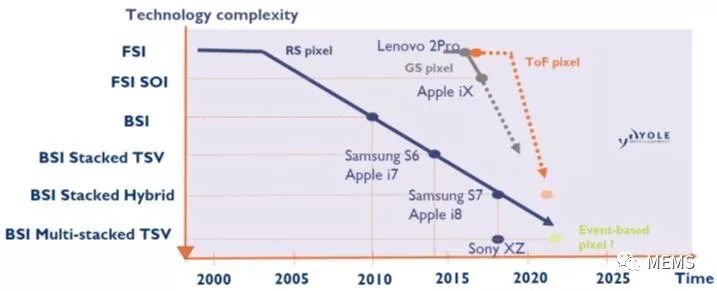

堆疊技術賦能的CMOS圖像傳感器發展路線圖

混合鍵合技術可以橋接“TSV”/“無TSV”這兩個主要技術類別。這項技術的獨特之處在于它可以同時成為TSV技術的挑戰者和支持者。自2016年以來,它一直被用于智能手機的CMOS圖像傳感器,并且在不久的將來,它將作為一種互連解決方案整合存儲和2.5D高端市場。

2018年“無TSV”堆疊技術概覽

誰在支持并投資堆疊技術?

各類不同的市場參與方都希望在不斷增長的55億美元堆疊市場中占有一席之地,目前主要有四種商業模式在堆疊業務領域參與競爭:代工廠、集成器件制造商(IDM)、外包半導體封測廠商(OSAT)和IP廠商。

據麥姆斯咨詢介紹,臺積電(TSMC)、聯華電子(UMC)和格芯(GlobalFoundries)等晶圓代工廠,主導了TSV異構堆疊技術,因為它們有能力自己生產中介層。擁有“Foveros”技術的英特爾,是唯一一個試圖在這個領域參與競爭的IDM。

對于3D堆疊存儲,競爭主要在IDM“三巨頭”三星(Samsung)、SK海力士(SK Hynix)和美光(Micron)之間,這些公司將繼續統治堆疊存儲市場。

同時,3D SoC是一種代工技術,很可能只有一家代工廠會生產它,以確保高良率并控制風險。在這方面,臺積電在上市時間的競爭中領先于格芯。

對于“無TSV”技術,競爭主要存在于代工廠、IDM、OSAT和基板制造商之間。三星、英特爾和臺積電等廠商,都參與了“有”和“沒有”TSV技術的開發。2016年,OSAT巨頭日月光(ASE)向市場引入了FOCoS技術,而安靠(Amkor)等其他廠商也已經開發出了合適的技術,但仍然在等待訂單中。

日本新光(Shinko)、欣興電子(Unimicron)以及最近的富士通互連科技(Fujitsu Interconnect)等基板公司,仍然在研發中。IP廠商Xperi的混合鍵合技術處于“有TSV”和“無TSV”技術之間,預計將對市場產生積極影響。Xperi的另一個優勢是其技術兼容高端和中/低端細分市場。

代工廠、IDM和IP廠商相比OSAT在堆疊技術方面有優勢,因為后者在獲得訂單方面有困難。

主要堆疊技術及廠商概覽

-

摩爾定律

+關注

關注

4文章

632瀏覽量

78938 -

圖像傳感器

+關注

關注

68文章

1886瀏覽量

129464 -

堆疊

+關注

關注

0文章

33瀏覽量

16578

原文標題:《2.5D/3D硅通孔(TSV)和晶圓級堆疊技術及市場-2019版》

文章出處:【微信號:MEMSensor,微信公眾號:MEMS】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

用于扇出型晶圓級封裝的銅電沉積

2.5D/3D芯片-封裝-系統協同仿真技術研究

日本計劃量產2nm芯片,著眼于2.5D、3D封裝異構技術

3D封裝結構與2.5D封裝有何不同?3D IC封裝主流產品介紹

2.5D異構和3D晶圓級堆疊正在重塑封裝產業

2.5D異構和3D晶圓級堆疊正在重塑封裝產業

評論