在智能機性能越來越強悍的今天,最核心的處理器就變得尤為重要。其實從上世紀70年代起,處理器發展的速度就沒有停下來過,從最初的180nm工藝到現在的14nm、7nm工藝,可以說制作工藝的進步帶給了CPU更多進化的可能。

然而到了7nm以后,很多在 1Xnm大放異彩的半導體公司都在7nm制程處遭遇到了苦頭,AMD御用代工廠商GF宣布無限期延期7nm制程工藝,英特爾的10nm制程更是跳票到2019年。目前僅剩下的7nm工藝也只有臺積電能夠在現階段實現量產。今天與非網小編就來與大家探討一些關于7nm工藝制程的問題。

也許有的看官還云里霧里,等會兒,先告訴我這個XX nm到底是啥意思?別急,下面就來說了。

XX nm制造工藝是什么概念?芯片的制造工藝常常用90nm、65nm、40nm、28nm、22nm、14nm來表示。現在的CPU內集成了以億為單位的晶體管,這種晶體管由源極、漏極和位于他們之間的柵極所組成,電流從源極流入漏極,柵極則起到控制電流通斷的作用。

所謂的XX nm其實指的是,CPU上形成的互補氧化物金屬半導體場效應晶體管柵極的寬度,也被稱為柵長。

柵長越短,則可以在相同尺寸的硅片上集成更多的晶體管——Intel曾經宣稱將柵長從130nm減小到90nm時,晶體管所占面積將減小一半;在芯片晶體管集成度相當的情況下,使用更先進的制造工藝,芯片的面積和功耗就越小,成本也越低。

柵長可以分為光刻柵長和實際柵長,其中光刻柵長是由光刻技術所決定的。

由于在光刻中光存在衍射現象以及芯片制造中還要經歷離子注入、蝕刻、等離子沖洗、熱處理等步驟,因此會導致光刻柵長和實際柵長不一致的情況。

另外,同樣的制程工藝下,實際柵長也會不一樣,比如雖然三星也推出了14nm制程工藝的芯片,但其芯片的實際柵長和Intel的14nm制程芯片的實際柵長依然有一定差距。

實現7nm制程工藝為什么這么困難?在討論7nm制程難度的時候,我們需要普及一個量子力學上的概念,這樣子可以有助于我們理解為什么低制程的成本急劇提升,那就是量子隧穿效應。

在量子力學里,量子隧穿效應指的是,像電子等微觀粒子能夠穿入或穿越位勢壘的量子行為,盡管位勢壘的高度大于粒子的總能量。在經典力學里,這是不可能發生的,但使用量子力學理論卻可以給出合理解釋。

如果通俗點來講,就是說制程工藝到一定程度下,電路與電路之間的距離降低到一定程度就會出現量子隧穿效應,這些電子呈現的是一種我們所不知道的規律進行運動,于是這些不可控制的電子造成了半導體的漏電率急劇上升,有太多的能源被浪費在控制電子運動上,自然不能發揮晶體管應該有的性能,宏觀上表現為處理器的發熱量增加,但是性能沒有太大的變化。

然后我們再來討論一下現階段有哪些存在的問題:

首先從本質上來說,7nm已經是物理極限。縮短晶體管柵極的長度可以使CPU集成更多的晶體管或者有效減少晶體管的面積和功耗,并削減CPU的硅片成本。

正是因此,CPU生產廠商不遺余力地減小晶體管柵極寬度,以提高在單位面積上所集成的晶體管數量。

不過這種做法也會使電子移動的距離縮短,容易導致晶體管內部電子自發通過晶體管通道的硅底板進行的從負極流向正極的運動,也就是漏電。而且隨著芯片中晶體管數量增加,原本僅數個原子層厚的二氧化硅絕緣層會變得更薄進而導致泄漏更多電子,隨后泄漏的電流又增加了芯片額外的功耗。

其次,工藝的精度已經趨近于傳統***的極限,極紫外***還無法用于大規模量產。傳統***的波長為193nm,通過浸液的方式可以使波長進一步縮短,再加上多次曝光的輔助,已經走到了14nm。可是到了7nm,這種方法光刻出來的線條誤差越來越大,越來越難以控制。我們可以通過下圖對比傳統***和極紫外***的實際效果圖,可以看出,傳統光刻的方法誤差確實很大。這種情況下,想要良率滿足要求是極為困難的。

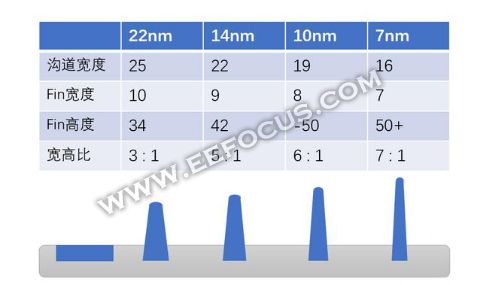

線寬逼近極限帶來的電阻電容增大變得不可忽視,我們知道同樣材質的前提下,越細的導線電阻越大。因此當工藝進入7nm,線上電阻已經變得非常大,Intel不得已采用貴技術釕來解決這個問題。除此之外,由于FinFET的Fin越來越小,控制其流過的電流也越來越困難。因此,不得已采用了增加Fin的高度來增強控制,可是這樣又帶來晶體管的電容更大從而速度變慢。下圖展示了不同工藝的晶體管的各種參數,可以看出隨這工藝升級,Fin的寬高比越來越大。

EDA工具支持的支持尚不完善,雖然每代工藝都會遇到此類問題,但是14nm/7nm工藝恰逢EDA工具尤其是后端設計工具更新換代,兩個主流軟件廠商均發布了所謂的次世代EDA工具。各種引擎的升級導致工具的bug數直線上升,而工藝帶來的的挑戰需要工具不斷升級并增加性的功能,助長了工具開發和使用方面的挑戰。

設計上的難度大幅增加,各個芯片設計公司希望通過工藝升級獲得更高的性能,更低的功耗和更小的芯片面積。可是7nm在設計方面提出了更高的挑戰。為了滿足工藝廠商的生產規則,在設計階段增加了大量的硬性規則,給芯片設計尤其是后端設計增加的很大難度。比如使用金屬層上,對于底層金屬,幾乎是只能按照特定的pattern和方向使用,變通性大大降低。

7nm擂臺,參與者僅剩三家

目前還在追求7nm制程工藝的廠商僅剩臺積電,英特爾以及三星三家廠商。芯片代工講究的是規模效應,前期投入的資金需要通過大量的芯片來平攤巨額的研發成本,同時芯片代工行業也是一個商業行為,企業追求是利潤,如果沒有利潤,賠本的買賣相信大家都不愿意長期干下去。

在這個贏者通吃的行業中,像臺積電憑借著率先實現的7nm工藝獲得了大量的訂單,而AMD也已經宣布未來的Zen 2和Navi顯卡將會讓臺積電進行代工,海量的訂單滿足了臺積電的7nm胃口,自然可以分攤巨額研發費用,同時還能賺取大量的利潤進行更進一步的制程工藝中來,這種良性循環也讓臺積電的財報節節攀升。

作為擁有完整IC設計的三星和英特爾自然擁有大量的芯片需求來滿足自己的芯片代工行業。即使沒有代工,他們同樣可以自主滿足7nm工藝制程的產能。

而其他的芯片代工企業恐怕就過得不那么舒服了,例如格羅方德先進制程制造公司,沒有了AMD最新的Zen 2以及Navi顯卡的訂單,自然推廣7nm制程的動力就小了很多。沒有訂單也沒有利潤,導致沒有足夠的研發資金投入到先進制程工藝的研發中去。這樣周而復始,自然也就退出了芯片行業的競爭中來。而整個芯片行業也伴隨著門檻的提升處于寡頭化的情形,除非有黑科技大幅降低先進制程的制造成本,玩得轉現在和未來芯片代工的最終還是那幾個科技巨頭。

三大巨頭的7nm制程現狀

據悉,臺積電預計將在2019年3月底開始量產7nmEUV工藝,EUV全稱Extreme Ultraviolet Lithography,也就是極紫外光刻。此舉將推動臺積電的7nm芯片總銷量占比提升至25%。同時消息人士指出,臺積電有望在2019年第二季度開始5nm風險試產,值得一提的是,5nm的整個代際都將基于EUV工藝部署。臺積電首席執行官CC Wei此前也透露,預計將在2019年上半年流片5nm,并在2020年上半年量產。

為與臺積電一較高下,三星 7nm 不走尋常套路,也就是像臺積電所選擇的作法,使用 DUV機臺,但通過多重曝光的方式搞定,后期再導入 EUV 機臺來降低成本并提高性能。三星一開始就會導入 EUV ,目標是把 7nm工藝的成本控制一步到位,創造更好的市場誘因。

然而 EUV 機臺的調整難度極高,三星雖然前些時候宣布有所突破,但2018年主要還是試產,自家 7nm Exynos 方案雖有機會在 2018 年底提早量產,但因為預期良率低,肯定還是滿足不了自家手機的需求,因此還是有一大部分的芯片必須求助高通,而高通此時與蘋果幾乎同時搶進臺積電的產能,相較于三星的窘迫,憑借臺積電的優秀良率與產能布局,對三星和其他客戶的需求也就更能從容應付。

根據三星高管所說,他們在2019年下半年會量產7nm EUV工藝,2021年則會量產更先進的3nm GAA工藝。

而牙膏廠英特爾,目前10nm工藝還沒量產,要到今年底才能首先出貨移動版10nm冰湖處理器,2020年才有可能大規模量產桌面版、服務器版,但是下下代7nm EUV工藝會吸取10nm工藝上的教訓,不會盲目追求高指標,量產進度會比10nm更順利(希望如此),而工廠建設、設備安裝調試需要兩三年的時間,英特爾的7nm EUV工藝量產要到2021-2022年才有可能了。

目前在制造工藝上,中國與世界先進工藝節點依然存在較大差距。對于現在的中國半導體產業而言,是花費巨大人力物力財力去探索突破7nm物理極限,還是將現有工藝實現量產是值得鄭重考慮的問題。在與非網小編看來,相對于耗費大量資源去研發新材料突破7nm物理極限,還不如腳踏實地地解決現實問題。

-

cpu

+關注

關注

68文章

10829瀏覽量

211193 -

晶體管

+關注

關注

77文章

9641瀏覽量

137876 -

制程工藝

+關注

關注

0文章

43瀏覽量

9426

原文標題:在7nm以后的世界,誰在盡頭等你?

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

XX nm制造工藝是什么概念?實現7nm制程工藝為什么這么困難?

XX nm制造工藝是什么概念?實現7nm制程工藝為什么這么困難?

評論