By Cliff Zitlaw, Cypress

作者:Cliff Zitlaw,賽普拉斯

NOR閃存已作為FPGA(現場可編程門列陣)的配置器件被廣泛部署。其為FPGA帶來的低延遲和高數據吞吐量特性使得FPGA在工業、通信和汽車ADAS(高級駕駛輔助系統)等應用中得到廣泛采用。汽車場景中攝像頭系統的快速啟動時間要求就是很好的一個例子——車輛啟動后后視圖像在儀表板顯示屏上的顯示速度是最為突出的設計挑戰。

上電后,FPGA立即加載存儲于NOR器件中的配置比特流。傳輸完成后,FPGA轉換為活動(已配置)狀態。FPGA包括許多配置接口選項,通常包括并行NOR總線和串行外設接口(SPI)總線。支持這些總線的存儲器在不同廠商的產品之間總是存在微小的不兼容性,增添了采購多款存儲器件的困難程度。

全新發布的JEDEC xSPI規范由各大主要NOR閃存廠商聯合制定。新標準結束了數十年來NOR閃存廠商獨立開發產品、各自為政的局面。雖然存在細微差別,但目前各廠商產品的核心JEDEC xSPI功能已完全相同。JEDEC xSPI規范對總線事務、命令和大量內部功能進行了標準化。結合高吞吐量這一性能,這些下一代閃存可實現全新的應用和功能。例如,賽普拉斯Semper NOR Flash系列符合JEDEC xSPI規范,并提供持續400MB /s讀取傳輸速率,非常適合作為FPGA配置存儲器。具體而言,憑借400MB/s的數據速率,容量為128MB(1Gb)的器件,其內容可在320ms內完成傳輸。

FPGA配置歷史回顧

當FPGA首次面世時,可選擇的配置存儲器是并行EPROM或并行EEPROM產品。隨著時間的推移,NOR閃存技術應運而生,同時因其系統內可重復編程性和高性價比而被廣泛采用。在第二次革命性轉折中,SPI存儲器接口在大多數應用中取代了并行NOR接口。今天的SPI存儲器產品具有高密度、小封裝尺寸和高讀取吞吐量,以及最重要的特點——更高效的低引腳數接口。

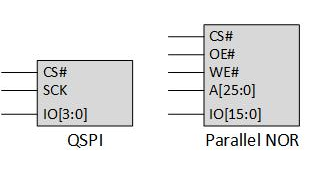

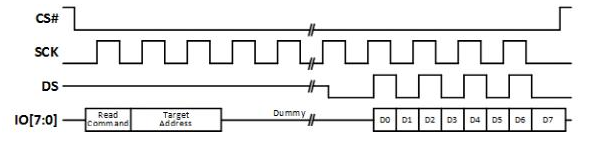

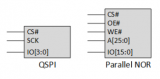

圖1 - 千兆位四路SPI(6引腳)和并行NOR(45引腳)接口

圖1顯示了千兆位SPI器件與千兆位并行NOR的引腳分配的對比。對于一個千兆位存儲器,四路串行外設接口(QSPI)器件具有六引腳接口,而并行NOR器件則需要45個引腳。引腳數量的巨大差異導致QSPI器件作為首選配置接口而被廣泛采用。QSPI接口允許在不改變器件占用空間的情況下更改密度。

FPGA配置速度

隨著工藝節點縮小,FPGA器件得以繼續增加可用的可編程邏輯模塊數量,進而導致對更高密度和更快速度配置存儲器的需求。現代FPGA在配置期間需要加載多達128MB的數據。這些高密度配置比特流需要更長的時間才能從NOR閃存器件傳輸到FPGA。配置接口不僅針對讀取吞吐量進行了優化,還專注于促進不同NOR閃存制造商之間的互操作性。

SPI讀取吞吐量

過去幾年,從最初以x1模式運行的SPI接口開始,一直到以x4 DDR模式運行的現代QSPI產品,SPI讀取吞吐量發生了顯著增長。從表1可以看出,下一代閃存器件能夠推動SPI總線性能實現又一次躍遷。

表1 - 閃存器件SPI讀取吞吐量選項

現代SPI器件能夠永久配置為固定的總線寬度和傳輸類型,可在上電時立即運行。FPGA須支持這一永久配置,以便在上電后立即啟動配置過程。

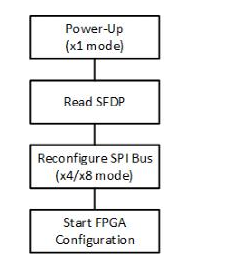

又或者,SPI存儲器可在x1模式下退出通電狀態,從而允許主機系統(FPGA)查詢存儲器中的串行閃存可發現參數(SFDP)表中的特性。這一x1模式已成為多家存儲器廠商支持的標準功能,并允許FPGA檢索有關器件功能的關鍵信息。一旦檢索到器件特性,就可以快速重新配置FPGA存儲器控制器和SPI存儲器器件,以獲得最大的讀取性能。

圖2 - 通電時使用串行閃存可發現參數(SFDP)表配置SPI總線功能

在選用可使用x1、x4或x8總線寬度以及SDR或DDR傳輸類型運行的下一代閃存設備時,使用集成SFDP表檢索關鍵設備信息將格外重要。所選擇的總線寬度和傳輸類型必須與FPGA上實現的總線接口基礎設施保持一致。

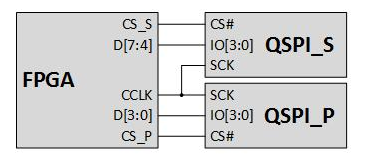

雙QSPI配置接口

為減少FPGA配置時間,許多現代FPGA允許將配置位流分區至兩個QSPI器件(圖3)。這兩個QSPI器件以并行方式連接,其中位流的低半字節存儲在“主”QSPI器件(QSPI_P)中,位流的高半字節存儲在“輔助”QSPI器件(QSPI_S)中。這兩個器件在加載位流時并行運行,從而有效地使讀取數據傳輸速率提升一倍。

請注意,除共享SCK(串行時鐘)線以外,接口在兩個器件上基本上是獨立的。之所以要共享SCK線,是為了在以并行方式(即同時)讀取器件時實現時序偏差最小化。當使用相同目標地址執行相同操作時,可以一次僅對一個器件進行訪問,也可以同時對兩個器件進行訪問。

圖3 - 雙QSPI配置接口(11個引腳)允許配置位流在兩個QSPI器件之間進行分區,從而有效地將讀取數據傳輸速率提升一倍。

當大型FPGA器件需要以最快的方式傳輸大配置(即高密度)配置比特流時,這種11引腳雙QSPI配置將具有非常大的優勢。

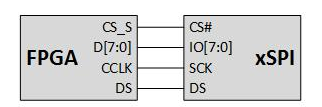

閃存配置

下一代閃存采用x1(主要用于SFDP訪問)、x4或x8 IO總線寬度運行,支持SDR或DDR格式傳輸數據,并且通過使用新的數據選通(Data Strobe)信號以促進高速傳輸。例如,使用11引腳接口的賽普拉斯Semper NOR閃存八進制配置(圖4)。

圖4 - 低引腳數接口支持SDR或DDR格式的x1、x4或x8 IO總線寬度傳輸數據。圖中顯示的是采用11引腳接口的賽普拉斯Semper NOR閃存八進制配置。

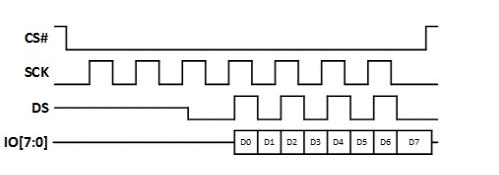

這一新的數據通選必須結合到FPGA配置接口中,從而可利用下一代閃存器件的高吞吐量讀取性能。數據選通與輸出讀取數據邊緣對齊,其方式與低功耗DDR DRAM器件上的選通方式相同(圖5)。數據選通“繪制”數據眼圖,并允許FPGA以高時鐘頻率有效抓取數據。

圖5 - 具有數據選通功能的x8 DDR讀取事務與輸出讀取數據邊緣對齊,使FPGA能夠以高時鐘頻率有效抓取數據。

支持連續讀取操作是非常適用于FPGA配置的閃存功能之一。連續讀取始于主機(MCU(微控制器)或FPGA)置位CS#(CS片選引腳),然后發出讀取命令,后跟目標地址。經過多次延遲周期,存儲器從目標地址輸出數據。如果主機繼續切換時鐘,則存儲器將通過從下一個順序地址輸出數據來響應。只要時鐘繼續切換,存儲器將繼續從順序地址輸出數據。這種順序讀取功能可以允許FPGA配置單個讀取事務。

AutoBoot(自動啟動)是另一項有助于FPGA配置的功能。AutoBoot在通電復位期間從預先配置的目標地址執行自動讀取,然后在第一次CS#置位時立即輸出數據(圖6)。此功能對需要簡單配置機制的ASIC(專用芯片)器件也十分有用。一旦CS#解除置位,內存將返回其待命狀態,并以正常方式處理后續操作。

圖6 - 運行中的AutoBoot讀取功能(具有3個預熱周期)

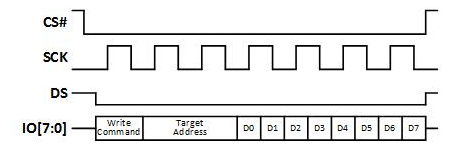

NOR 閃存器件的寫入事務(圖7)與標準SPI操作幾乎完全相同,但有兩點例外。首先,在整個事務期間必須將新的數據選通信號驅動為LOW(低電平)。其次,當配置為DDR操作時,數據被寫為字(16b),而非傳統SPI產品的字節寫編程粒度。

圖7- NOR 閃存的寫入事務需要在整個事務期間將數據選通信號驅動為LOW,并且在配置為DDR操作時將數據寫為16位字。

下一代NOR閃存器件可提供滿足大規模FPGA應用的高密度和隨開即用要求所需的高吞吐量。各大NOR閃存制造廠商都參與了JEDEC xSPI規范的開發,為代工廠商提供了廣泛的采購選擇。JEDEC xSPI規范涵蓋了上述八進制SPI接口以及HyperBus接口,兩者均提供400MB/s的讀取吞吐量,已實現的讀取吞吐量遠高于傳統SPI產品。為利用高速基礎設施,需要對FPGA SPI控制器進行修改。需要考慮的新功能包括DDR數據速率,用于數據抓取的新數據選通引腳和擴展的x8總線接口。此外,一些NOR閃存器件(例如賽普拉斯Semper NOR系列)允許在實施雙QSPI配置架構時消除其中一個QSPI器件。在需要進行快速FPGA配置的情況下,以及在執行實時重新配置的FPGA應用中,下一代閃存所提供的性能將具有強大的優勢。

關于作者:Cliff Zitlaw擁有長達36年的半導體存儲器開發經驗,重點關注可以實現在各類應用程序約束范圍內優化內存性能總線接口。Cliff是Xicor微處理器串行存儲器接口(EEPROM),美光科技(Micron)CellularRAM接口(PSRAM)和賽普拉斯Hyperbus接口(NOR和PSRAM)的發明者。 Cliff是49項與內存功能和用法相關的專利著作者或合著者。閑暇之余,Cliff喜歡燒烤,看電視,或在周六小睡片刻。

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602022 -

NOR閃存

+關注

關注

0文章

25瀏覽量

14576 -

賽普拉斯

+關注

關注

28文章

391瀏覽量

87661

發布評論請先 登錄

相關推薦

NOR閃存前景不妙,SPI NOR閃存困境獲勝

EEPROM和NOR閃存之間的差異

如何連接FPGA和NOR并行閃存的2個實習引腳?

汽車應用怎么選擇NOR閃存?

串行SPI NOR閃存與并行NOR閃存之間的對比

使用STARTUPE3對并行NOR閃存進行配置后訪問的UltraScale FPGA應用說明

使用高速NOR閃存配置FPGA

使用高速NOR閃存配置FPGA

評論