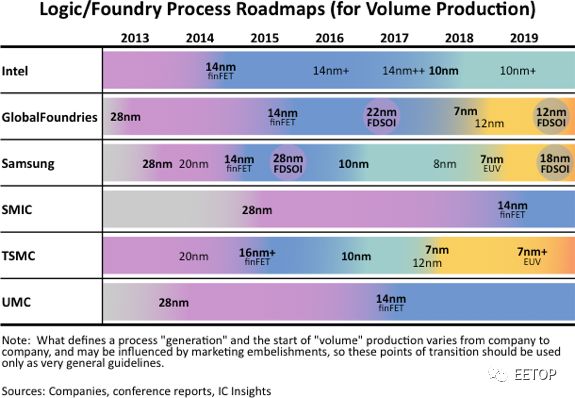

集成電路產業的發展取決于IC制造商是否有能力繼續為消費者提供更多的性能和功能。隨著主流CMOS工藝在理論、實踐和經濟方面的限制,降低集成電路的成本(按功能或按性能)比以往任何時候都更加關鍵和具有挑戰性。IC Insights 2019年版的McClean報告顯示,企業提供的面向邏輯的流程技術比以往任何時候都更加多樣化。圖1列出了公司目前使用的幾種領先的高級邏輯技術。主要節點之間的每個過程生成的衍生版本已成為常規事件。

主要晶圓廠的最新工藝進展:

其在2018年末發布的第九代處理器代號為“Coffee Lake-S”,有時也被稱為“Coffee Lake Refresh.”。英特爾表示,這些處理器是新一代產品,但它們似乎更像是對第8代產品的增強。細節尚不清楚,但這些處理器似乎是在14nm++工藝的增強版上制造的,或者可以認為是14nm++工藝。

英特爾將于2019年推動10nm工藝的大規模生產,首批使用這個工藝的產品將是2018年12月推出的“Sunny Cove”系列處理器。從目前看來,Sunny Cove架構基本上取代了應該是原本計劃在2019年推出的10納米Cannon Lake架構。預計到2020年,10nm +衍生工藝將進入批量生產階段。

臺積電

臺積電的10nm finFET工藝于2016年底投入批量生產,短短兩年間,他們已經從10納米迅速發展至7納米。在臺積電看來,7nm產品將成為繼28nm和16nm之后的又一個長壽命節點。

先進工藝方面,臺積電5納米工藝正在開發中,預計將于2019年上半年進入風險試產階段,并于2020年進入量產。該工藝將使用EUV,但它不會是臺積電利用EUV技術的第一個工藝。根據臺積電規劃,他們將在7nm技術的改進版本N7 +工藝的關鍵層(四層)上使用EUV***。但N5工藝將廣泛使用EUV(最多14層)。N7 +計劃于2019年第二季度開始批量生產。

在2018年初,三星宣布開始批量生產名為0LPP(low power plus)的第二代10nm工藝。在2018年晚些時候,三星推出了名為10LPU(low power ultimate)的第三代10nm工藝,從另一個角度實現性能提升。與臺積電不同的是,三星在10nm工藝上使用三重圖案光刻技術,且三星認為其10納米工藝系列(包括8納米衍生產品)的生命周期將會很長。

三星的7nm技術于2018年10月投入風險試產。與臺積電不一樣,三星不再提供采用浸沒式光刻技術的7nm工藝,而是決定直接上馬EUV的。據了解,三星該將EUV用于7nm的8-10層。

格芯

格芯公司將其22nm FD-SOI工藝視為其主要市場,并與其14nm finFET技術相輔相成。按照他們的說法,22FDX平臺的性能與finFET非常接近,但制造成本與28nm技術相同。

2018年8月,GlobalFoundries宣布將停止7nm開發。按照他們的說法,做出這個決定一方面是因為先進技術節點的生產成本大幅增加,另一方面是太少的代工客戶計劃使用下一代工藝,因此他們對其戰略進行了重大轉變。公司也調整了其研發工作,以進一步增強其14nm和12nm finFET工藝及其完全耗盡的SOI技術的競爭力。

SMIC

前中芯國際第一代FinFET 14nm工藝已經進入客戶驗證階段,產品可靠度與良率進一步提升,同時12nm工藝開發也取得突破。 根據媒體報道,中芯國際14nm工藝將在今年上半年投入大規模量產,良品率已高達95%。

五十年來,集成電路技術的生產力和性能有了驚人的提高。雖然這個行業已經克服了擺在它面前的許多障礙,但這些障礙似乎越來越大。盡管如此,集成電路設計人員和制造商正在開發的解決方案似乎更具革命性,而非漸進性,以增加芯片的功能。

-

芯片

+關注

關注

453文章

50417瀏覽量

421854 -

集成電路

+關注

關注

5381文章

11388瀏覽量

360878 -

臺積電

+關注

關注

44文章

5609瀏覽量

166127

原文標題:行業 | 主流代工廠芯片制造工藝的新進展

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

RFID天線主要有哪些制造工藝

新思科技針對主要代工廠提供豐富多樣的UCIe IP解決方案

概倫電子NanoSpice通過三星代工廠3/4nm工藝技術認證

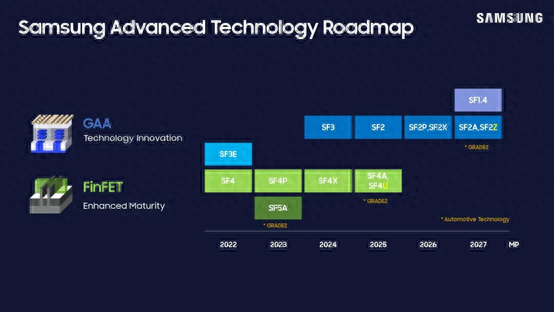

三星公布最新工藝路線圖

電機的制造工藝有哪些

美國純MEMS代工廠RVM宣布新建12英寸MEMS晶圓代工產線

2024年最新全球EMS代工廠50強(TOP 50)

Intel Foundry:2030成為全球第二大半導體制造代工廠!

英諾激光:光伏業務進展順利,消費電子業務以創新工藝提升競爭力

全球知名晶圓廠的產能、制程、工藝平臺對比

和碩集團擬在印度設立PC代工廠,響應政策鼓勵本土制造

無意發展至10nm以下,第二梯隊晶圓代工廠的成熟工藝現狀

主流代工廠芯片制造工藝主要晶圓廠的最新工藝進展

主流代工廠芯片制造工藝主要晶圓廠的最新工藝進展

評論