自20世紀(jì)80年代以來,數(shù)字信號(hào)處理算法和集成電路迅猛發(fā)展,雖然許多類型的信號(hào)處理已經(jīng)由模擬電路轉(zhuǎn)換成數(shù)字電路來實(shí)現(xiàn),但是在一塊芯片中,模擬電路是必不可少的。作為一個(gè)模擬電路設(shè)計(jì)師中的菜鳥,說一下自己學(xué)習(xí)和工作中的一些心得體會(huì)。

我從研究生開始接觸模擬集成電路到現(xiàn)在有四年了,有讀過“模擬芯片設(shè)計(jì)的四重境界”這篇文章,我現(xiàn)在應(yīng)該處于菜鳥的境界。

模擬電路設(shè)計(jì)和數(shù)字電路設(shè)計(jì)是有很大區(qū)別的,最基本的是模擬電路處理的是模擬信號(hào),數(shù)字電路處理的數(shù)字信號(hào)。模擬信號(hào)在時(shí)間和值上是連續(xù)的,數(shù)字信號(hào)在時(shí)間和值上是離散的,基于這個(gè)特點(diǎn),模擬電路設(shè)計(jì)在某些程度上比數(shù)字電路設(shè)計(jì)困難。模擬電路設(shè)計(jì)困難的具體原因如下:

1. 模擬設(shè)計(jì)需要在速度、功耗、增益、精度、電源電壓、噪聲、面積等多種因素間進(jìn)行折中,而數(shù)字設(shè)計(jì)只需在功耗、速度和面積三個(gè)因素間進(jìn)行平衡。

2. 模擬電路對(duì)噪聲、串?dāng)_和其他干擾比數(shù)字電路敏感得多。

3. 隨著工藝尺寸的不斷減小,電源電壓的降低和器件的二級(jí)效應(yīng)對(duì)模擬電路比數(shù)字電路的影響嚴(yán)重得多,給模擬設(shè)計(jì)帶來了新的挑戰(zhàn)。

4. 版圖對(duì)于模擬電路的影響遠(yuǎn)大于數(shù)字電路,同樣的線路差的版圖會(huì)導(dǎo)致芯片無法工作。

我的模擬集成電路設(shè)計(jì)學(xué)習(xí)之路是從拉扎維的模擬CMOS集成電路設(shè)計(jì)這本書開始,這本書在現(xiàn)在工作中還是會(huì)去查看,是模擬集成電路設(shè)計(jì)的經(jīng)典教材之一。我首先想談的就是關(guān)于模擬電路設(shè)計(jì)的相關(guān)課程和教材建議。模擬電路設(shè)計(jì)跟做其他事情一樣,首先要學(xué)會(huì)一些基本的準(zhǔn)則、方法和知識(shí)點(diǎn),而經(jīng)典的模擬電路設(shè)計(jì)教材就是這些東西的融合體,razavi的design of analog CMOS integrated circuits, sansen的analog design essentials, allen的CMOS Analog Circuit Design, paul gray的Analysis and Design of Analog Integrated Circuits以及baker的CMOS Circuit Design, Layout, and Simulation都是模擬電路設(shè)計(jì)經(jīng)典的教材,是即使已經(jīng)工作了都需要經(jīng)常閱讀的書籍。

razavi的design of analog CMOS integrated circuits非常適合入門學(xué)習(xí),至于其他幾本教材的學(xué)習(xí)順序則根據(jù)自己的情況自行決定。我覺得閱讀教材是在作者的幫助下分析電路,而做課后習(xí)題則是在鍛煉自己獨(dú)立分析電路和設(shè)計(jì)電路的能力,將書里的每個(gè)電路每個(gè)公式每個(gè)習(xí)題都自己分析推導(dǎo)一遍是非常有必要的,對(duì)掌握單級(jí)放大器、電流鏡,帶隙基準(zhǔn)。軌到軌輸入,class AB。運(yùn)放。比較器等基本電路具有很大的幫助,可以為以后的發(fā)展打下良好的基礎(chǔ)。信號(hào)與系統(tǒng)和matlab是本科時(shí)期必須學(xué)好的技能,在研究生的學(xué)習(xí)以及以后的工作時(shí)經(jīng)常用到。

模擬電路設(shè)計(jì)重在學(xué)習(xí)和累積經(jīng)驗(yàn)

學(xué)習(xí)模擬電路設(shè)計(jì)首先要從分析模擬電路開始,模擬電路分析應(yīng)遵循以下步驟:首先確定分析的目的,明確電路的問題;其次,將復(fù)雜電路分解成你熟識(shí)的基本電路模塊;第三,利用基本電路模塊的模型給系統(tǒng)建模;第四,對(duì)系統(tǒng)模型進(jìn)行手工計(jì)算;第五,用仿真驗(yàn)證手工計(jì)算結(jié)果,如若不一致,則必須仔細(xì)查找其原因,而不能盲目的相信仿真結(jié)果。

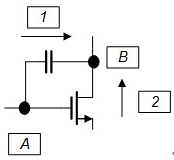

圖1 密勒電容補(bǔ)償電路

另外,在做電路設(shè)計(jì)時(shí),要特別注意電路中的信號(hào)流,包括電源、地、時(shí)鐘、輸入信號(hào)到輸出信號(hào)的通路等關(guān)鍵通路,清楚了解整個(gè)系統(tǒng)的關(guān)鍵信號(hào)流,能更快找出電路中的問題,有效減少電路時(shí)的bug和縮短debug所用的時(shí)間。

例如,在圖1所示的密勒電容補(bǔ)償電路中,A點(diǎn)的信號(hào)到達(dá)B點(diǎn)有兩種方式,一種是信號(hào)流1通過電容饋通到B點(diǎn),一種是信號(hào)流2通過MOS管到達(dá)B點(diǎn)。信號(hào)流1中的A點(diǎn)和B點(diǎn)極性相同,信號(hào)流2中的A點(diǎn)和B點(diǎn)極性相反,所以由A到B的傳輸函數(shù)有一個(gè)右半平面的零點(diǎn)。右半平面的零點(diǎn)減少了系統(tǒng)環(huán)路的相位裕度,會(huì)降低系統(tǒng)的穩(wěn)定性,所以在發(fā)現(xiàn)這個(gè)問題后可以及時(shí)將其彌補(bǔ),以免芯片無法正常工作,降低產(chǎn)品研發(fā)的風(fēng)險(xiǎn)和成本。

前文中提到模擬電路的版圖設(shè)計(jì)不光關(guān)系到芯片的性能和面積,還會(huì)影響芯片的功能,使芯片完全失效,因此我還想談下模擬電路設(shè)計(jì)中的版圖設(shè)計(jì)。現(xiàn)在SOC已成為芯片設(shè)計(jì)的主流趨勢(shì),將模擬電路與數(shù)字電路集成在一塊芯片上,這將模擬電路的版圖設(shè)計(jì)提高到一個(gè)新的難度。

模擬電路版圖設(shè)計(jì)的關(guān)鍵有兩點(diǎn):

一是匹配;二是電源、地和關(guān)鍵信號(hào)的走線。

有些前輩說模擬集成電路做的就是匹配,在高性能模擬集成電路中更是如此,匹配是降低offset、降低非線性失真、提高共模抑制比和電源抑制比。 減小工藝溫度和電源電壓對(duì)芯片性能影響的重要措施,比如bandgap電路的兩個(gè)bipolar管子之比通常是1:8,這就是為了版圖設(shè)計(jì)時(shí)更好地匹配。電源。地以及關(guān)鍵信號(hào)的走線設(shè)計(jì)主要是為了降低數(shù)字電路對(duì)模擬電路的干擾以及模擬電路中的敏感模塊受模擬電路其他模塊干擾。具體的學(xué)習(xí)方法是首先學(xué)習(xí)模擬版圖的藝術(shù)這本書,掌握基本的模擬版圖設(shè)計(jì)規(guī)則,更深層次的學(xué)習(xí)只能依靠在學(xué)習(xí)和工作中累積經(jīng)驗(yàn)。

成為優(yōu)秀的模擬電路設(shè)計(jì)師

總而言之,模擬集成電路設(shè)計(jì)是藝術(shù)和科學(xué)的結(jié)合。它既需要模擬電路設(shè)計(jì)師有藝術(shù)家那種發(fā)散的創(chuàng)新能力,又要求模擬電路設(shè)計(jì)師有科學(xué)家那種嚴(yán)謹(jǐn)?shù)膽B(tài)度和方法,因?yàn)槟M電路設(shè)計(jì)是細(xì)節(jié)決定成敗。作為一個(gè)菜鳥,我要學(xué)的東西還有很多,成為優(yōu)秀的模擬電路設(shè)計(jì)師是我一直奮斗的目標(biāo)。

-

CMOS

+關(guān)注

關(guān)注

58文章

5680瀏覽量

235137 -

模擬電路

+關(guān)注

關(guān)注

125文章

1554瀏覽量

102675 -

IC

+關(guān)注

關(guān)注

36文章

5897瀏覽量

175231

原文標(biāo)題:搞模擬IC設(shè)計(jì),這幾個(gè)重點(diǎn)可千萬別大意!

文章出處:【微信號(hào):wujianying_danpianji,微信公眾號(hào):?jiǎn)纹瑱C(jī)精講吳鑒鷹】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

做模擬IC設(shè)計(jì)需要注意哪幾個(gè)重點(diǎn)資料

做模擬IC設(shè)計(jì)需要注意哪幾個(gè)重點(diǎn)資料

評(píng)論