高阻態

高阻態這是一個數字電路里常見的術語,指的是電路的一種輸出狀態,既不是高電平也不是低電平。

如果高阻態再輸入下一級電路的話,對下級電路無任何影響,和沒接一樣,如果用萬用表測的話有可能是高電平也有可能是低電平,隨它后面接的東西定。

高阻態的實質

電路分析時高阻態可做開路理解,你可以把它看作輸出(輸入)電阻非常大。

它的極限可以認為懸空,也就是說理論上高阻態不是懸空,它是對地或對電源電阻極大的狀態。而實際應用上與引腳的懸空幾乎是一樣的。

高阻態的意義

當門電路的輸出上拉管導通而下拉管截止時,輸出為高電平,反之就是低電平。

如果當上拉管和下拉管都截止時,輸出端就相當于浮空(沒有電流流動),其電平隨外部電平高低而定,即該門電路放棄對輸出端電路的控制 。

典型應用

在總線連接的結構上。總線上掛有多個設備,設備于總線以高阻的形式連接。這樣在設備不占用總線時自動釋放總線,以方便其他設備獲得總線的使用權。

大部分單片機I/O使用時都可以設置為高阻輸入。高阻輸入可以認為輸入電阻是無窮大的,認為I/O對前級影響極小,而且不產生電流(不衰減),而且在一定程度上也增加了芯片的抗電壓沖擊能力。

高阻態常用表示方法:高阻態常用字母 Z 表示。

在一個系統中或在一個整體中,我們往往定義了一些參考點,就像我們常常說的海平面,在單片中也是如此,我們無論說是高電平還是低電平都是相對來說的。明確了這一點對這一問題可能容易理解。

單片機中的高阻態

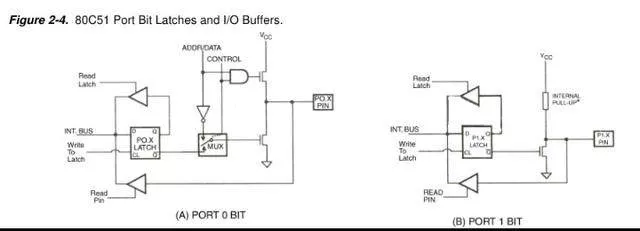

在51單片機,沒有連接上拉電阻的P0口相比有上拉電阻的P1口在I/O口引腳和電源之間相連是通過一對推挽狀態的FET來實現的,51具體結構如下圖。

組成推挽結構,從理論上講是可以通過調配管子的參數輕松實現輸出大電流,提高帶載能力,兩個管子根據通斷狀態有四種不同的組合,上下管導通相當于把電源短路了,這種情況下在實際電路中絕對不能出現。

從邏輯電路上來講,上管開-下管關開時IO與VCC直接相連,IO輸出低電平0,這種結構下如果沒有外接上拉電阻,輸出0就是開漏狀態(低阻態),因為I/O引腳是通過一個管子接地的,并不是使用導線直接連接,而一般的MOS在導通狀態也會有mΩ極的導通電阻。

到這里就很清楚了,無論是低阻態還是高阻態都是相對來說的,把下管子置于截止狀態就可以把GND和I/O口隔離達到開路的狀態,這時候推挽一對管子是截止狀態,忽略讀取邏輯的話I/O口引腳相當于與單片機內部電路開路,考慮到實際MOS截止時會有少許漏電流,就稱作“高阻態”。

由于管子PN節帶來的結電容的影響,有的資料也會稱作“浮空”,通過I/O口給電容充電需要一定的時間,那么IO引腳處的對地的真實電壓和水面浮標隨波飄動類似了,電壓的大小不僅與外界輸入有關還和時間有關,在高頻情況下這種現象是不能忽略的。

總之一句話高阻態是一個相對概念。在使用的時候我們只要按照要求去做,讓我們加上拉我們就加上,都是有一定道理的。

-

電阻

+關注

關注

86文章

5476瀏覽量

171700 -

單片機

+關注

關注

6032文章

44525瀏覽量

633260

原文標題:【華為營銷班】揭秘華為客戶關系決策鏈

文章出處:【微信號:lanxueyanjiu,微信公眾號:藍血研究】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

淺析單片機IO口輸入的高阻態

單片機IO口懸空,高阻態究竟是什么意思?

單片如何控制高阻態輸出

單片機高阻態與P0口上拉電阻講解資料下載

淺析單片機IO口工作在高阻態的輸入模式是什么狀態

單片機知識講解:什么是高阻態?

單片機知識講解:什么是高阻態?

評論