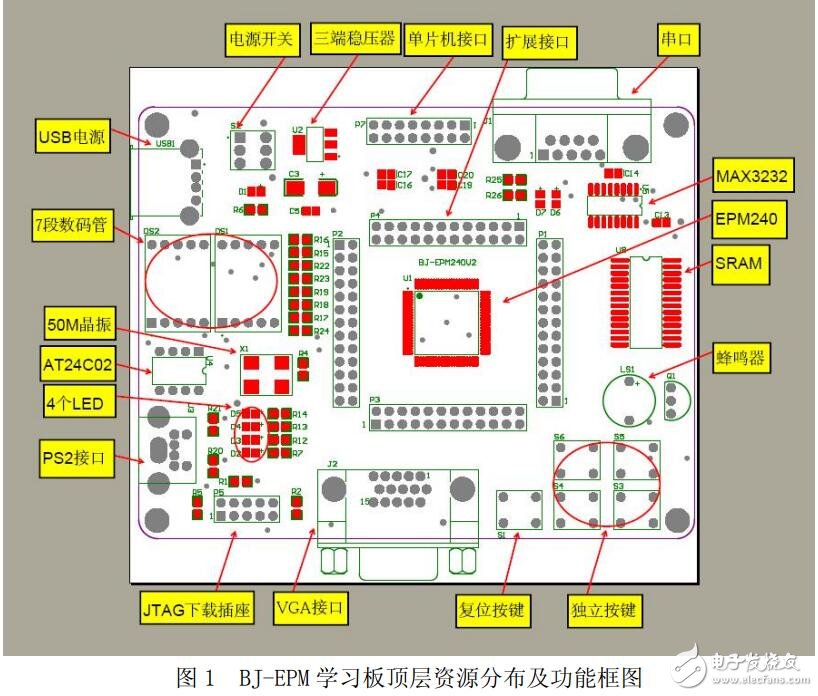

1.BJ-EPM240學習板功能框圖

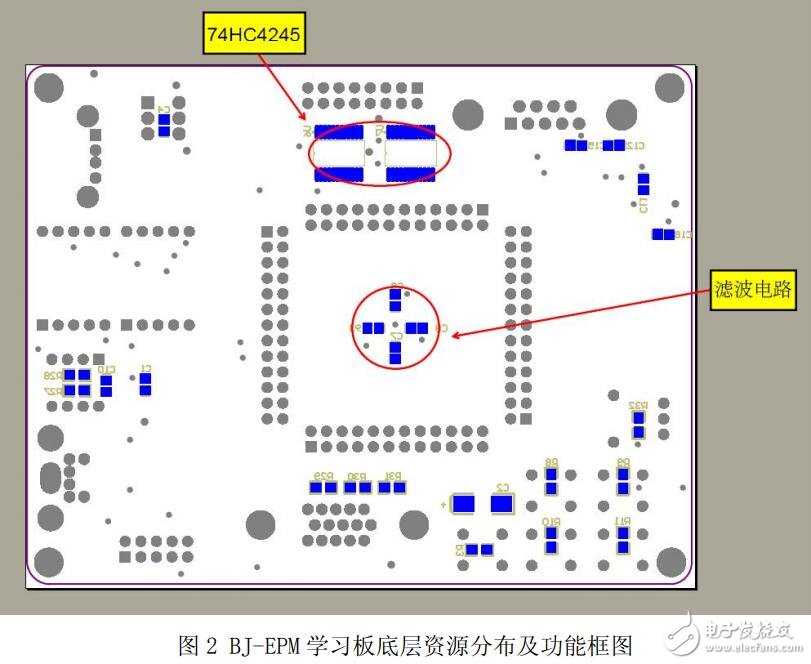

圖1和圖2是整板系統的功能框圖,從圖中可以清楚地看到EPM240T100學習板上豐富的外設資源及其位置分布情況。

2.BJ-EPM240學習板基本配置

主芯片使用的是Altera公司的MAXII系列EPM240T100C5,該芯片有240個邏輯單元,等效宏單元192個,資源比較豐富,內有8KbitFlash的存儲空間。

50MHz有源晶振,作為系統主時鐘。

低電平復位按鍵,使用EPM240的全局復位管腳。

RS232串口1個,通過串口調試助手輕松實現UART通信協議。

PS/2接口1個,實現鍵盤解碼,配合串口調試助手在PC機上顯示鍵值。

70ns快速讀寫的SRAM芯片IS62LV256-70U,具有32KB存儲空間,讓大家熟悉SRAM的讀寫操作。

EEPROM芯片AT24C02,讓大家熟悉使用verilog進行I2C通信。

4個獨立按鍵,進行verilog脈沖采樣和按鍵消抖控制。

4個流水燈,配合4位按鍵進行Johnson計數器實驗。

蜂鳴器,實現簡單的分頻計數器。

2位數碼管,使用其進行計數實驗。

外接信號電平轉換芯片SN74LVC4245,可以與單片機等5V器件進行通信,預留16PIN總線接口。

3. EPM240T100C5芯片介紹

選用Altera公司目前市場性價比較高的MAXII系列的CPLD。Altera推出的MAX II器件系列是一款革命性的CPLD產品。它基于突破性的CPLD架構,提供業界所有 CPLD系列中單個I/O管腳最低成本和最小功耗。這些器件采用新的查表(LUT)體系,采用TSMC的0.18μm嵌入Flash工藝,使其裸片尺寸僅為同樣工藝器件的1/4。

MAX II系列和上一代MAX產品相比,成本降低了一半,功耗只有其1/10,同時保持MAX系列原有的瞬態啟動、單芯片、非易失性和易用性。新的系列器件容量翻了兩番,性能是上一代MAX CPLD的兩倍多,使消費類、通信、工業和計算機產品的設計者能夠采用MAX II系列器件代替昂貴和不夠靈活的小型ASIC和ASSP。

MAX II 系列器件的主要特征:

成本優化的架構:新型 MAX II CPLD 架構包括基于 LUT 的 LAB 陣列、非易失性 Flash 存儲模塊和 JTAG 控制電路。

低功耗:MAX II 器件是動態功耗較低的 CPLD。

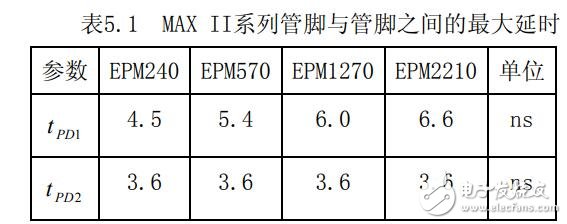

高性能:MAX II 器件支持高達 300MHz 的內部時鐘,可為用戶提供更高的系統級性能。通過改善布線結構管腳間的延時與其他同容量的 CPLD 相比大大降低,目前降低到 3.6ns。MAX II 系列管腳與管腳之間的最大延時見表 5.1,其中 PD1 t 為最大距離管腳之間的延遲時間(即對角上的管腳之間), PD2 t 為最小距離管腳的延遲時間(即相鄰的管腳之間)。

。用戶 Flash 存儲器:MAX II CPLD 內的用戶 Flash 存儲器是一個大小為 8Kbit、用戶可訪問且可編程的 Flash 存儲器塊,可用于用戶自己定義的數據。

實時在系統可編程能力(ISP):MAX II 器件支持實時在系統可編程。

靈活的多電壓內核:MAX II 架構支持 MultiVolt,允許器件在 1.8V、 2.5V 或 3.3V 電壓環境下工作。

JATG 翻譯器:MAX II CPLD 具有一種被稱為 JATG 翻譯器的功能,這種功能允許通過 MAX II 器件執行定制的 JTAG 指令,配置單板上不兼容 JTAG 協議的器件,從而簡化了單板管理。

I/O 能力:MAX II CPLD 的 I/O 能力加強了其易用性和系統集成能力。表 5.2 列出了 MAX II 器件支持的 I/O 標準。

-

學習板

+關注

關注

0文章

43瀏覽量

12154

發布評論請先 登錄

相關推薦

語音集成電路bj015怎么接線

奇怪的CPLD問題:能下載,不工作

ACT240電源波動是什么原因導致的?

TMS320LF240xA和TMS320LC240xA DSP器件數據表

端點存儲器 (EPM) 位于何處? 系統RAM還是MMIO寄存器空間?

艾睿電子聯合英飛凌推出240W USB PD3.1參考設計

3.3伏ABT八進制緩沖器/驅動器SN54LVTH240 SN74LVTH240數據表

MS4525DO-SS3BJ015AS氣壓計怎么換算高度

學習筆記分享|使用C庫函數控制ELF 1開發板的LED

BJ-EPM240學習板介紹

BJ-EPM240學習板介紹

評論