介紹

日常生活中,我們不會注意到最常用設(shè)備核心的復(fù)雜芯片 — 它們通常隱藏在設(shè)備內(nèi)部。另一方面,芯片的功能卻非常引人注目:它們能讓我們使用手機拍攝高質(zhì)量的照片,駕駛時提醒我們注意行人,以及檢測和識別我們向虛擬助手發(fā)出的命令。在本系列文章中,我將重點討論驗證芯片功能所面臨的挑戰(zhàn)。

正如廣告宣傳的那樣,在設(shè)備光鮮亮麗的外表下,隱藏著一支杰出的人才隊伍 — 研究人員、硬件架構(gòu)師、硬件設(shè)計師、軟件開發(fā)人員、集成商和質(zhì)量保證工程師 — 他們確保了每一塊芯片在任何可能的情況下都能平穩(wěn)運行。這些人員即使處于不同時區(qū)空域,也必須努力協(xié)作。他們的任務(wù)就是確保拼圖的各個部分完美地組合在一起,并通過大量的軟件代碼行和硬件邏輯塊來確保所需要的功能順利實現(xiàn),以滿足消費者的預(yù)期要求。實現(xiàn)這些芯片功能的最大挑戰(zhàn)之一在于軟件和硬件之間的邊界。

硬件調(diào)試

我假定垂閱這篇文章的您已對嵌入式設(shè)計領(lǐng)域有所了解,但我仍需快速扼要地復(fù)述一些主要的挑戰(zhàn),特別是當(dāng)開放嵌入式 DSP軟件時的挑戰(zhàn)。

首先,為什么您想使用 DSP?CEVA DSP 專門用于多個應(yīng)用領(lǐng)域,如人工智能、計算機視覺、語音識別和移動通信。相比通用 CPU,使用 DSP 可以實現(xiàn)更高的性能和更低的功耗,同時仍能保持軟件編程的靈活性。CEVA DSP 可在必要時運行實時操作系統(tǒng),以保證 DSP 應(yīng)用程序通常所需要的實時性能。應(yīng)用程序既可以在多核系統(tǒng)上同時運行多個線程,又可以在單核系統(tǒng)上分時運行。然后,線程可以異步處理多個并行進程,從而控制系統(tǒng)的不同硬件元素以及處理數(shù)據(jù)。

舉個 DSP 操作的例子,它可以通過增強顏色或?qū)Ρ榷取⒉捎酶邉討B(tài)范圍 (HDR)算法將多個圖像融合為一個圖像、自動檢測場景內(nèi)容、或穩(wěn)定快速行駛期間手持電話拍攝的抖動視頻來處理相機的圖像。或者,它還可以對來自兩個傳感器的兩個每秒 120 幀/12 位采樣率/超高清 8K分辨率視頻流來執(zhí)行上面所有這些功能,。在這種復(fù)雜運算時,數(shù)據(jù)傳輸率可超過每秒 33GB,因此,確保該過程每一步都能按預(yù)期運行具有非常大的復(fù)雜性和挑戰(zhàn)性。

DSP 架構(gòu)可能相當(dāng)復(fù)雜,相應(yīng)的匯編操作可能跨越多條線路。為了滿足預(yù)期吞吐量,需要通過專用編譯器或由程序員手動對代碼進行性能優(yōu)化。這包括展開循環(huán)、重新排序指令并將其組合在一起以便在單個循環(huán)內(nèi)并行執(zhí)行等等。調(diào)試此類代碼可能非常困難,且需要非常先進的調(diào)試工具。

通常,新功能的開發(fā)都從高級開發(fā)語言環(huán)境開始,例如Matlab、Visual Studio 或在PC 上運行的GNU 開發(fā)/調(diào)試工具。這些環(huán)境在軟件開發(fā)人員中很受歡迎,文檔完善,擁有很多針對各種算法的現(xiàn)成方法,并且通常以開源方式分發(fā)。這樣可以快速提升軟件、重用代碼、利用高級編程環(huán)境并采用快速服務(wù)器基礎(chǔ)設(shè)施。工程師可以很便捷地進行通信,共享代碼并在多個開發(fā)人員甚至團隊之間分工協(xié)作。這些開發(fā)環(huán)境可提供一種簡單而舒適的調(diào)試體驗:程序員可在運行時在應(yīng)用程序內(nèi)部進行步進操作,以檢查內(nèi)存和變量值、設(shè)置斷點、手動操縱資源并檢查結(jié)果,有時,甚至可以在不停止調(diào)試應(yīng)用程序的情況下重新編譯代碼,從而相對容易地跟蹤漏洞和實施過程中發(fā)生的故障。

但最終,該軟件需要能夠運行起來,并且在嵌入式目標(biāo)上有效運行。那時,開發(fā)人員必須有能夠在實際芯片上進行調(diào)試和優(yōu)化軟件的工具。這就需要主流的開發(fā)和調(diào)試工具有更高的能力的。

硬件調(diào)試領(lǐng)域的各項挑戰(zhàn)

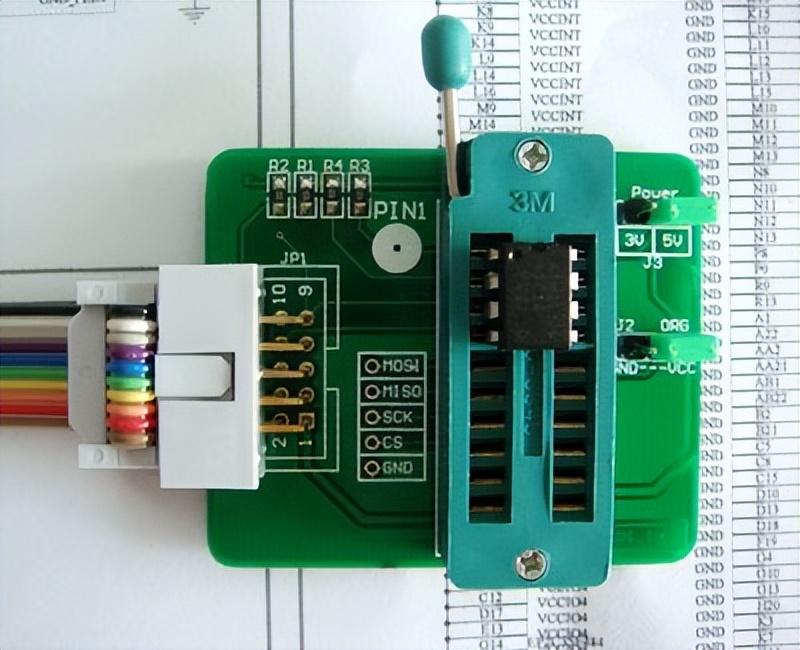

由于目標(biāo)芯片或設(shè)備在我們的桌面工作環(huán)境中屬于“外來”元素,因此在目標(biāo)硬件上調(diào)試軟件會面臨一系列不同的挑戰(zhàn)。桌面工作環(huán)境及其操作系統(tǒng)對自身的計算引擎(在一定程度上)有所了解,但通常沒有訪問外部硬件內(nèi)部狀態(tài)的通用方法。這就是為什么最終您必須采用硬件供應(yīng)商提供的嵌入式開發(fā)環(huán)境的原因。這些嵌入式開發(fā)工具可以與目標(biāo)設(shè)備進行通信,并觀測或操縱內(nèi)部狀態(tài)。當(dāng)您在不同的調(diào)試環(huán)境中進行這種詳細調(diào)試和優(yōu)化時,會希望這些工具能提供易于使用的調(diào)試體驗,并且能夠完全支持您在這個階段的所有需求。

對于目標(biāo)硬件的調(diào)試可能具有挑戰(zhàn)性,因為很多情況在您的早期開發(fā)中都無法預(yù)見。您只要與 DUT(被測設(shè)備)建立調(diào)試連接,就可能會遇到一些匪夷所思的通信問題。更為普遍的是,硬件調(diào)試問題可能發(fā)生在各個階段:在初始連接、設(shè)備重置、應(yīng)用程序加載、分步調(diào)試程序或查看內(nèi)存和變量值時;這些問題的原因可能并不明顯。基于主機或通用的開發(fā)和調(diào)試工具對目標(biāo)平臺并不了解,因此,在分析此類問題方面幾乎沒有幫助。您只能寄希望于一個充分了解你所構(gòu)建系統(tǒng)的開發(fā)/調(diào)試平臺。

-

硬件

+關(guān)注

關(guān)注

11文章

3253瀏覽量

66122 -

編譯器

+關(guān)注

關(guān)注

1文章

1618瀏覽量

49052 -

計算機視覺

+關(guān)注

關(guān)注

8文章

1696瀏覽量

45928

原文標(biāo)題:專家解讀|硬件調(diào)試的復(fù)雜性 — 第 1 部分

文章出處:【微信號:CEVA-IP,微信公眾號:CEVA】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

如何進行硬件調(diào)試?

解決驗證“最后一公里”的挑戰(zhàn):芯神覺Claryti如何助力提升調(diào)試效率

解鎖SoC “調(diào)試”挑戰(zhàn),開啟高效原型驗證之路

Midjourney正式宣告進軍硬件領(lǐng)域

說說硬件調(diào)試中發(fā)現(xiàn)的那些低級錯誤

說說硬件調(diào)試中發(fā)現(xiàn)的那些低級錯誤

解析當(dāng)代硬件工程師面臨的可靠性設(shè)計挑戰(zhàn)與應(yīng)對策略

在機遇與挑戰(zhàn)并存的AI時代,三星如何在DRAM領(lǐng)域開拓創(chuàng)新?

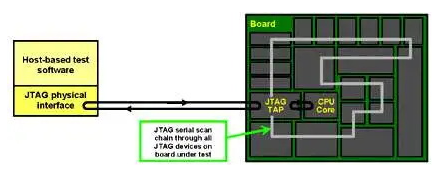

JTAG在整個嵌入式系統(tǒng)開發(fā)生命周期中的系統(tǒng)調(diào)試和測試中的作用

PLC系統(tǒng)的安裝與調(diào)試流程

硬件工程師在可靠性設(shè)計中所面臨的挑戰(zhàn)及解決之道

使用帶有DAP miniwiggler硬件的memtool進行閃存,如何使用memtool進行調(diào)試?

FPGA硬件電路的調(diào)試必備原則和技巧

硬件調(diào)試領(lǐng)域的各項挑戰(zhàn)

硬件調(diào)試領(lǐng)域的各項挑戰(zhàn)

評論