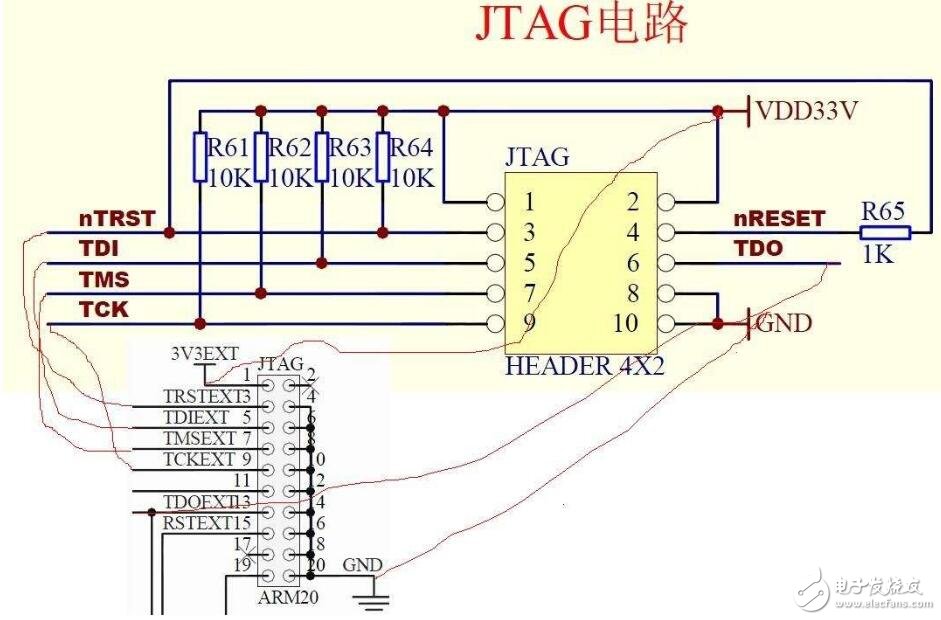

JTAG(聯(lián)合測試工作組)是一種國際標準測試協(xié)議(IEEE 1149.1兼容),主要用于芯片內(nèi)部測試。現(xiàn)在多數(shù)的高級器件都支持JTAG協(xié)議,如DSP、FPGA器件等。標準的JTAG接口是4線:TMS、TCK、TDI、TDO,分別為模式選擇、時鐘、數(shù)據(jù)輸入和數(shù)據(jù)輸出線。

如今大多數(shù)比較復雜的器件都支持 JTAG 協(xié)議,如 ARM 、 DSP 、 FPGA 器件等。標準的 JTAG 接口是 4 線: TMS 、 TCK 、 TDI 、 TDO ,分別為測試模式選擇、測試時鐘、測試數(shù)據(jù)輸入和測試數(shù)據(jù)輸出。

JTAG最初是用來對芯片進行測試的,JTAG的基本原理是在器件內(nèi)部定義一個TAP(測試訪問口)通過專用的JTAG測試工具對內(nèi)部節(jié)點進行測試。JTAG測試允許多個器件通過JTAG接口串聯(lián)在一起,形成一個JTAG鏈,能實現(xiàn)對各個器件分別測試。如今,JTAG接口還常用于實現(xiàn)ISP(在系統(tǒng)編程),對FLASH等器件進行編程。

JTAG編程方式是在線編程,傳統(tǒng)生產(chǎn)流程中先對芯片進行預編程然后再裝到板上,簡化的流程為先固定器件到電路板上,再用JTAG編程,從而大大加快工程進度。JTAG接口可對DSP芯片內(nèi)部的所有部件進行編程。

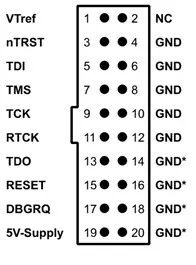

TAG引腳定義:

具有JTAG口的芯片都有如下JTAG引腳定義:

TCK——測試時鐘輸入;

TDI——測試數(shù)據(jù)輸入,數(shù)據(jù)通過TDI輸入JTAG口;

TDO——測試數(shù)據(jù)輸出,數(shù)據(jù)通過TDO從JTAG口輸出;

TMS——測試模式選擇,TMS用來設置JTAG口處于某種特定的測試模式。

可選引腳TRST——測試復位,輸入引腳,低電平有效。

含有JTAG口的芯片種類較多,如CPU、DSP、CPLD等。

JTAG內(nèi)部有一個狀態(tài)機,稱為TAP控制器。TAP控制器的狀態(tài)機通過TCK和TMS進行狀態(tài)的改變,實現(xiàn)數(shù)據(jù)和指令的輸入。

-

JTAG

+關(guān)注

關(guān)注

6文章

398瀏覽量

71598

發(fā)布評論請先 登錄

相關(guān)推薦

dp接口的定義與應用

通過JTAG接口使用SimpleLink?MSP432E4微控制器

SPI、UART、RGMII、JTAG接口的低電壓轉(zhuǎn)換

JTAG接口定義

JTAG接口定義

評論