由于高速傳輸的數據速率和緊密耦合布線,高速PCB設計的串擾分析變得越來越重要。傳統的基于路的分析已不能滿足精度要求,需要三維全波電磁求解器來模擬與PCB結構和頻率相關的效應。本文介紹了一種兼具速度和精度的新型混合求解器技術,同時開發了通過S參數后處理用于量化串擾水平的串擾度量的技術。結合這兩種技術,工程師可以僅在數小時內就能按計劃實現全板串擾分析,從而顯著縮短layout后的檢查時間并確保及時簽核。

1

簡介

串擾存在于高速PCB中的不同區域。導致串擾的一個重要來源是連接器和封裝下的引腳通孔區域和扇出區域。在本文中,我們將用Heracles工具來進行快速全板串擾掃描,以實現信號完整性和高速PCB設計的簽核。Heracles提供的混合全波EM求解器具有與傳統3D求解器相同的精度,但運行速度提高了一個數量級。

圖 1 Heracles 流程

2

混合電磁場求解器

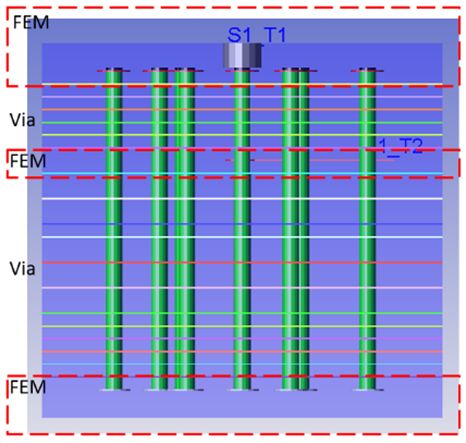

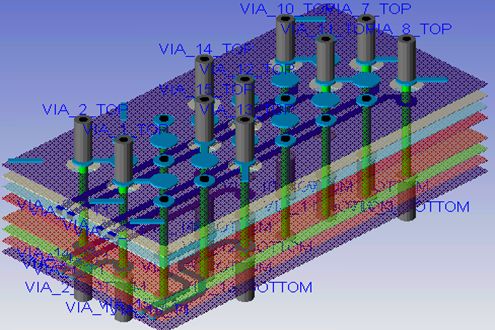

Heracles集成了一套新的基于區域分解的混合算法,與傳統的3D求解器相比,它在保持3D仿真精度的同時能顯著提高速度。首先,3D PCB結構會被分解為多個層,其中具有純via的層可以使用via求解器快速求解,而具有via和trace的層則通過3D FEM求解器來解決。

圖2 Hybrid 電磁場求解器

3

針對串擾的ICN/TDT

在頻域中,ICN(累積串擾噪聲)一般被用于量化串擾水平,它表示串擾作為頻域中串擾噪聲相對于被傳輸信號的功率譜的加權和。 在時域中,NEXT和FEXT串擾可以通過其頻域對應的傅里葉變換獲得。測量峰值能表示相應干擾源的串擾水平。所有干擾源的串擾噪聲總和就是時域中的串擾量化。

圖3 單擾 ICN 與 TDT

4

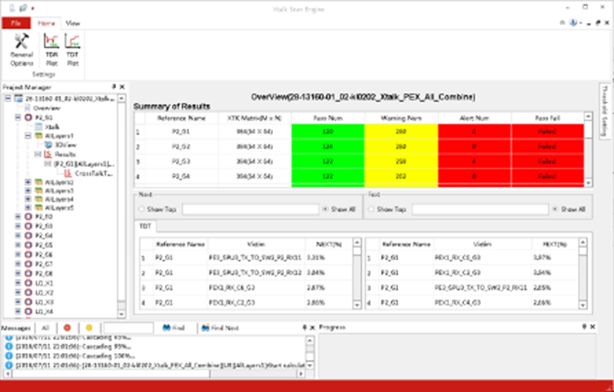

全板串擾檢查

在芯禾科技Heracles工具中,設計人員可以輕松選擇協議中定義的網絡匹配規則的串擾掃描區域。在串擾矩陣中,使用了3種顏色來突出顯示串擾級別(pass/warning/alert)。 串擾矩陣允許設計人員在Allegro工具中定位串擾熱點,并返回EM仿真模型。

圖4 EM 仿真模型

5

結論

本文介紹了Heracles工具中的混合求解器技術。與傳統的3D求解器相比,它可以在保持3D仿真精度的同時顯著提高速度。設計人員使用Heracles工具,能夠在幾個小時內實現完整的全電路板串擾分析,從而顯著縮短layout后的檢查時間并確保及時簽核。

圖5 仿真結果

-

pcb

+關注

關注

4318文章

23022瀏覽量

396422 -

求解器

+關注

關注

0文章

77瀏覽量

4516

原文標題:用于SI簽核的自動串擾掃描、阻抗掃描和DRC+

文章出處:【微信號:Xpeedic,微信公眾號:Xpeedic】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

《FPGACPLD設計工具──Xilinx+ISE使用詳解》

混合電路和模塊技術簡史

混合信號設計的模擬工具

電子管集成電路混合功放制作詳解

混合FEBI求解器的實現

IE和FEBI求解器詳解及對比

基于SMT求解器的程序路徑驗證方法

Heracles工具中的混合求解器技術詳解

Heracles工具中的混合求解器技術詳解

評論