4 mA至20 mA模擬電流環(huán)路常用于工廠(chǎng)環(huán)境中。雖然這些環(huán)境中的基本信號(hào)調(diào)制均相同,但帶寬要求卻有很大的不同。工廠(chǎng)控制系統(tǒng)可能需要100 Hz環(huán)路帶寬(來(lái)自位置和位移傳感器)。而典型的過(guò)程控制系統(tǒng)僅需幾Hz更新速率,且一般都支持HART。HART (可尋址遠(yuǎn)程傳感器高速通道的開(kāi)放通信協(xié)議)協(xié)議允許在傳統(tǒng)的模擬4 mA至20 mA電流環(huán)路內(nèi)實(shí)現(xiàn)雙向1.2 kHz/2.2 kHz FSK (頻移鍵控)調(diào)制數(shù)字通信。設(shè)計(jì)同時(shí)滿(mǎn)足兩種情況的4 mA至20 mA輸入可能會(huì)有一定難度。本文提供了一種方法,可以極大地簡(jiǎn)化這類(lèi)設(shè)計(jì)。

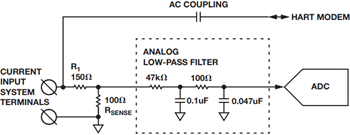

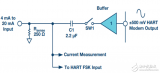

圖1中的電路圖是一個(gè)支持HART的模擬輸入的傳統(tǒng)實(shí)現(xiàn)方法。

R1和RSENSE組成一個(gè)250 Ω系統(tǒng)端接阻抗。HART FSK信號(hào)從該處到HART調(diào)制解調(diào)器為交流耦合。通過(guò)精密100 Ω RSENSE電阻,將4 mA至20 mA模擬信號(hào)轉(zhuǎn)換為0.4 V至2 V電壓信號(hào)。然后,模擬低通濾波器衰減模擬信號(hào)中的HART FSK成分,接著將其輸入ADC。二階低通模擬濾波器帶寬為25 Hz,滾降為–40 dB/十倍頻程。

該電路符合HART規(guī)范,可將HART FSK信號(hào)衰減至4 mA至20 mA滿(mǎn)量程以下超過(guò)–60 dB電平,確保HART FSK通信的4 mA至20 mA模擬輸入擾動(dòng)不超過(guò)0.1%。

另一方面,該模擬低通濾波器在系統(tǒng)輸入端的滿(mǎn)量程跳變之后,建立至0.1%以?xún)?nèi)需大約70 ms。這種較長(zhǎng)的建立時(shí)間和低帶寬性能不適合沒(méi)有HART通訊需求的高速系統(tǒng)。雖然模擬濾波器可以被旁路掉,但需要額外的模擬電路,比如開(kāi)關(guān)或多路復(fù)用器。

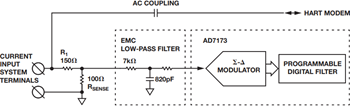

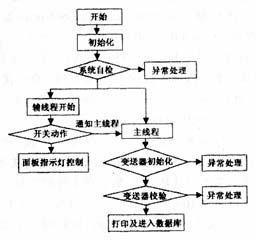

圖2顯示了支持HART的模擬輸入的替代方案。

與上一個(gè)電路類(lèi)似,HART FSK信號(hào)交流耦合至250 Ω輸入阻抗,而4 mA至20 mA信號(hào)通過(guò)精密100 Ω RSENSE電阻轉(zhuǎn)換為0.4 V至2 V電壓信號(hào)。然而在本電路中,一個(gè)輕度的低通濾波器將信號(hào)帶寬限制為27 kHz左右,以便為系統(tǒng)提供免疫性和電磁兼容性(EMC)。系統(tǒng)輸入端滿(mǎn)量程跳變后,濾波器在40 μs時(shí)間內(nèi)建立至0.1%。

該信號(hào)通過(guò)內(nèi)置的數(shù)字濾波器傳輸至Σ-Δ型ADC (比如ADI的 AD7173)。數(shù)字濾波器可編程設(shè)置為較慢的工作速度模式和最優(yōu)HART FSK信號(hào)抑制模式,或者在要求快速模擬輸入時(shí)設(shè)置為快速工作模式。

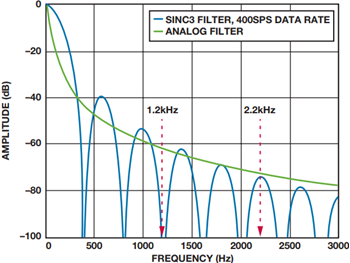

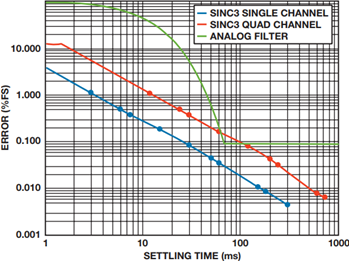

AD7173支持多種工作模式。其中一種模式適合用來(lái)抑制HART FSK信號(hào),將SINC3濾波器的陷波頻率設(shè)為400 Hz,或者可在較低HARTFSK頻率(1.2 kHz)時(shí)提供深濾波器陷波并可在較高頻率(2.2 kHz)時(shí)提供大幅衰減的分?jǐn)?shù)頻率。圖3中的曲線(xiàn)顯示該數(shù)字濾波器的頻率響應(yīng),及其與圖1中模擬濾波器的比較。

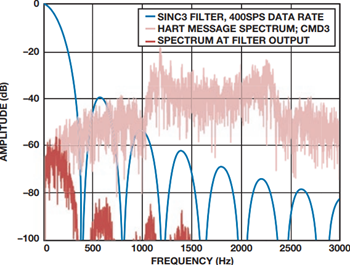

不幸的是,真實(shí)情況遠(yuǎn)沒(méi)有那么簡(jiǎn)單。當(dāng)一條完整的消息經(jīng)過(guò)HART發(fā)送后,HART FSK調(diào)制信號(hào)頻譜不僅在基頻調(diào)制頻率處包含電能,且在1.2 kHz與2.2 kHz載波之間、下方和上方包含頻率分量。

圖4顯示了HART FSK消息在ADC輸入端的典型頻譜,以及通過(guò)sinc3濾波器以400 Hz陷波衰減時(shí)的頻譜。本例中,主機(jī)發(fā)送HART命令3,從機(jī)響應(yīng)該命令。

由圖4可以看出,HART消息的一部分(尤其在較低頻率處)依然可以出現(xiàn)在模數(shù)輸出數(shù)據(jù)中。也就是說(shuō),可以輕松更改數(shù)字濾波器設(shè)置,以便實(shí)現(xiàn)4 mA至20 mA輸入速度和HART FSK采樣抑制之間的正確平衡。

圖5顯示了系統(tǒng)性能,其測(cè)量值在4 mA至20 mA滿(mǎn)量程范圍內(nèi)以百分比誤差表示,同時(shí)比較模擬濾波器(如圖1所示)和sinc3數(shù)字濾波器(如圖2所示)的系統(tǒng)速度。

模擬濾波器在硬件中固定,并具有固定的建立時(shí)間。對(duì)于系統(tǒng)輸入端的快速變化模擬信號(hào)而言,模擬濾波器輸出誤差由其較慢的建立時(shí)間決定。例如,如果系統(tǒng)輸入每40 ms改變滿(mǎn)量程,則濾波器輸出不會(huì)建立至正確值的1%以?xún)?nèi)。對(duì)于較慢的輸入信號(hào)而言,模擬濾波器輸出誤差由其抑制HART FSK信號(hào)低頻分量的能力決定。對(duì)于典型HART命令3消息而言,該誤差測(cè)量值約為4 mA至20 mA滿(mǎn)量程的0.09%。

此外,數(shù)字SINC3濾波器的建立時(shí)間是一個(gè)用戶(hù)設(shè)置的參數(shù),濾波器輸出誤差是由于HART FSK調(diào)制對(duì)應(yīng)的濾波器設(shè)置決定的。例如,400 Hz陷波的SINC3濾波器對(duì)應(yīng)7.5 ms建立時(shí)間,當(dāng)傳輸HART命令3時(shí),A/D上測(cè)得的擾動(dòng)不足4 mA至20 mA滿(mǎn)量程的0.4%。在具有四個(gè)模擬輸入的系統(tǒng)中,SINC3濾波器在通道之間順序切換。同樣的400 Hz陷波SIN3濾波器現(xiàn)在需要4 × 7.5 = 30 ms才能掃描全部四個(gè)通道。這便是四通道系統(tǒng)的曲線(xiàn)在30 ms處均顯示出約為0.4%誤差的原因。

對(duì)于更精確的4 mA至20 mA輸入而言,sinc3濾波器可設(shè)為30 ms建立時(shí)間,該設(shè)置對(duì)應(yīng)100 Hz陷波且將HART信號(hào)抑制在不足滿(mǎn)量程的0.1%。如果在系統(tǒng)中速度更為重要,則6 ms建立時(shí)間(約500 Hz陷波)的sinc3濾波器依然可以將HART通信信號(hào)抑制在4 mA至20 mA滿(mǎn)量程的0.5%以下。此外,如果只要求速度且無(wú)需進(jìn)行HART通信,則前文示例中的AD7173能夠以每通道161 μs的建立時(shí)間達(dá)到31 kSPS的采樣速率。

總之,傳統(tǒng)的模擬低通濾波器較容易理解,而某些情況下,每通道略為增加幾個(gè)元器件可在多通道系統(tǒng)中實(shí)現(xiàn)較好的模擬輸入性能。另一方面,Σ-型ADC的集成數(shù)字sinc3濾波器具有極大的靈活性,而這種靈活性是一路直到終端系統(tǒng)用戶(hù)都可提供的。數(shù)字解決方案所需硬件較少,并且若設(shè)置得當(dāng),則其在HART FSK信號(hào)濾波性能方面遠(yuǎn)優(yōu)于單通道系統(tǒng)中的模擬解決方案,而與最多四通道的系統(tǒng)相比具有接近或更佳的性能。

-

HART

+關(guān)注

關(guān)注

2文章

74瀏覽量

32667 -

多路復(fù)用器

+關(guān)注

關(guān)注

9文章

869瀏覽量

65283 -

模擬電流環(huán)路

+關(guān)注

關(guān)注

0文章

2瀏覽量

2545

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

四種模擬輸入信號(hào)的保護(hù)電路實(shí)現(xiàn)方法

HART協(xié)議傳輸原理

【技術(shù)貼】HART協(xié)議傳輸原理和特點(diǎn)

基于HART兼容性簡(jiǎn)化模擬電流環(huán)路設(shè)計(jì)

HART的電流輸入

傳統(tǒng)變送器的HART改造

傳統(tǒng)變送器的HART改造

HART協(xié)議智能儀表自動(dòng)校驗(yàn)系統(tǒng)的設(shè)計(jì)和實(shí)現(xiàn)

什么是HART協(xié)議,HART是什么意思

支持HART的電流輸入以及與向余量受限的4mA至20mA輸入設(shè)計(jì)中添加HART功能

關(guān)于HART協(xié)議的低功耗智能變送器的研究

如何在支持HART的模擬輸入上實(shí)施硬件資料下載

一個(gè)支持HART的模擬輸入的傳統(tǒng)部署方法資料下載

使用TPS2661x保護(hù)模擬輸入和輸出模塊中的HART I/O

HART的模擬輸入的傳統(tǒng)實(shí)現(xiàn)方法

HART的模擬輸入的傳統(tǒng)實(shí)現(xiàn)方法

評(píng)論