太陽能應(yīng)用中的電壓和電流測量需采用隔離測量技術(shù)。DSP Sinc輸入以及ADIAD7401A隔離式ADC恰好提供ADI信號鏈的一個示例,實現(xiàn)這種隔離測量。本文介紹采用ADSP-CM403xy和AD7401A器件,并由ADI設(shè)計的測量應(yīng)用典型信號鏈。

太陽能光伏逆變器系統(tǒng)

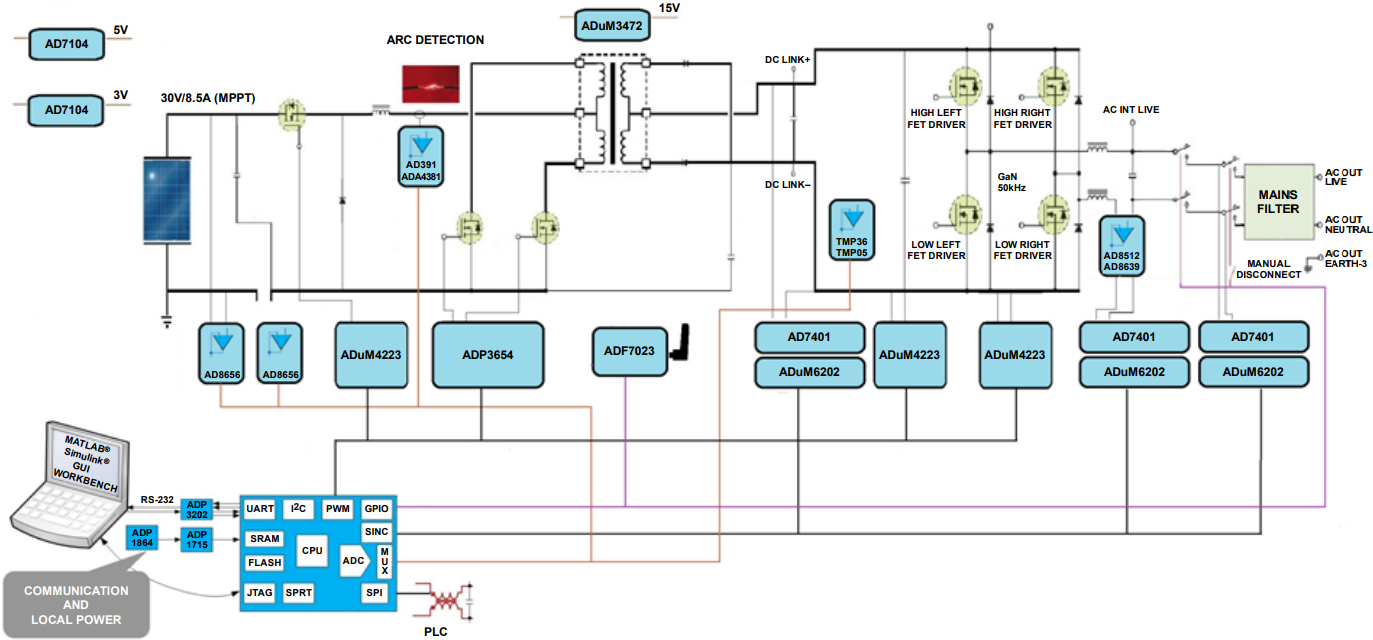

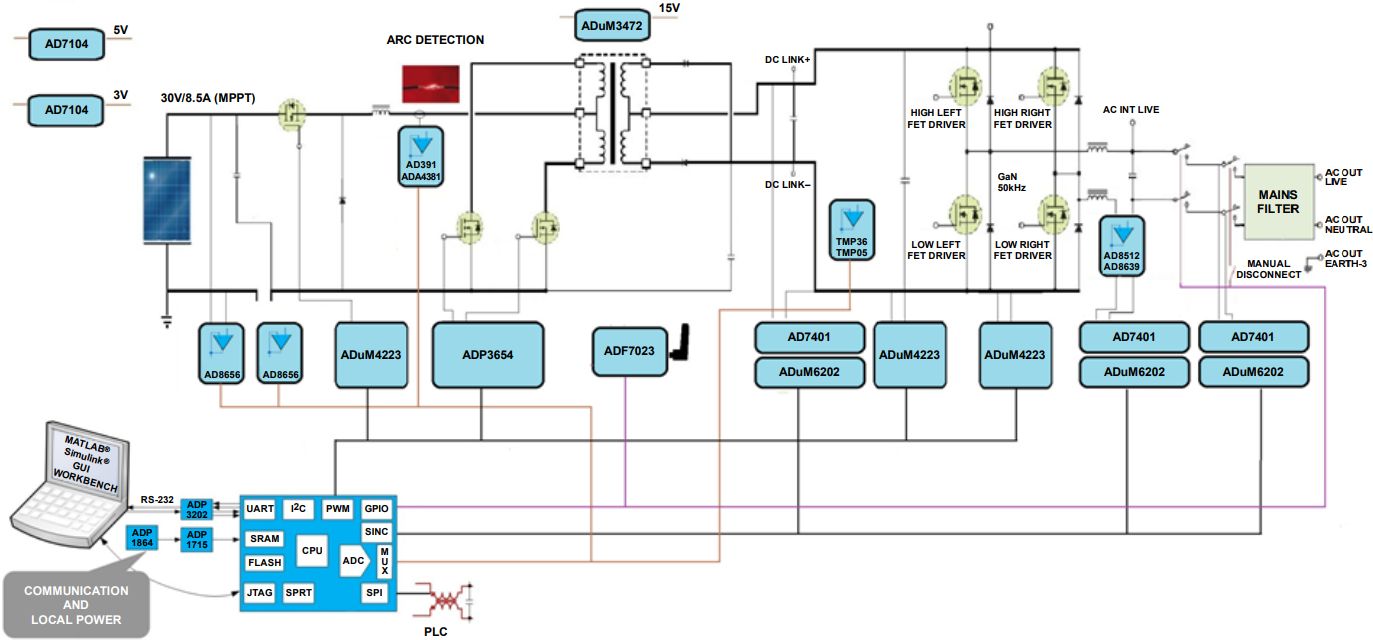

太陽能光伏逆變器轉(zhuǎn)換來自太陽能面板的電能并高效地將其部署到公用電網(wǎng)中。來自太陽能面板的電能基本上屬于直流源,它會被轉(zhuǎn)換成交流,并與電網(wǎng)頻率成一定的相位關(guān)系,饋送至公用電網(wǎng)上,且效率極高。轉(zhuǎn)換可以采用單級,也可以采用多級(見圖1)。第1級通常為DC-DC轉(zhuǎn)換,其中太陽能面板的低電壓與高電流輸出轉(zhuǎn)換為高電壓與低電流。這樣做的目的是為了將電壓提升至與電網(wǎng)峰值電壓兼容的水平。第2級通常將直流電壓和電流轉(zhuǎn)換為交流電壓和電流,一般使用H-電橋拓撲。

ADC理論—AD7401A

AD7401A是一款二階Σ-Δ調(diào)制器,片上的數(shù)字隔離采用ADI公司的iCoupler? 技術(shù),能將模擬輸入信號轉(zhuǎn)換為高速1位數(shù)據(jù)流。AD7401A采用5 V電源供電,可輸入±250 mV的差分信號(滿量程±320 mV)。模擬調(diào)制器對模擬輸入信號連續(xù)采樣,因而無需外部采樣保持電路。輸入信息以數(shù)據(jù)流密度的形式包含在輸出數(shù)據(jù)流內(nèi),該數(shù)據(jù)流的最高數(shù)據(jù)速率可到20 MHz。通過適當?shù)臄?shù)字濾波器(稱為Sinc濾波器)可重構(gòu)原始信息。處理器側(cè)(非隔離)可采用5 V或3 V電源 (VDD2)。

示例電路 – 描述

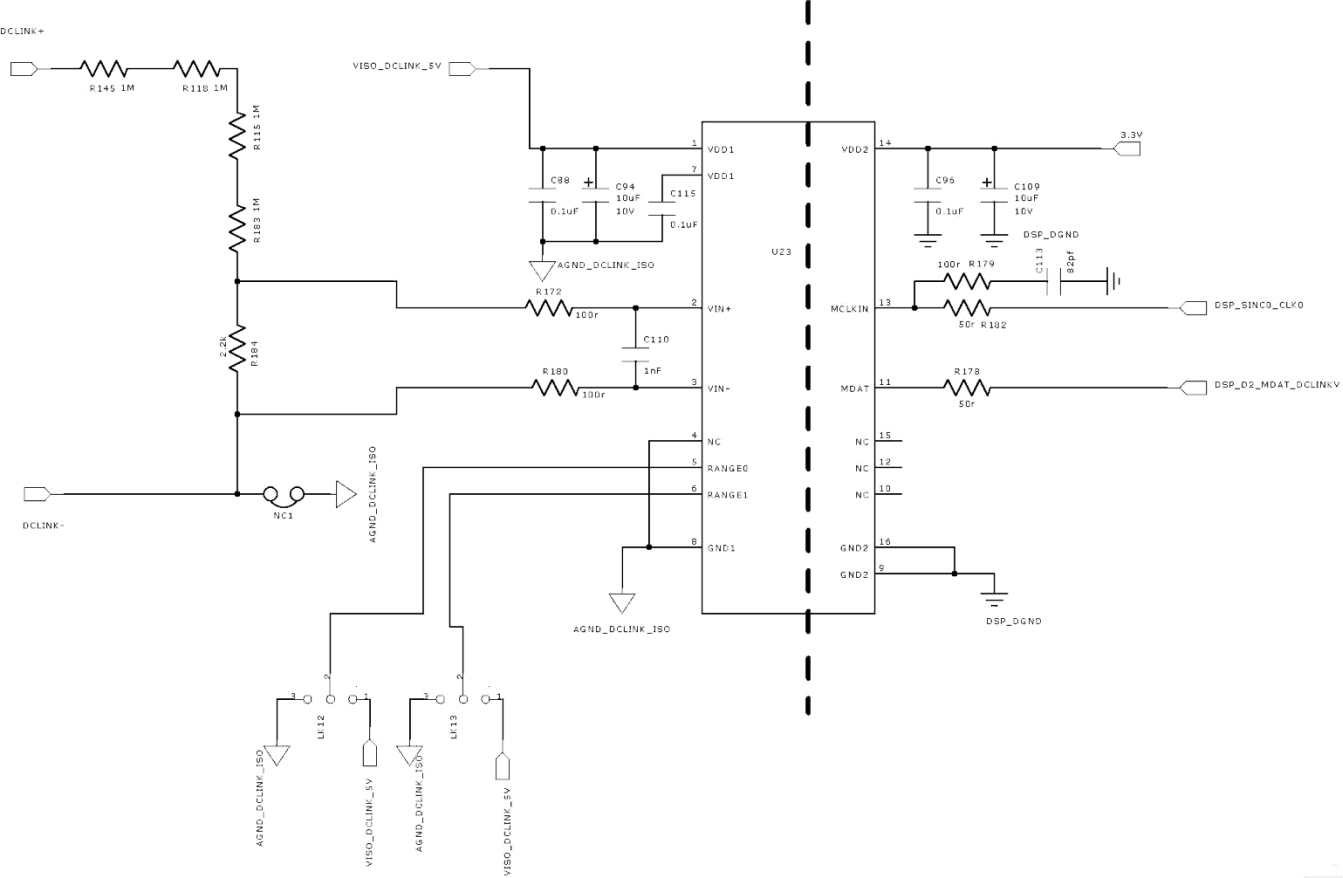

Σ-Δ 調(diào)制器的交流輸入是一個交流正弦波,表示單相電網(wǎng)發(fā)出的220 V rms信號。電阻分頻器將輸入范圍縮小到ADC的額定輸入范圍。輸入濾波器可降低輸入端的噪聲。

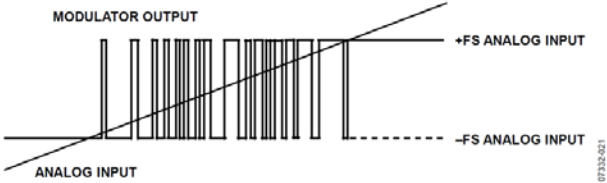

Σ-Δ 調(diào)制器輸出包含兩個信號:來自ADSP-CM403xyDSP處理器的高速時鐘輸入,以及保持調(diào)制數(shù)據(jù)的數(shù)據(jù)信號。該數(shù)據(jù)可直接輸入Sinc3濾波器,直接將數(shù)據(jù)轉(zhuǎn)換為ADC結(jié)果。下文顯示該數(shù)據(jù)的一個示例。

在ADC的下限范圍內(nèi),輸入信號具有窄脈沖寬度,而在上限范圍內(nèi)脈沖寬度幾乎達到其最大值。輸出數(shù)據(jù)通過Sinc濾波器后,便如對角線所示。AD7401A工作電壓高達891 V單極性范圍,或565 V雙極性范圍,并橫跨隔離柵:20μm聚酰亞胺。更多有關(guān)這些內(nèi)容的信息以及各種認證可在相關(guān)數(shù)據(jù)手冊中找到。

ADSP-CM403XY SINC3外設(shè)模塊

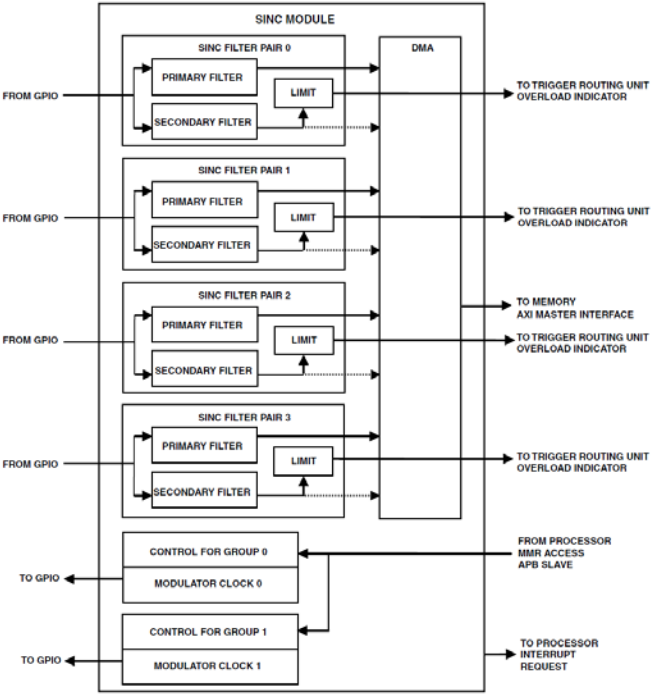

框圖顯示4對Sinc濾波器(Sinc0至Sinc3)、2個調(diào)制器時鐘源和2組控制寄存器(單元)。模塊接受4路來自GPIO輸入引腳的Σ-Δ 位流,并將2個調(diào)制器時鐘源導(dǎo)入GPIO輸出引腳。脈沖寬度調(diào)制(PWM)信號使調(diào)制器時鐘同步,以獲得最佳的系統(tǒng)性能。每個Sinc濾波器對均包含初級濾波器、次級濾波器、DMA接口和過載限值檢測功能。初級Sinc濾波器通過DMA將其數(shù)據(jù)傳輸至存儲器。次級Sinc濾波器產(chǎn)生過載信號,可通過觸發(fā)路由單元(TRU)路由該信號,使PWM調(diào)制器產(chǎn)生跳變,生成中斷。

使用AD7401A時,器件額定抽取速率(DR)為256,但也可在其他抽取速率下使用該器件。

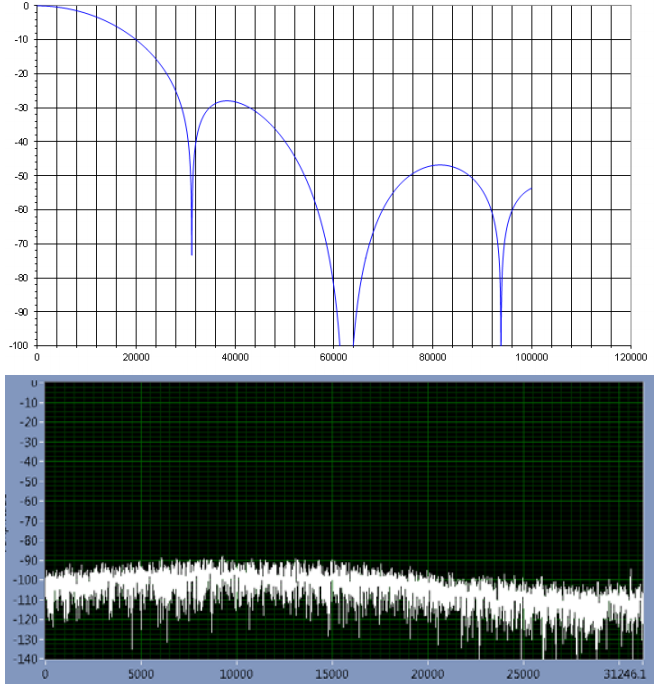

對于DR=256的情況而言,Sinc3濾波器的響應(yīng)見下文中的圖5a和5b。

數(shù)字濾波器

Sinc濾波器的傳遞函數(shù)使其能用在數(shù)字邏輯中(使用一系列求和與抽取函數(shù))。使用濾波器移除調(diào)制器采樣時鐘,恢復(fù)采樣信號的數(shù)字值。濾波器設(shè)計匹配雙極性Σ-Δ 調(diào)制器,0 V輸入下具有50%脈沖密度,正輸入時超過50%,而負輸入時不足50%,如圖6所示。

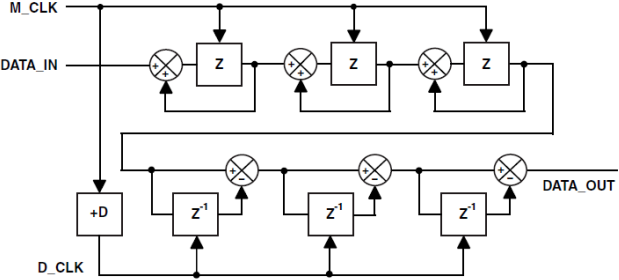

數(shù)字濾波器是一組累加器,由調(diào)制器時鐘(M_CLK)驅(qū)動,后接一組由抽取時鐘(D_CLK)驅(qū)動的微分器。 輸入累加器將輸入位流轉(zhuǎn)換為多字節(jié)字,而輸出微分器獲取位流的均值1密度。

累加器和微分器的級數(shù)可以為3或4,具體取決于濾波器階數(shù)。濾波器的直流增益和帶寬為濾波器階數(shù)(O)和抽取速率(D)的函數(shù),即調(diào)制器時鐘與抽取時鐘的比值。Sinc濾波器傳遞函數(shù)由累加器與微分器的傳遞函數(shù)之積確定,Z域內(nèi)的表達式為:

PWM和SINC數(shù)據(jù)對齊

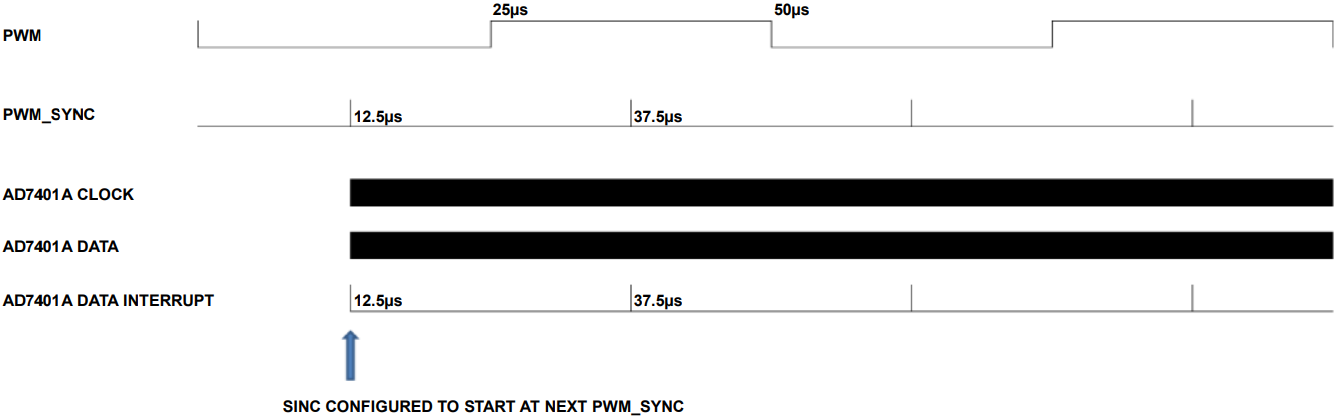

Sinc外設(shè)時鐘和PWM本質(zhì)上運行在同樣的ADSP-CM403系統(tǒng)時鐘下,典型值為100 MHz。PWM和Sinc可以同步以便提供數(shù)據(jù),并且時間與速率恰好和控制算法一致。通常與PWM電平波形對齊。下圖顯示使用Sinc輸入進行電網(wǎng)同步所需時序的示例。當PWM運行在20 kHz (50 μs)時,PWM_SYNC信號(同步不同DSP的PWM模塊或外部PWM時需要用到該信號)位于PWM波形中央,幾乎不發(fā)生切換。若要對齊Sinc數(shù)據(jù),則AD7401A的時鐘速率應(yīng)設(shè)為10.24 MHz,并且抽取速率為256(見AD7401A數(shù)據(jù)手冊)。這將產(chǎn)生40 KHz (50μs)的16位字速率,兩倍于PWM頻率。由于Sinc還可設(shè)為與PWM_SYNC輸出對齊(如下框圖所示),Sinc現(xiàn)在能在每個PWM周期內(nèi)產(chǎn)生兩個數(shù)據(jù)輸出。輸出字在SRAM中可用, 位置在下一個PWM_SYNC信號位置處。顯然,它說明Sinc數(shù)據(jù)可用于電網(wǎng)同步算法控制中。

編程示例

/* SPECIFY DECIMATION RATE OPTIONS */

/* 256 */

// RESULT = ADI_SINC_SETRATECONTROL (DEV, ADI_SINC_GROUP_0, ADI_SINC_FILTER_PRIMARY,DECRATE_256, 0);

// RESULT = ADI_SINC_SETLEVELCONTROL (DEV, ADI_SINC_GROUP_0, 0, 0, SAMPLECOUNT_INTRATE, PSCALE_256); // PCINT INT RATE

/* 128 */

RESULT = ADI_SINC_SETLEVELCONTROL (DEV, ADI_SINC_GROUP_0, 0, 0, SAMPLECOUNT_INTRATE, PSCALE_128); // PCINT INT RATE

RESULT = ADI_SINC_SETRATECONTROL (DEV, ADI_SINC_GROUP_0, ADI_SINC_FILTER_PRIMARY,DECRATE_128, 0);

/* 64 */

RESULT = ADI_SINC_SETLEVELCONTROL (DEV, ADI_SINC_GROUP_0, 0, 0, SAMPLECOUNT_INTRATE, PSCALE_64); // PCINT INT RATE

RESULT = ADI_SINC_SETRATECONTROL (DEV, ADI_SINC_GROUP_0, ADI_SINC_FILTER_PRIMARY,DECRATE_64, 0);

/* SET SECONDARY RATE CONTROL “/

RESULT = ADI_SINC_SETRATECONTROL (DEV, ADI_SINC_GROUP_0, ADI_SINC_FILTER_SECONDARY, 8, 0);

RESULT = ADI_SINC_SETFILTERORDER (DEV, ADI_SINC_GROUP_0, ADI_SINC_FILTER_THIRD_ORDER, ADI_SINC_FILTER_THIRD_ORDER); RESULT = ADI_SINC_SETCIRCBUFFER(DEV, ADI_SINC_GROUP_0, SINC_CIRCBUFFER, CIRC_BUF_SIZE);

/* SET OVERLOAD AMPLITUDE DETECTION LIMITS TO 0 – FULLSCALE */

RESULT = ADI_SINC_SETAMPLITUDELIMIT (DEV, ADI_SINC_PAIR_0, 0X0000, 0XFFFF);

RESULT = ADI_SINC_SETAMPLITUDELIMIT (DEV, ADI_SINC_PAIR_1, 0X0000, 0XFFFF);

RESULT = ADI_SINC_SETAMPLITUDELIMIT (DEV, ADI_SINC_PAIR_2, 0X0000, 0XFFFF);

RESULT = ADI_SINC_SETAMPLITUDELIMIT (DEV, ADI_SINC_PAIR_3, 0X0000, 0XFFFF);

/* SPECIFY MODULATOR CLOCK FREQUENCY, PHASE & STARTUP SYNCHRONIZATION */

RESULT = ADI_SINC_CONFIGMODCLOCK (DEV, ADI_SINC_GROUP_0, FSYSCLK, MODCLK, 0, FALSE); // UP TO 20MHZ

/* IT’S THE SAME CLOCK AS THE PWM – SO PWM AND SINC ARE SYNCHRONOUS */

RESULT = ADI_SINC_ENABLEMODCLOCK (DEV, ADI_SINC_GROUP_0, ADI_SINC_MOD_CLK_IMMEDIATE );

/* ASSIGN BUFFERS TO RECEIVE SINC DATA-AUTOMATICALLY DMA’D INTO SRAM IN THE ADSP-CM403*/

RESULT = ADI_SINC_SUBMITBUFFER(DEV, ADI_SINC_GROUP_0, SINCDATA0, NUM_SAMPLES);

/* ROUTE THE TRU INTERRUPT */

RESULT = ADI_SINC_ENABLEDATAINTERRUPT (DEV, ADI_SINC_GROUP_0, ADI_SINC_DATA_INT_0, TRUE);

/* ENABLE & ASSIGN USED SINC FILTER PAIR, AND SPECIFY INTERRUPT MASKS */

RESULT = ADI_SINC_SETCONTROLINTMASK (DEV, ADI_SINC_INT_EPCNT0|ADI_SINC_INT_EFOVF0|ADI_SINC_INT_EPCNT1|ADI_SINC_INT_EFOVF1);

RESULT = ADI_SINC_ENABLEPAIR(DEV, ADI_SINC_PAIR_0, ADI_SINC_GROUP_0, TRUE); // ACV_EXTERNAL

RESULT = ADI_SINC_ENABLEPAIR(DEV, ADI_SINC_PAIR_1, ADI_SINC_GROUP_0, TRUE); // ACV_INTERNAL

RESULT = ADI_SINC_ENABLEPAIR(DEV, ADI_SINC_PAIR_2, ADI_SINC_GROUP_0, TRUE); // DC LINK

RESULT = ADI_SINC_ENABLEPAIR(DEV, ADI_SINC_PAIR_3, ADI_SINC_GROUP_0, TRUE); // AC_CURRENT

/* WAIT AND READ FULL SINE WAVE INTO SRAM – START NEAR AC CROSSOVER. */

DO

{

PWM_SINC_LOOP=0;

GET_ADC_DATA_PWM();

}

WHILE ((SINC_VEXT_DATA[0] 》 50) || (SINC_VEXT_DATA[0] 《 -50)) ; // START SINC AT 0 V MEASUREMENT-ALIGNS WITH SINEWAVE.

-

太陽能

+關(guān)注

關(guān)注

37文章

3341瀏覽量

113780 -

逆變器

+關(guān)注

關(guān)注

279文章

4606瀏覽量

204625 -

面板

+關(guān)注

關(guān)注

13文章

1657瀏覽量

53646

發(fā)布評論請先 登錄

相關(guān)推薦

在太陽能應(yīng)用中采用ADI信號鏈實現(xiàn)隔離測量技術(shù)

在太陽能應(yīng)用中采用ADI信號鏈實現(xiàn)隔離測量技術(shù)

評論