想法簡介

仿真已經(jīng)成為設(shè)計(jì)過程中的一個(gè)重要階段,因?yàn)樗梢宰?a target="_blank">工程師在原型設(shè)計(jì)之前評(píng)估和驗(yàn)證電路行為,防止設(shè)計(jì)缺陷在設(shè)計(jì)鏈中層疊,并有助于設(shè)計(jì)人員在虛擬環(huán)境中提高了電路的性能,無風(fēng)險(xiǎn)。

還有什么比讓電路板商店回歸錯(cuò)誤設(shè)計(jì)更令人沮喪的事情嗎?今天許多設(shè)計(jì)師都面臨著在幾周內(nèi)(如果不是幾天)生產(chǎn)原型的壓力,并且設(shè)計(jì)迭代的余地有限。幸運(yùn)的是,最新的設(shè)計(jì)工具通過提供整體和直觀的電路設(shè)計(jì)和驗(yàn)證方法來提高生產(chǎn)率。

許多半導(dǎo)體制造商提供工具來幫助在初始規(guī)范階段設(shè)計(jì)穩(wěn)健的系統(tǒng)模塊。 Analog Devices,Inc。 (ADI),例如,hasan在線濾波器設(shè)計(jì)工具(參見參考文獻(xiàn)1),指導(dǎo)用戶完成有源濾波器合成過程以及根據(jù)這些規(guī)范選擇推薦的運(yùn)算放大器。然后,該工具生成最終設(shè)計(jì)拓?fù)洌约拔锪锨鍐魏蚐PICE網(wǎng)表。在原型設(shè)計(jì)之前的階段,來自NI(NI)的模擬環(huán)境使用指定部件的宏模型提供進(jìn)一步的優(yōu)化和驗(yàn)證(參見參考文獻(xiàn)2)。

在本文中,我們將探討如何進(jìn)行整體設(shè)計(jì)這種方法可以加速并改善過濾器設(shè)計(jì)中經(jīng)常令人生畏的任務(wù) - 這是一系列電子應(yīng)用中常見的構(gòu)建模塊。但首先是一些背景知識(shí)。

SIM基礎(chǔ)知識(shí)

最流行的模擬電路仿真工具是SPICE,它代表集成電路強(qiáng)調(diào)的仿真程序。 SPICE可以追溯到20世紀(jì)60年代后期,當(dāng)時(shí)它是在加州大學(xué)伯克利分校開發(fā)的。 SPICE已發(fā)展成為模擬電路仿真的行業(yè)標(biāo)準(zhǔn),并且仍然是世界上使用最廣泛的電路仿真器。多年來,增加了更多的模擬算法,組件模型和擴(kuò)展。例如,在佐治亞理工學(xué)院開發(fā)的XSPICE允許對(duì)組件進(jìn)行行為建模,以加快混合模式和數(shù)字仿真的速度。 NI Multisim ?環(huán)境支持SPICE 3F5和XSPICE仿真。

但是為什么設(shè)計(jì)師需要模擬仿真?仿真已經(jīng)成為設(shè)計(jì)過程中必不可少的階段,因?yàn)樗梢宰尮こ處熢谠驮O(shè)計(jì)之前評(píng)估和驗(yàn)證電路行為。仿真可以防止設(shè)計(jì)缺陷從設(shè)計(jì)鏈級(jí)聯(lián)到制造的電路板,重新設(shè)計(jì)變得成本更高。此外,通過探索一系列假設(shè)情景,設(shè)計(jì)人員可以在無風(fēng)險(xiǎn)的情況下提高其在虛擬環(huán)境中的電路性能。

使用電路仿真器的主要好處之一是能力模擬模擬真實(shí)可訂購零件的宏模型。現(xiàn)代SPICE仿真器也采用越來越多的圖形化方法來處理傳統(tǒng)上基于文本的過程。例如,NI Multisim包含17,500多個(gè)組件,其中許多宏模型來自領(lǐng)先的半導(dǎo)體制造商;捕獲電路時(shí)自動(dòng)生成基于文本的SPICE網(wǎng)表,交互式測(cè)量儀器(如示波器或函數(shù)發(fā)生器)具有模擬真實(shí)臺(tái)式電腦的顯示和功能。通過這些圖形擴(kuò)展,設(shè)計(jì)人員不再需要具備SPICE語法方面的專業(yè)知識(shí),以充分利用仿真的優(yōu)勢(shì)。

仿真和濾波器設(shè)計(jì)

濾波器無處不在 - 從超聲設(shè)備到心臟起搏器,只有特定頻率范圍通過才至關(guān)重要。然而,雖然過濾器是電子應(yīng)用中無處不在的構(gòu)建塊,但過濾器設(shè)計(jì)很少被理解并且經(jīng)常是痛苦的。是什么讓它如此復(fù)雜?通常,強(qiáng)度不是模擬電路設(shè)計(jì)的系統(tǒng)設(shè)計(jì)人員不能很好地理解特定性能所需的濾波器階數(shù)。

濾波器類型有很多變化(例如,Butterworth,Chebyshev和橢圓)針對(duì)各種規(guī)格進(jìn)行了優(yōu)化,例如單調(diào)紋波或過渡區(qū)域?qū)挾取V波器設(shè)計(jì)還涉及編寫復(fù)雜的數(shù)學(xué)方程式,以識(shí)別改變?yōu)V波器形狀的極點(diǎn)/零點(diǎn)位置(參見參考文獻(xiàn)3)。另一個(gè)問題是理論計(jì)算過程中假設(shè)的完美組分不存在;例如,電阻器的制造公差會(huì)影響預(yù)期的電路行為。

過濾器向?qū)У仍O(shè)計(jì)工具通過幫助設(shè)計(jì)人員了解不同拓?fù)浣Y(jié)構(gòu)之間的差異,以及建議在不同拓?fù)浣Y(jié)構(gòu)中使用的部件,大大簡化了這一復(fù)雜任務(wù)。設(shè)計(jì),無需復(fù)雜的數(shù)學(xué)。圖形環(huán)境允許設(shè)計(jì)人員觀察其電路如何在各種元件公差范圍內(nèi)工作。

驗(yàn)證巴特沃斯濾波器的設(shè)計(jì)

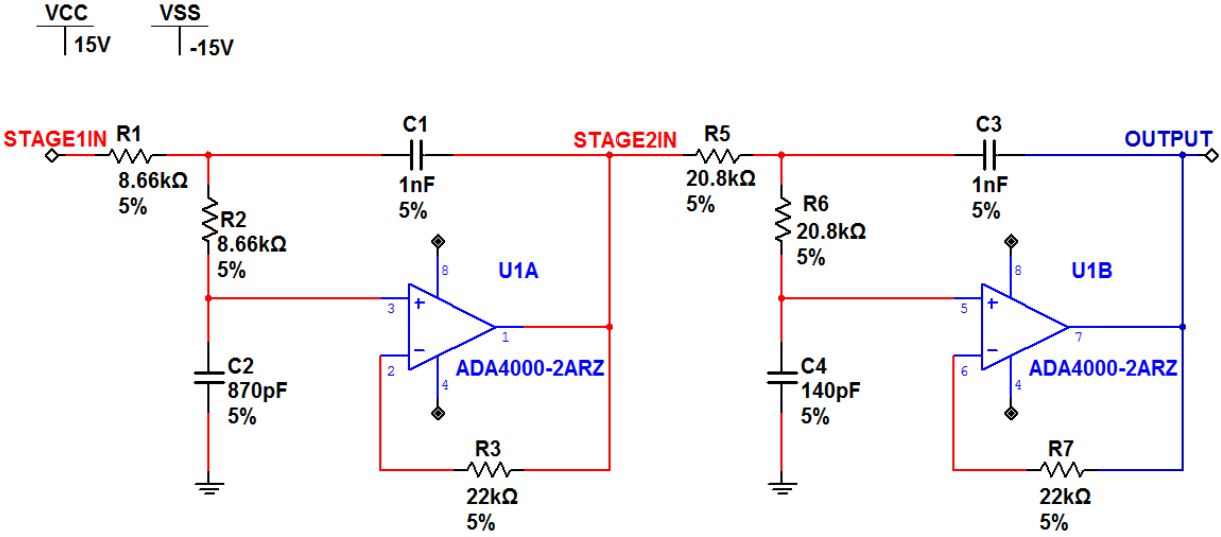

在我們的示例中,我們驗(yàn)證了有源電路的設(shè)計(jì)過濾。該濾波器采用ADI濾波器向?qū)гO(shè)計(jì),并采用ADA4000-2雙精度運(yùn)算放大器,該放大器因其快速壓擺率和容性負(fù)載穩(wěn)定性而被選中,因此非常適合濾波器設(shè)計(jì)。該運(yùn)算放大器的微微安培偏置電流允許使用高值電阻來構(gòu)建低頻濾波器,而無需擔(dān)心增加直流誤差。此外,R1的高值可最大限度地減少與信號(hào)源電阻的相互作用。通過級(jí)聯(lián)更多塊可以實(shí)現(xiàn)更高階濾波器;然而,對(duì)元件值的敏感性以及元件之間相互作用對(duì)頻率響應(yīng)的影響顯著增加,使得這些選擇的吸引力降低。信號(hào)相位通過濾波器保持(非反相配置)。

在NI Multisim中捕獲過濾器以進(jìn)行驗(yàn)證和進(jìn)一步分析(參見圖1)。這種低通,四階巴特沃茲濾波器設(shè)計(jì)具有20 kHz截止頻率和Sallen-Key實(shí)現(xiàn),因?yàn)樗子谠O(shè)計(jì),最大平坦的頻率響應(yīng)和最小的元件要求。巴特沃斯濾波器在通帶和阻帶中是單調(diào)的,并且具有最佳的通帶紋波和寬的過渡區(qū)域(即通帶和阻帶之間的區(qū)域)。它們經(jīng)常在數(shù)據(jù)采集系統(tǒng)中用作抗混疊濾波器。在EVAL-FLTR-SO-1RZ和EVAL-FLTR-LD-1RZ濾波器板上使用雙極版Sallen-Key濾波器拓?fù)浣Y(jié)構(gòu),可從ADI訂購。該電路板的應(yīng)用筆記為AN-0991。

設(shè)計(jì)濾波器時(shí),重要的是要考慮電路的頻率和時(shí)域響應(yīng)。讓我們研究如何使用NI Multisim驗(yàn)證這些特性。

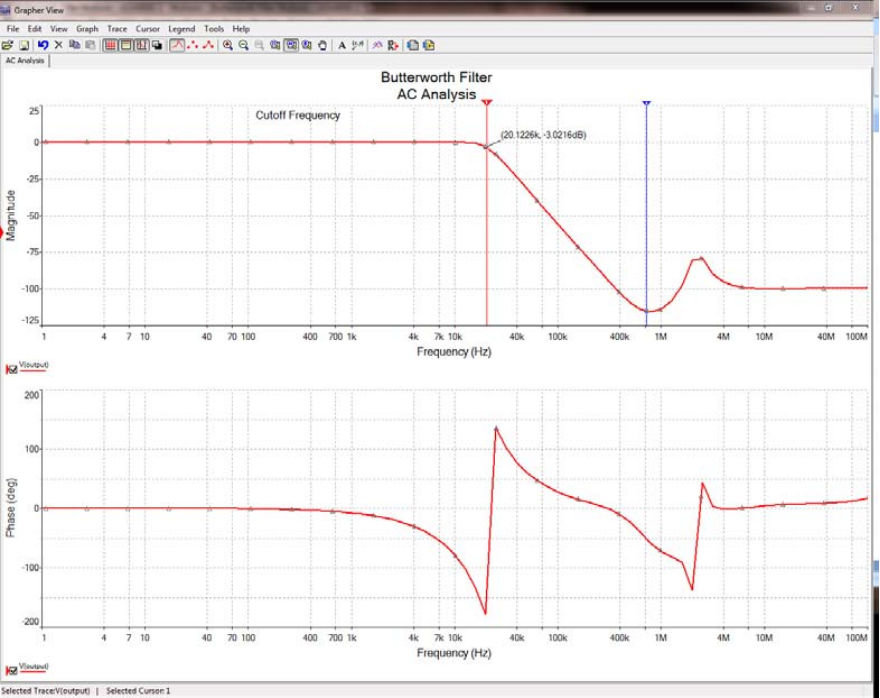

驗(yàn)證頻率響應(yīng)

圖2顯示了交流分析的結(jié)果。仿真結(jié)果表明截止頻率(增益下降3dB的頻率)為20.1 kHz,這非常接近我們?cè)O(shè)定的20 kHz規(guī)范。我們可以看到,在這個(gè)轉(zhuǎn)角頻率之外,增益下降到每十倍頻80 dB(濾波器傳遞函數(shù)中每個(gè)極點(diǎn)為-20dB / dec或-6dB / oct)。

我們還觀察到阻帶不會(huì)像我們對(duì)理想濾波器的預(yù)期那樣連續(xù)減小;由于運(yùn)算放大器電壓增益的損失,增益開始在大約1 MHz處增加。使用光標(biāo),我們估計(jì)該阻帶約為700 kHz。

驗(yàn)證時(shí)域響應(yīng)

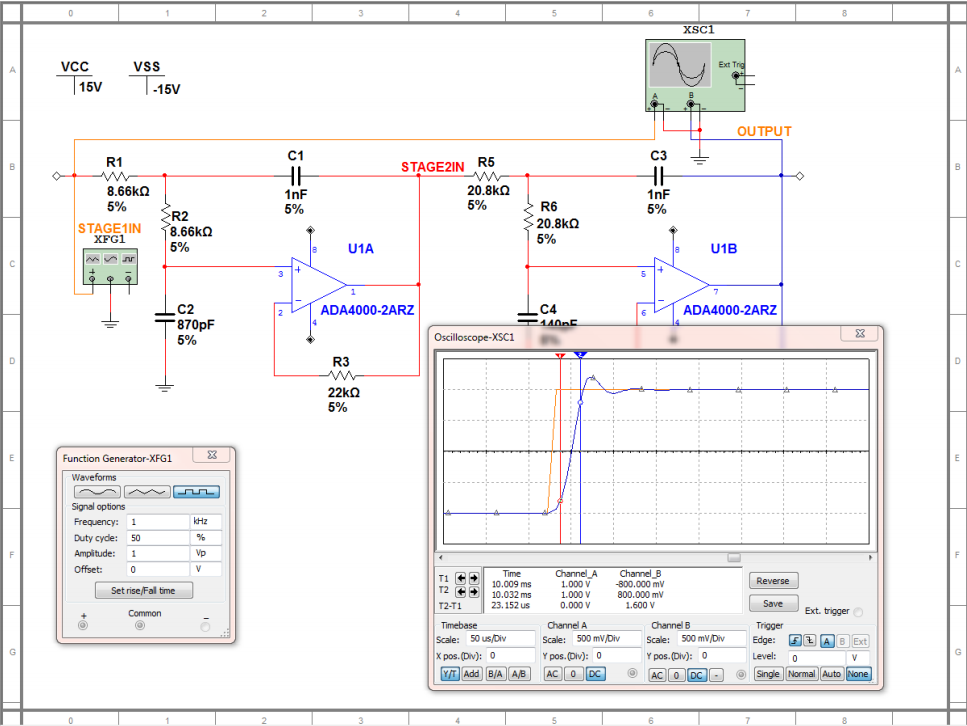

我們可以使用Multisim中提供的測(cè)量儀器來研究階躍響應(yīng)。函數(shù)發(fā)生器允許我們輸入激勵(lì),示波器允許我們直接在原理圖環(huán)境中觀察輸出波形。這些測(cè)量儀器模仿他們的臺(tái)式機(jī);例如,使用示波器,可以根據(jù)波形特征調(diào)整時(shí)基和分壓等參數(shù)。使用測(cè)量儀器,我們還可以實(shí)時(shí)更改設(shè)置,例如函數(shù)發(fā)生器設(shè)置的頻率,這樣我們就可以看到信號(hào)在超過20 kHz點(diǎn)的頻率下衰減了多少。

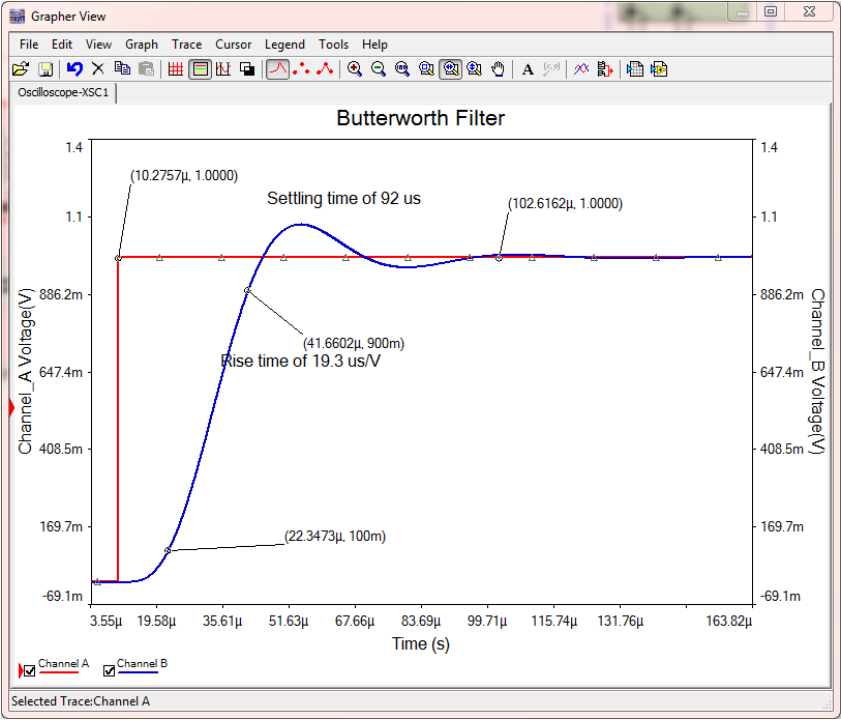

我們可以用示波器測(cè)量上升時(shí)間和建立時(shí)間等特性,如圖3所示;但是,我們也可以在Grapher中查看這些數(shù)據(jù),這個(gè)選項(xiàng)允許我們注釋和打印圖形以用于文檔目的。

我們研究的第一個(gè)特征是上升時(shí)間(定義為時(shí)間從最終產(chǎn)值的10%到90%);使用游標(biāo),我們確定這是19.3μs。我們還看到約92μs的建立時(shí)間。這些特性在圖4所示的圖表上進(jìn)行了注釋。(請(qǐng)注意,參數(shù)TMAX會(huì)影響上升時(shí)間,并且為了本示例的目的而從默認(rèn)值更改。)

考慮最壞的案例情景

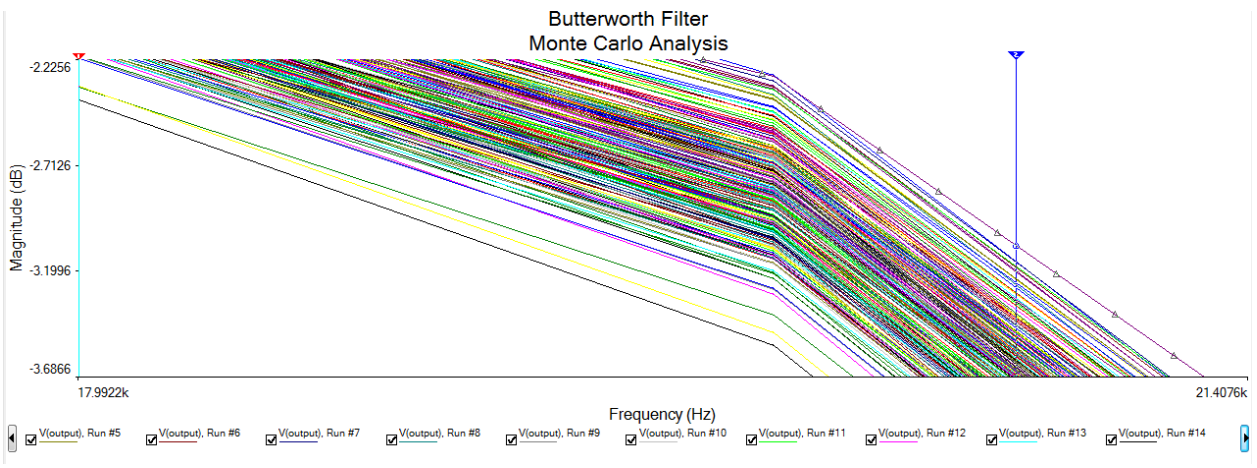

模擬的另一個(gè)核心好處是能夠計(jì)算非理想的組件值(即容差)。在本節(jié)中,我們執(zhí)行蒙特卡羅分析,該分析使用我們?cè)谠韴D中定義的5%元件公差范圍內(nèi)的元件值排列運(yùn)行多個(gè)交流分析;這使我們能夠看到在最壞的情況下我們的截止頻率如何受到影響。 (請(qǐng)注意,此分析也可用于瞬態(tài)或直流工作點(diǎn)分析。)

假設(shè)理想條件,第一次運(yùn)行是標(biāo)稱運(yùn)行。我們的分析輸出迭代了我們電路的200個(gè)排列,如圖5所示。觀察到第171次運(yùn)行(底部跟蹤)和第二次運(yùn)行(底部跟蹤)定義了截止頻率為20.67 kHz和19.02 kHz的最壞情況, 分別。截止頻率的這種偏差表明該濾波器設(shè)計(jì)對(duì)元件方差的靈敏度較低。

正如我們所看到的,一些測(cè)量需要比其他測(cè)量更多的后處理。例如,如果重復(fù)進(jìn)行,計(jì)算上升時(shí)間等任務(wù)可能會(huì)變得乏味。幸運(yùn)的是,有一些工具可以解決這個(gè)問題。 NI LabVIEW ?是一種圖形化編程語言,允許我們創(chuàng)建一個(gè)自定義界面,用于在Multisim中可視化和分析測(cè)量結(jié)果。該儀器可根據(jù)輸入和輸出波形自動(dòng)計(jì)算濾波器設(shè)計(jì)的上升時(shí)間,斜率,過沖和下沖。通過創(chuàng)建自定義儀器,設(shè)計(jì)人員可以自動(dòng)顯示傳統(tǒng)上需要手動(dòng)后處理的準(zhǔn)確的特征值。定制儀器可用于廣泛的應(yīng)用,包括將實(shí)際采集的測(cè)量值導(dǎo)入NI Multisim,其中包含噪聲等真實(shí)效果,以獲得更高的仿真精度。

結(jié)論

今天的系統(tǒng)設(shè)計(jì)師無法承受未經(jīng)驗(yàn)證的想法。借助現(xiàn)代設(shè)計(jì)工具,例如ADIFilter向?qū)В呀?jīng)構(gòu)建和驗(yàn)證的電路和NI Multisim,他們不需要工程師可以在原型設(shè)計(jì)階段之前驗(yàn)證和改善電路行為,大大提高設(shè)計(jì)效率。結(jié)果是重新設(shè)計(jì)成本更低,上市時(shí)間更短,設(shè)計(jì)性能更好。

-

半導(dǎo)體

+關(guān)注

關(guān)注

334文章

27026瀏覽量

216354 -

運(yùn)算放大器

+關(guān)注

關(guān)注

215文章

4898瀏覽量

172571 -

PCB設(shè)計(jì)

+關(guān)注

關(guān)注

394文章

4670瀏覽量

85294 -

SPICE

+關(guān)注

關(guān)注

6文章

181瀏覽量

42519 -

可制造性設(shè)計(jì)

+關(guān)注

關(guān)注

10文章

2065瀏覽量

15473 -

華秋DFM

+關(guān)注

關(guān)注

20文章

3493瀏覽量

4378

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

一文理解布隆過濾器和布谷鳥過濾器

CN過濾器原理

基于值域二次哈希方法的布魯姆過濾器

過濾器的作用

解密高效空氣過濾器的性能及要求

絲扣Y過濾器

絲扣Y過濾器及過濾器測(cè)試原理簡介

絲扣Y形過濾器

Y型過濾器

漢克森過濾器系列介紹

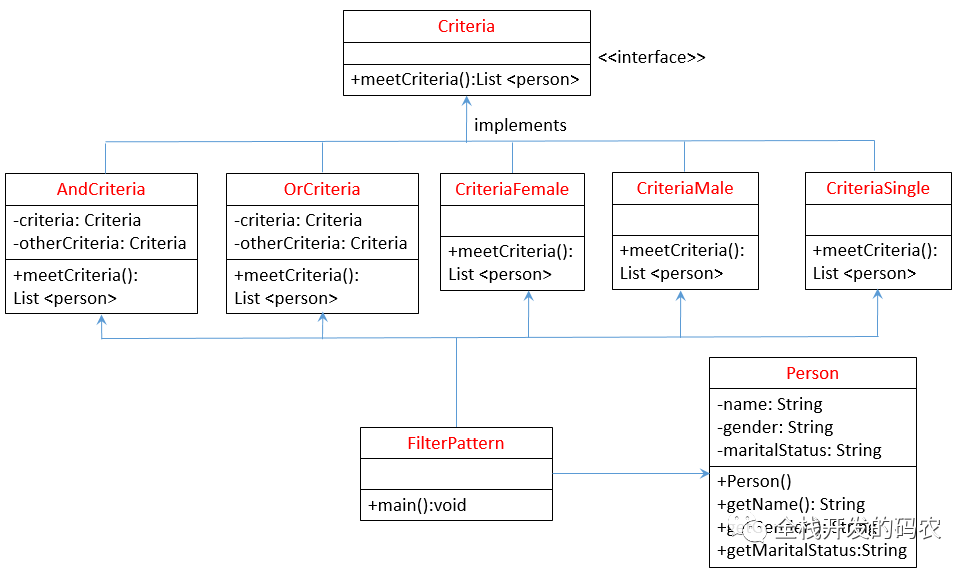

過濾器模式是指什么?

通過SPICE仿真軟件加速并改善過濾器設(shè)計(jì)

通過SPICE仿真軟件加速并改善過濾器設(shè)計(jì)

評(píng)論