比較器,是一個看起來簡單但又讓人極為痛苦的器件。如果你是剛學模擬電子技術的學生,那么在初次使用它時,不僅會被其詭異的表現難住,還將百思不得其解:如此簡單的比較器,怎么就這般不聽話呢?

《新概念模擬電路》系列叢書之《信號處理電路》一本書中這樣說:

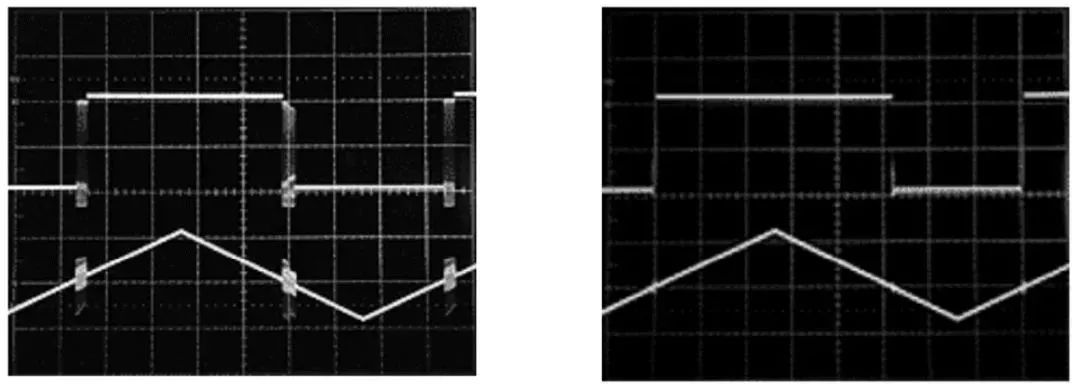

其實,比較器最常見的詭異現象就是翻轉抖動。以一個基準電壓為0V,輸入信號為從-1V到1V的三角波為例,當輸入信號穿越基準電壓點時,理論上:輸出信號應該立即翻轉,干脆利索,且輸入信號應該不受任何影響。但實際情況如圖1左圖所示:輸出信號在翻轉位置出現了多次抖動,然后才歸于平靜,然后,輸入信號居然也出現了抖動毛刺。

圖1 比較器的翻轉抖動及克服抖動帶來的效果

造成這種現象的原因很多,電源穩定性和地線穩定性不強是主要原因。其本質原理是,比較器的輸出端突然發生狀態變化時,會導致內部工作電流發生脈沖式突變,這個變化電流作用在電源電壓上,會導致電源電壓出現脈動;作用在地線上,會導致地線電位出現脈動。這種脈動帶來的直接后果就是,比較器的輸入狀態發生變化:原本輸入信號已經高于基準電壓,卻因為地線脈動的存在,出現瞬間的輸入信號低于基準電壓,比較器出現誤翻轉。這種誤翻轉持續作用,就會出現翻轉抖動。

翻轉抖動的存在,一定是輸入信號在處于基準電壓附近時發生。當輸入電壓持續增大,以至于地線抖動不足以改變比較器的輸入狀態時,那么輸出就歸于平靜了。

克服翻轉抖動的本質方法是加強電源和地線的穩定性——想盡一切辦法讓電源和地線接近理論要求:不管電源、地線上流過多大電流,其電壓都是恒定不變的。比如加粗電源線(地線)、縮短電源線(地線)長度,增加合適的電源旁路、去耦電容,使用高質量的地平面,或者將數字地和模擬地分開且實現單點對接。

克服翻轉抖動的另外一種方法,就是給比較器增加遲滯:用正反饋將原本開環的比較器,改變成遲滯比較器。圖1右圖,即為增加了遲滯后的波形,可見其翻轉抖動幾乎不存在了。

五大規則,破除“詭異現象”

相對來說,高速比較器更易出現各種各樣的詭異現象。因此,我們在設計之初就必須牢記以下五大規則,以最大程度地避免詭異現象。

01給比較器電路增加合適的旁路電容

在器件電源管腳的最近處,對地接一個或者兩個電容,以避免突變電流在漫長的電源線上——含有電阻和電感——產生的突變壓降。

02讓比較器電路使用地平面

由于地平面具有極大的面積,直接帶來的好處有兩點:第一,它具有極低的導通電阻,可以在通過大電流時保持地平面上任意兩點之間的電位差足夠小,以利于“地”與理論接近。第二,它還具有極低的電感,對高頻電流,也不會產生足夠大的壓降。

03用高速布線技術實施PCB設計

高速布線技術有別于低速,關鍵在于考慮了雜散參數。在低頻領域,電路板中的兩個隔離線,具有足夠大的電阻,但在高速領域,它們之間的雜散電容就會起作用。同時,長長的導線存在的電感,也會跳出來破壞正常的工作。因此,走線、位置、間距、方向、粗細、長短、過孔等,都將對高速電路產生不可忽視的影響。此事說來話長,要設計高速比較器電路,必須認真研讀相關資料。

04使用合適的探頭、示波器

如果要觀察比較器輸入輸出狀態,則一定要注意:探頭和示波器不是理想的,它們會影響電路的正常工作。

05注意降低信號源內阻

高速比較器接收的是高速信號,因此它非常懼怕低通濾波器。信號源電阻,也就是前級信號的輸出電阻,會與比較器輸入端電容組成低通濾波器。提高此低通濾波器上限截止頻率,是唯一的解決方案。而要如此,則有兩條路:第一,降低前級信號源的輸出電阻,第二,降低比較器輸入端的等效輸入電容。

一般來說,比較器入端等效電容主要由比較器芯片性能決定,也受線路與周邊“地”之間的雜散電容影響。當選擇了輸入端電容最小的比較器,又通過優秀的電路板設計,將雜散電容降至最小,此時應重點考慮降低前級信號源內阻。

-

比較器

+關注

關注

14文章

1636瀏覽量

107099 -

電壓

+關注

關注

45文章

5561瀏覽量

115586 -

去耦電容

+關注

關注

11文章

315瀏覽量

22310

原文標題:如何妙解“詭異的比較器”?

文章出處:【微信號:analog_devices,微信公眾號:analog_devices】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

為什么PCB看起來是黑色的?

SOLT原始數據看起來不對

救救孩子吧,這個電路看起來好奇怪啊

請問如何實現一個I2C從設備看起來像一個內存?

想讓你的iOS 10看起來與眾不同?可以試試越獄后這樣做

一個看起來簡單但又讓人極為痛苦的器件一一比較器

一個看起來簡單但又讓人極為痛苦的器件一一比較器

評論