上周臺積電發(fā)布了2018年報,全年營收342億美元,占到了全球晶圓代工市場份額的56%,可謂一家獨大。在先進工藝上,臺積電去年量產(chǎn)7nm工藝,進度領(lǐng)先友商一年以上,今年量產(chǎn)7nm EUV工藝,明年還有5nm EUV工藝,3nm工藝工廠也在建設中了。

作為全球最大的晶圓代工公司,臺積電在半導體制造上的技術(shù)沒啥可說的了,但很多人不知道的是臺積電近年來加大了半導體封裝技術(shù)的研發(fā),過去幾年能夠獨家代工蘋果A系列處理器也是跟他們的封裝技術(shù)進步有關(guān)。

日前在臺積電說法會上,聯(lián)席CEO魏哲家又透露了臺積電已經(jīng)完成了全球首個3D IC封裝,預計在2021年量產(chǎn),據(jù)悉該技術(shù)主要面向未來的5nm工藝,最可能首發(fā)3D封裝技術(shù)的還是其最大客戶蘋果公司。

在蘋果A系列處理器代工中,三星曾經(jīng)在A9處理器分到一杯羹,與臺積電分享了蘋果訂單,不過從A10處理器開始都是臺積電獨家代工了,而臺積電能夠贏得蘋果青睞也不只是因為半導體制造工藝,還跟臺積電能夠整合先進封裝工藝有關(guān)。

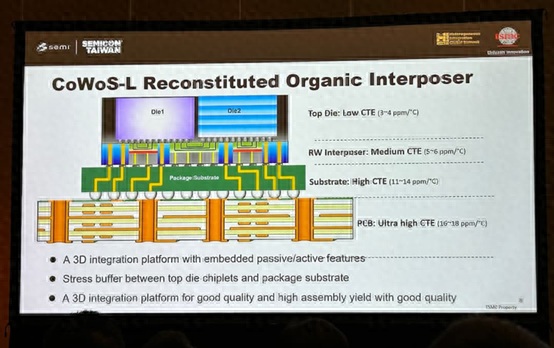

在半導體制造黃金定律摩爾定律逐漸失效的情況下,單純指望制造工藝來提高芯片集成度、降低成本不太容易了,所以先進封裝技術(shù)這幾年發(fā)展很快。此前臺積電推出了扇出型晶圓級封裝(InFO WLP)以及CoWoS封裝工藝,使得芯片有更好的電氣特性,能實現(xiàn)更高的內(nèi)存帶寬和低功耗運行能力,能使到移動設備有更好性能和更低功耗。

不過InFO WLP、CoWoS本質(zhì)上還是2.5D封裝,業(yè)界追求的一直是真3D封裝,去年臺積電宣布推出Wafer-on-Wafer(WoW) 封裝技術(shù),通過TSV硅穿孔技術(shù)實現(xiàn)了真正的3D封裝,而這個封裝技術(shù)主要用于未來的7nm及5nm換工藝。

雖然臺積電在上周的說法會上沒有明確提及他們首發(fā)的3D IC工藝是否為Wafer-on-Wafer(WoW)封裝技術(shù),但猜測起來就是這個新技術(shù)了,畢竟3D封裝是2019年的熱門新技術(shù),英特爾之前推出的Foreros封裝也是3D芯片封裝的一種。

根據(jù)臺積電的說法,他們的3D IC封裝技術(shù)已經(jīng)完成了技術(shù)開發(fā),不過2021年才會量產(chǎn),這個時候他們的主力工藝還是5nm EUV級別的。至于哪家客戶都成為第一個吃螃蟹的,預計蘋果還是最先采用臺積電3D封裝的公司,以往也是蘋果率先使用臺積電2.5D封裝的,他們有這個需求,也有這個資本。

-

處理器

+關(guān)注

關(guān)注

68文章

19170瀏覽量

229187 -

臺積電

+關(guān)注

關(guān)注

44文章

5610瀏覽量

166155 -

晶圓

+關(guān)注

關(guān)注

52文章

4850瀏覽量

127811

原文標題:臺積電:已完成全球首個3D IC封裝,預計2021年量產(chǎn)!

文章出處:【微信號:icsmart,微信公眾號:芯智訊】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

臺積電美國廠預計2025年初量產(chǎn)4nm制程

臺積電亞利桑那州新廠預計2025年初投產(chǎn)

臺積電2025年繼續(xù)漲價,5/3納米制程產(chǎn)品預計漲幅3~8%

臺積電德國晶圓廠即將動工,預計2027年底量產(chǎn)

臺積電SoIC封裝技術(shù)再獲蘋果青睞,2025年或迎量產(chǎn)新篇章

三星加強半導體封裝技術(shù)聯(lián)盟,以縮小與臺積電差距

臺積電延緩中科二期用地1.4nm廠建設,因2nm需求強勁,預計明年量產(chǎn)

蘋果自研AI服務器芯片,預計2025年臺積電3nm工藝

臺積電它有哪些前沿的2.5/3D IC封裝技術(shù)呢?

臺積電:已完成全球首個3D IC封裝,預計2021年量產(chǎn)

臺積電:已完成全球首個3D IC封裝,預計2021年量產(chǎn)

評論