尺寸縮小有其物理限制

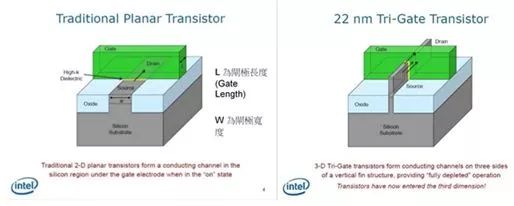

不過,制程并不能無限制的縮小,當我們將晶體管縮小到 20 奈米左右時,就會遇到量子物理中的問題,讓晶體管有漏電的現象,抵銷縮小 L 時獲得的效益。作為改善方式,就是導入 FinFET(Tri-Gate)這個概念,如右上圖。在 Intel 以前所做的解釋中,可以知道藉由導入這個技術,能減少因物理現象所導致的漏電現象。

更重要的是,藉由這個方法可以增加 Gate 端和下層的接觸面積。在傳統的做法中(左上圖),接觸面只有一個平面,但是采用 FinFET(Tri-Gate)這個技術后,接觸面將變成立體,可以輕易的增加接觸面積,這樣就可以在保持一樣的接觸面積下讓 Source-Drain 端變得更小,對縮小尺寸有相當大的幫助。

最后,則是為什么會有人說各大廠進入 10 奈米制程將面臨相當嚴峻的挑戰,主因是 1 顆原子的大小大約為 0.1 奈米,在 10 奈米的情況下,一條線只有不到 100 顆原子,在制作上相當困難,而且只要有一個原子的缺陷,像是在制作過程中有原子掉出或是有雜質,就會產生不知名的現象,影響產品的良率。

如果無法想象這個難度,可以做個小實驗。在桌上用 100 個小珠子排成一個 10×10 的正方形,并且剪裁一張紙蓋在珠子上,接著用小刷子把旁邊的的珠子刷掉,最后使他形成一個 10×5 的長方形。這樣就可以知道各大廠所面臨到的困境,以及達成這個目標究竟是多么艱巨。

隨著三星以及臺積電在近期將完成 14 奈米、16 奈米 FinFET 的量產,兩者都想爭奪 Apple 下一代的 iPhone 芯片代工,我們將看到相當精彩的商業競爭,同時也將獲得更加省電、輕薄的手機,要感謝摩爾定律所帶來的好處呢。

在前面已經介紹過芯片制造的過程就如同用樂高蓋房子一樣,先有晶圓作為地基,再層層往上迭的芯片制造流程后,就可產出必要的 IC 芯片。然而,沒有設計圖,擁有再強制造能力都沒有用,因此,建筑師的角色相當重要。但是 IC 設計中的建筑師究竟是誰呢?接下來要針對 IC 設計做介紹。

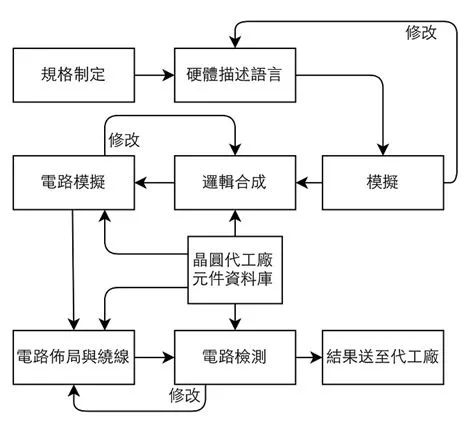

在 IC 生產流程中,IC 多由專業 IC 設計公司進行規劃、設計,像是聯發科、高通、Intel 等知名大廠,都自行設計各自的 IC 芯片,提供不同規格、效能的芯片給下游廠商選擇。因為 IC 是由各廠自行設計,所以 IC 設計十分仰賴工程師的技術,工程師的素質影響著一間企業的價值。然而,工程師們在設計一顆 IC 芯片時,究竟有那些步驟?設計流程可以簡單分成如下。

設計第一步,訂定目標

在 IC 設計中,最重要的步驟就是規格制定。這個步驟就像是在設計建筑前,先決定要幾間房間、浴室,有什么建筑法規需要遵守,在確定好所有的功能之后在進行設計,這樣才不用再花額外的時間進行后續修改。IC 設計也需要經過類似的步驟,才能確保設計出來的芯片不會有任何差錯。

規格制定的第一步便是確定 IC 的目的、效能為何,對大方向做設定。接著是察看有哪些協議要符合,像無線網卡的芯片就需要符合 IEEE 802.11 等規范,不然,這芯片將無法和市面上的產品兼容,使它無法和其他設備聯機。最后則是確立這顆 IC 的實作方法,將不同功能分配成不同的單元,并確立不同單元間鏈接的方法,如此便完成規格的制定。

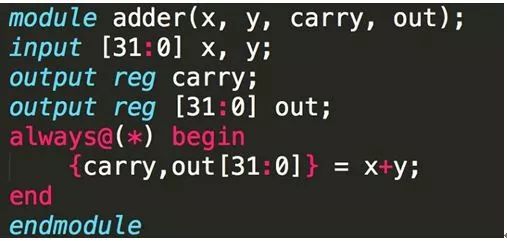

設計完規格后,接著就是設計芯片的細節了。這個步驟就像初步記下建筑的規畫,將整體輪廓描繪出來,方便后續制圖。在 IC 芯片中,便是使用硬件描述語言(HDL)將電路描寫出來。常使用的 HDL 有 Verilog、VHDL 等,藉由程序代碼便可輕易地將一顆 IC 地菜單達出來。接著就是檢查程序功能的正確性并持續修改,直到它滿足期望的功能為止。

▲ 32 bits 加法器的 Verilog 范例。

有了計算機,事情都變得容易

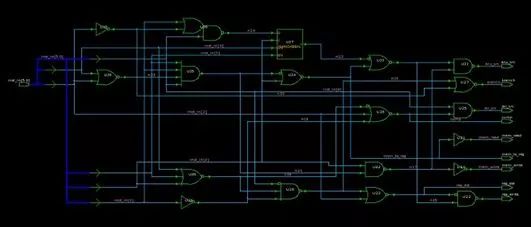

有了完整規畫后,接下來便是畫出平面的設計藍圖。在 IC 設計中,邏輯合成這個步驟便是將確定無誤的 HDL code,放入電子設計自動化工具(EDA tool),讓計算機將 HDL code 轉換成邏輯電路,產生如下的電路圖。之后,反復的確定此邏輯閘設計圖是否符合規格并修改,直到功能正確為止。

▲ 控制單元合成后的結果。

最后,將合成完的程序代碼再放入另一套 EDA tool,進行電路布局與繞線(Place And Route)。在經過不斷的檢測后,便會形成如下的電路圖。圖中可以看到藍、紅、綠、黃等不同顏色,每種不同的顏色就代表著一張光罩。至于光罩究竟要如何運用呢?

▲ 常用的演算芯片- FFT 芯片,完成電路布局與繞線的結果。

層層光罩,迭起一顆芯片

首先,目前已經知道一顆 IC 會產生多張的光罩,這些光罩有上下層的分別,每層有各自的任務。下圖為簡單的光罩例子,以集成電路中最基本的組件 CMOS 為范例,CMOS 全名為互補式金屬氧化物半導體(Complementary metal–oxide–semiconductor),也就是將 NMOS 和 PMOS 兩者做結合,形成 CMOS。至于什么是金屬氧化物半導體(MOS)?這種在芯片中廣泛使用的組件比較難說明,一般讀者也較難弄清,在這里就不多加細究。

下圖中,左邊就是經過電路布局與繞線后形成的電路圖,在前面已經知道每種顏色便代表一張光罩。右邊則是將每張光罩攤開的樣子。制作是,便由底層開始,依循上一篇 IC 芯片的制造中所提的方法,逐層制作,最后便會產生期望的芯片了。

至此,對于 IC 設計應該有初步的了解,整體看來就很清楚 IC 設計是一門非常復雜的專業,也多虧了計算機輔助軟件的成熟,讓 IC 設計得以加速。IC 設計廠十分依賴工程師的智能,這里所述的每個步驟都有其專門的知識,皆可獨立成多門專業的課程,像是撰寫硬件描述語言就不單純的只需要熟悉程序語言,還需要了解邏輯電路是如何運作、如何將所需的算法轉換成程序、合成軟件是如何將程序轉換成邏輯閘等問題。

然而,使用以上這些封裝法,會耗費掉相當大的體積。像現在的行動裝置、穿戴裝置等,需要相當多種組件,如果各個組件都獨立封裝,組合起來將耗費非常大的空間,因此目前有兩種方法,可滿足縮小體積的要求,分別為 SoC(System On Chip)以及 SiP(System In Packet)。

在智能型手機剛興起時,在各大財經雜志上皆可發現 SoC 這個名詞,然而 SoC 究竟是什么東西?簡單來說,就是將原本不同功能的 IC,整合在一顆芯片中。藉由這個方法,不單可以縮小體積,還可以縮小不同 IC 間的距離,提升芯片的計算速度。至于制作方法,便是在 IC 設計時間時,將各個不同的 IC 放在一起,再透過先前介紹的設計流程,制作成一張光罩。

然而,SoC 并非只有優點,要設計一顆 SoC 需要相當多的技術配合。IC 芯片各自封裝時,各有封裝外部保護,且 IC 與 IC 間的距離較遠,比較不會發生交互干擾的情形。但是,當將所有 IC 都包裝在一起時,就是噩夢的開始。IC 設計廠要從原先的單純設計 IC,變成了解并整合各個功能的 IC,增加工程師的工作量。此外,也會遇到很多的狀況,像是通訊芯片的高頻訊號可能會影響其他功能的 IC 等情形。

此外,SoC 還需要獲得其他廠商的 IP(intellectual property)授權,才能將別人設計好的組件放到 SoC 中。因為制作 SoC 需要獲得整顆 IC 的設計細節,才能做成完整的光罩,這同時也增加了 SoC 的設計成本。或許會有人質疑何不自己設計一顆就好了呢?因為設計各種 IC 需要大量和該 IC 相關的知識,只有像 Apple 這樣多金的企業,才有預算能從各知名企業挖角頂尖工程師,以設計一顆全新的 IC,透過合作授權還是比自行研發劃算多了。

折衷方案,SiP 現身

作為替代方案,SiP 躍上整合芯片的舞臺。和 SoC 不同,它是購買各家的 IC,在最后一次封裝這些 IC,如此便少了 IP 授權這一步,大幅減少設計成本。此外,因為它們是各自獨立的 IC,彼此的干擾程度大幅下降。

▲ Apple Watch 采用 SiP 技術將整個計算機架構封裝成一顆芯片,不單滿足期望的效能還縮小體積,讓手表有更多的空間放電池。

采用 SiP 技術的產品,最著名的非 Apple Watch 莫屬。因為 Watch 的內部空間太小,它無法采用傳統的技術,SoC 的設計成本又太高,SiP 成了首要之選。藉由 SiP 技術,不單可縮小體積,還可拉近各個 IC 間的距離,成為可行的折衷方案。下圖便是 Apple Watch 芯片的結構圖,可以看到相當多的 IC 包含在其中。

▲ Apple Watch 中采用 SiP 封裝的 S1 芯片內部配置圖。

完成封裝后,便要進入測試的階段,在這個階段便要確認封裝完的 IC 是否有正常的運作,正確無誤之后便可出貨給組裝廠,做成我們所見的電子產品。至此,半導體產業便完成了整個生產的任務。

-

芯片

+關注

關注

453文章

50402瀏覽量

421800 -

半導體

+關注

關注

334文章

27014瀏覽量

216289 -

SiP

+關注

關注

5文章

498瀏覽量

105259

原文標題:精華 | 半導體工程師必看!半導體整個生產流程揭秘

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

smd 貼片LED生產流程

PCB生產流程有哪些

半導體整個生產流程大揭秘

半導體整個生產流程大揭秘

評論