要想造個芯片, 首先, 你得畫出來一個長這樣的玩意兒給Foundry (外包的晶圓制造公司)

在 IC 設計中,邏輯合成這個步驟便是將確定無誤的 HDL code,放入電子設計自動化工具(EDA tool),讓電腦將 HDL code 轉換成邏輯電路,產生如下的電路圖。之后,反覆的確定此邏輯閘設計圖是否符合規格并修改,直到功能正確為止。

控制單元合成后的結果

最后,將合成完的程式碼再放入另一套 EDA tool,進行電路布局與繞線(Place And Route)。在經過不斷的檢測后,便會形成如下的電路圖。圖中可以看到藍、紅、綠、黃等不同顏色,每種不同的顏色就代表著一張光罩。

完成電路布局與繞線的結果

然后Foundry是怎么做的呢?大體上分為以下幾步:

首先搞到一塊圓圓的硅晶圓, (就是一大塊晶體硅, 打磨的很光滑, 一般是圓的)

此處重新排版, 圖片按照生產步驟排列. 但是步驟總結單獨寫出.

1. 濕洗(用各種試劑保持硅晶圓表面沒有雜質)

2. 光刻(用紫外線透過蒙版照射硅晶圓, 被照到的地方就會容易被洗掉, 沒被照到的地方就保持原樣. 于是就可以在硅晶圓上面刻出想要的圖案. 注意, 此時還沒有加入雜質, 依然是一個硅晶圓. )

3. 離子注入(在硅晶圓不同的位置加入不同的雜質, 不同雜質根據濃度/位置的不同就組成了場效應管.)

4.1干蝕刻(之前用光刻出來的形狀有許多其實不是我們需要的,而是為了離子注入而蝕刻的. 現在就要用等離子體把他們洗掉, 或者是一些第一步光刻先不需要刻出來的結構, 這一步進行蝕刻).

4.2濕蝕刻(進一步洗掉, 但是用的是試劑, 所以叫濕蝕刻).

--- 以上步驟完成后, 場效應管就已經被做出來啦~ 但是以上步驟一般都不止做一次, 很可能需要反反復復的做, 以達到要求. ---

5 等離子沖洗(用較弱的等離子束轟擊整個芯片)

6 熱處理,其中又分為:

6.1 快速熱退火(就是瞬間把整個片子通過大功率燈啥的照到1200攝氏度以上, 然后慢慢地冷卻下來, 為了使得注入的離子能更好的被啟動以及熱氧化)6.2 退火6.3 熱氧化(制造出二氧化硅, 也即場效應管的柵極(gate) )

7 化學氣相淀積(CVD), 進一步精細處理表面的各種物質

8 物理氣相淀積(PVD), 類似, 而且可以給敏感部件加coating

9 分子束外延 (MBE)如果需要長單晶的話就需要這個..

10 電鍍處理

11 化學/機械 表面處理

然后芯片就差不多了,接下來還要:12 晶圓測試13 晶圓打磨

就可以出廠封裝了.

我們來一步步看:

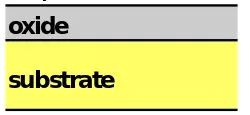

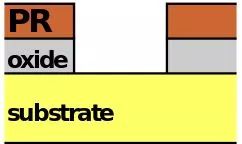

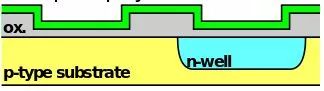

1上面是氧化層, 下面是襯底(硅) -- 濕洗

2 一般來說, 先對整個襯底注入少量(10^10 ~ 10^13 / cm^3) 的P型物質(最外層少一個電子), 作為襯底 -- 離子注入

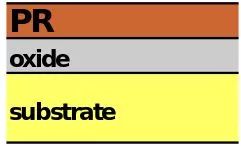

3先加入Photo-resist, 保護住不想被蝕刻的地方 -- 光刻

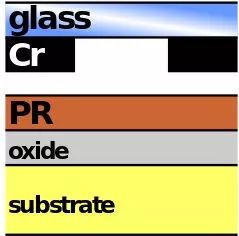

4.上掩膜!(就是那個標注Cr的地方.中間空的表示沒有遮蓋,黑的表示遮住了.)-- 光刻

5 紫外線照上去... 下面被照得那一塊就被反應了-- 光刻

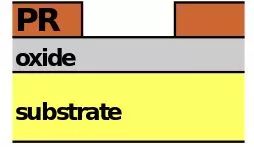

6.撤去掩膜.-- 光刻

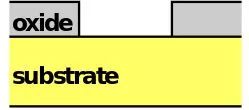

7 把暴露出來的氧化層洗掉, 露出硅層(就可以注入離子了)-- 光刻

8 把保護層撤去. 這樣就得到了一個準備注入的硅片. 這一步會反復在硅片上進行(幾十次甚至上百次). -- 光刻

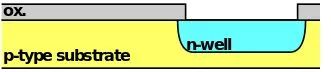

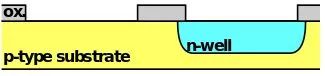

9 然后光刻完畢后, 往里面狠狠地插入一塊少量(10^14 ~ 10^16 /cm^3) 注入的N型物質就做成了一個N-well (N-井) -- 離子注入

10 用干蝕刻把需要P-well的地方也蝕刻出來. 也可以再次使用光刻刻出來. -- 干蝕刻

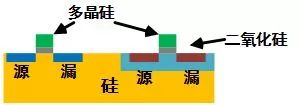

11 上圖將P-型半導體上部再次氧化出一層薄薄的二氧化硅. -- 熱處理

12 用分子束外延處理長出的一層多晶硅, 該層可導電 -- 分子束外延

13 進一步的蝕刻, 做出精細的結構. (在退火以及部分CVD) -- 重復3-8光刻 + 濕蝕刻

14 再次狠狠地插入大量(10^18 ~ 10^20 / cm^3) 注入的P/N型物質, 此時注意MOSFET已經基本成型. -- 離子注入

15 用氣相積淀 形成的氮化物層 -- 化學氣相積淀

16 將氮化物蝕刻出溝道 -- 光刻 + 濕蝕刻

17 物理氣相積淀長出 金屬層 -- 物理氣相積淀

18 將多余金屬層蝕刻. 光刻 + 濕蝕刻

最開始那個芯片, 大小大約是1.5mm x 0.8mm

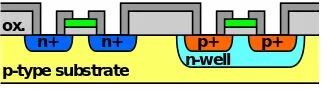

比如說我們要做一個100nm的門電路(90nmtechnology),那么實際上是這樣的:

這層掩膜是第一層, 大概是10倍左右的Die Size

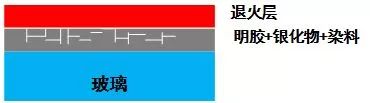

有兩種方法制作:EmulsionMask和MetalMask

EmulsionMask:

這貨分辨率可以達到 2000line / mm (其實挺差勁的... 所以sub-micron ,也即um級別以下的 VLSI不用... )

制作方法:首先:需要在Rubylith(不會翻譯...)上面刻出一個比想要的掩膜大個20倍的形狀(大概是真正制作尺寸的200倍),這個形狀就可以用激光什么的刻出來,只需要微米級別的刻度.

然后:

給!它!照!相!,相片就是EmulsionMask!

如果要拍的"照片"太大, 也有分區域照的方法.

MetalMask:

制作過程:1.先做一個EmulsionMask,然后用EmulsionMask以及我之前提到的17-18步做MetalMask!瞬間有種Recursion的感覺有木有!!!

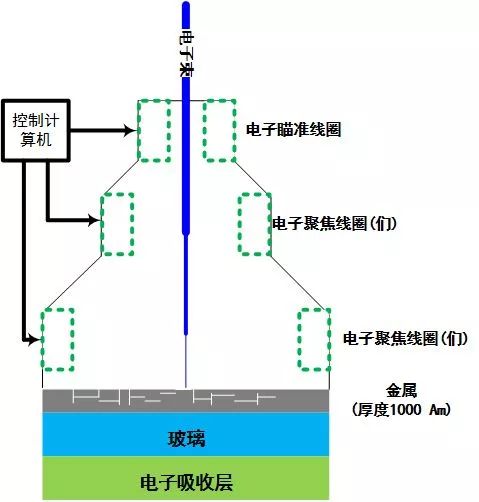

2.Electronbeam:

大概長這樣

制作的時候移動的是底下那層. 電子束不移動.就像打印機一樣把底下打一遍.

好處是精度特別高, 目前大多數高精度的(<100nm技術)都用這個掩膜. 壞處是太慢...

做好掩膜后:Feature Size = k*lamda / NA

k一般是0.4, 跟制作過程有關; lamda是所用光的波長; NA是從芯片看上去, 放大鏡的倍率.

以目前的技術水平, 這個公式已經變了, 因為隨著Feature Size減小, 透鏡的厚度也是一個問題了

Feature Size = k * lamda / NA^2

恩.. 所以其實掩膜可以做的比芯片大一些. 至于具體制作方法, 一般是用高精度計算機探針 + 激光直接刻板. Photomask(掩膜) 的材料選擇一般也比硅晶片更加靈活, 可以采用很容易被激光汽化的材料進行制作.

今天突然發現我還忘了一個很重要的點!找了一圈知乎找到了!多謝

@又見山人

!!

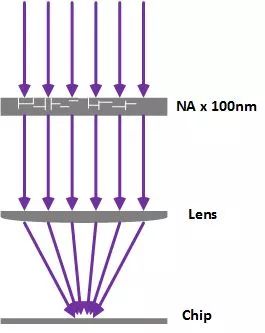

浸沒式光刻

這個光刻的方法絕壁是個黑科技一般的點!直接把Lamda縮小了一個量級,Withnoextracost!你們說吼不吼啊!

FoodforThought:Wikipedia上面關于掩膜的版面給出了這樣一幅圖,假設用這樣的掩膜最后做出來會是什么形狀呢?

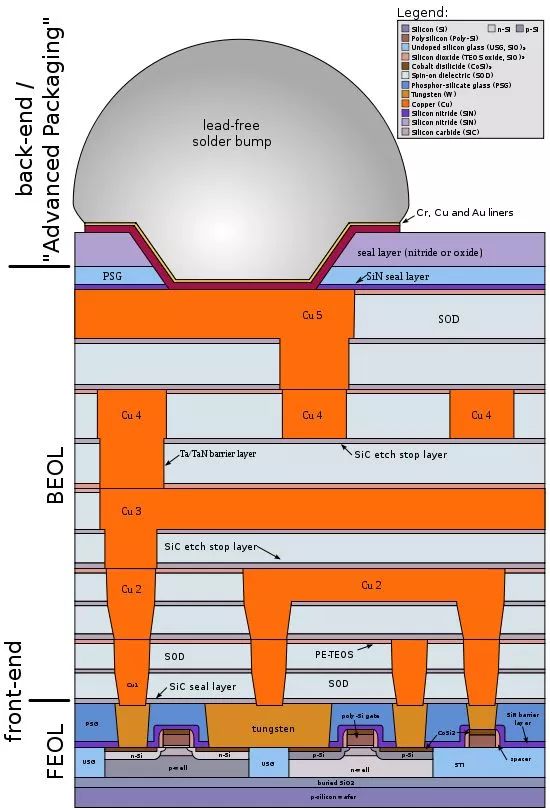

最終成型大概長這樣:

其中, 步驟1-15 屬于 前端處理 (FEOL), 也即如何做出場效應管

步驟16-18(加上許許多多的重復)屬于后端處理(BEOL),后端處理主要是用來布線.最開始那個大芯片里面能看到的基本都是布線!一般一個高度集中的芯片上幾乎看不見底層的硅片,都會被布線遮擋住.

SOI(Silicon-on-Insulator)技術:

傳統CMOS技術的缺陷在于:襯底的厚度會影響片上的寄生電容,間接導致芯片的性能下降.SOI技術主要是將源極/漏極和硅片襯底分開,以達到(部分)消除寄生電容的目的.

傳統:

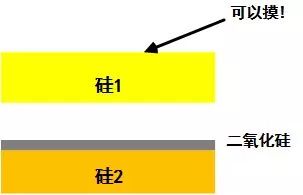

SOI:

制作方法主要有以下幾種(主要在于制作硅-二氧化硅-硅的結構, 之后的步驟跟傳統工藝基本一致.)

1.高溫氧化退火:

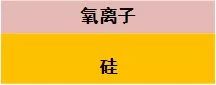

在硅表面離子注入一層氧離子層

等氧離子滲入硅層, 形成富氧層

高溫退火

成型.

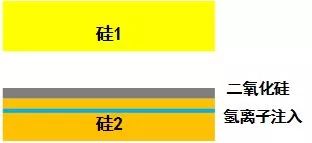

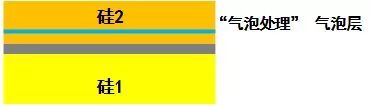

或者是2.WaferBonding(用兩塊!)

不是要做夾心餅干一樣的結構嗎?爺不差錢!來兩塊!

來兩塊!

對硅2進行表面氧化

對硅2進行氫離子注入

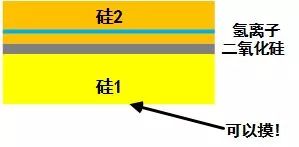

翻面

將氫離子層處理成氣泡層

切割掉多余部分

成型!+再利用

光刻

離子注入

微觀圖長這樣:

再次光刻+蝕刻

撤去保護, 中間那個就是Fin

門部位的多晶硅/高K介質生長

門部位的氧化層生長

長成這樣

源極 漏極制作(光刻+ 離子注入)

初層金屬/多晶硅貼片

蝕刻+成型

物理氣相積淀長出表面金屬層(因為是三維結構, 所有連線要在上部連出)

機械打磨(對!不打磨會導致金屬層厚度不一致)

成型!

連線

處理器的制造過程可以大致分為沙子原料(石英)、硅錠、晶圓、光刻(平版印刷)、蝕刻、離子注入、金屬沉積、金屬層、互連、晶圓測試與切割、核心封裝、等級測試、包裝上市等諸多步驟,而且每一步里邊又包含更多細致的過程。

下邊就圖文結合,一步一步看看:

沙子:硅是地殼內第二豐富的元素,而脫氧后的沙子(尤其是石英)最多包含25%的硅元素,以二氧化硅(SiO2)的形式存在,這也是半導體制造產業的基礎。

硅熔煉:12英寸/300毫米晶圓級,下同。通過多步凈化得到可用于半導體制造質量的硅,學名電子級硅(EGS),平均每一百萬個硅原子中最多只有一個雜質原子。此圖展示了是如何通過硅凈化熔煉得到大晶體的,最后得到的就是硅錠(Ingot)。

單晶硅錠:整體基本呈圓柱形,重約100千克,硅純度99.9999%。

第一階段的合影。

硅錠切割:橫向切割成圓形的單個硅片,也就是我們常說的晶圓(Wafer)。順便說,這下知道為什么晶圓都是圓形的了吧?

晶圓:切割出的晶圓經過拋光后變得幾乎完美無瑕,表面甚至可以當鏡子。事實上,Intel自己并不生產這種晶圓,而是從第三方半導體企業那里直接購買成品,然后利用自己的生產線進一步加工,比如現在主流的45nm HKMG(高K金屬柵極)。值得一提的是,Intel公司創立之初使用的晶圓尺寸只有2英寸/50毫米。

第二階段合影。

光刻膠(Photo Resist):圖中藍色部分就是在晶圓旋轉過程中澆上去的光刻膠液體,類似制作傳統膠片的那種。晶圓旋轉可以讓光刻膠鋪的非常薄、非常平。

光刻:光刻膠層隨后透過掩模(Mask)被曝光在紫外線(UV)之下,變得可溶,期間發生的化學反應類似按下機械相機快門那一刻膠片的變化。掩模上印著預先設計好的電路圖案,紫外線透過它照在光刻膠層上,就會形成微處理器的每一層電路圖案。一般來說,在晶圓上得到的電路圖案是掩模上圖案的四分之一。

光刻:由此進入50-200納米尺寸的晶體管級別。一塊晶圓上可以切割出數百個處理器,不過從這里開始把視野縮小到其中一個上,展示如何制作晶體管等部件。晶體管相當于開關,控制著電流的方向。現在的晶體管已經如此之小,一個針頭上就能放下大約3000萬個。

第三階段合影。

溶解光刻膠:光刻過程中曝光在紫外線下的光刻膠被溶解掉,清除后留下的圖案和掩模上的一致。

蝕刻:使用化學物質溶解掉暴露出來的晶圓部分,而剩下的光刻膠保護著不應該蝕刻的部分。

清除光刻膠:蝕刻完成后,光刻膠的使命宣告完成,全部清除后就可以看到設計好的電路圖案。

第四階段合影。

光刻膠:再次澆上光刻膠(藍色部分),然后光刻,并洗掉曝光的部分,剩下的光刻膠還是用來保護不會離子注入的那部分材料。

離子注入(Ion Implantation):在真空系統中,用經過加速的、要摻雜的原子的離子照射(注入)固體材料,從而在被注入的區域形成特殊的注入層,并改變這些區域的硅的導電性。經過電場加速后,注入的離子流的速度可以超過30萬千米每小時。

清除光刻膠:離子注入完成后,光刻膠也被清除,而注入區域(綠色部分)也已摻雜,注入了不同的原子。注意這時候的綠色和之前已經有所不同。

第五階段合影。

晶體管就緒:至此,晶體管已經基本完成。在絕緣材(品紅色)上蝕刻出三個孔洞,并填充銅,以便和其它晶體管互連。

電鍍:在晶圓上電鍍一層硫酸銅,將銅離子沉淀到晶體管上。銅離子會從正極(陽極)走向負極(陰極)。

銅層:電鍍完成后,銅離子沉積在晶圓表面,形成一個薄薄的銅層。

第六階段合影。

拋光:將多余的銅拋光掉,也就是磨光晶圓表面。

金屬層:晶體管級別,六個晶體管的組合,大約500納米。在不同晶體管之間形成復合互連金屬層,具體布局取決于相應處理器所需要的不同功能性。芯片表面看起來異常平滑,但事實上可能包含20多層復雜的電路,放大之后可以看到極其復雜的電路網絡,形如未來派的多層高速公路系統。

第七階段合影。

晶圓測試:內核級別,大約10毫米/0.5英寸。圖中是晶圓的局部,正在接受第一次功能性測試,使用參考電路圖案和每一塊芯片進行對比。

晶圓切片(Slicing):晶圓級別,300毫米/12英寸。將晶圓切割成塊,每一塊就是一個處理器的內核(Die)。

丟棄瑕疵內核:晶圓級別。測試過程中發現的有瑕疵的內核被拋棄,留下完好的準備進入下一步。

第八階段合影。

單個內核:內核級別。從晶圓上切割下來的單個內核,這里展示的是Core i7的核心。

封裝:封裝級別,20毫米/1英寸。襯底(基片)、內核、散熱片堆疊在一起,就形成了我們看到的處理器的樣子。襯底(綠色)相當于一個底座,并為處理器內核提供電氣與機械界面,便于與PC系統的其它部分交互。散熱片(銀色)就是負責內核散熱的了。

處理器:至此就得到完整的處理器了(這里是一顆Core i7)。這種在世界上最干凈的房間里制造出來的最復雜的產品實際上是經過數百個步驟得來的,這里只是展示了其中的一些關鍵步驟。

第九階段合影。

等級測試:最后一次測試,可以鑒別出每一顆處理器的關鍵特性,比如最高頻率、功耗、發熱量等,并決定處理器的等級,比如適合做成最高端的Core i7-975 Extreme,還是低端型號Core i7-920。

裝箱:根據等級測試結果將同樣級別的處理器放在一起裝運。

零售包裝:制造、測試完畢的處理器要么批量交付給OEM廠商,要么放在包裝盒里進入零售市場。

-

芯片

+關注

關注

454文章

50430瀏覽量

421862 -

晶圓

+關注

關注

52文章

4846瀏覽量

127804 -

晶體管

+關注

關注

77文章

9635瀏覽量

137856

原文標題:【科普】芯片里面有幾千萬的晶體管是怎么實現的?

文章出處:【微信號:TechSugar,微信公眾號:TechSugar】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

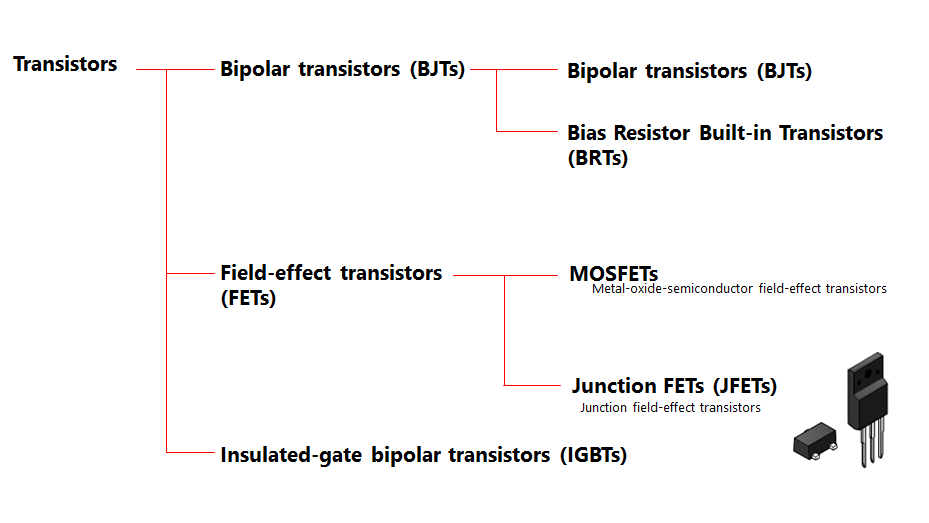

晶體管的基本工作模式

NMOS晶體管和PMOS晶體管的區別

CMOS晶體管和MOSFET晶體管的區別

芯片晶體管的深度和寬度有關系嗎

芯片中的晶體管是怎么工作的

晶體管電流的關系有哪些類型 晶體管的類型

PNP晶體管符號和結構 晶體管測試儀電路圖

蘋果M3芯片的晶體管數量

M3芯片有多少晶體管

什么是達林頓晶體管?達林頓晶體管的基本電路

芯片里面有幾千萬的晶體管是怎么實現的

芯片里面有幾千萬的晶體管是怎么實現的

評論