本文的作者為大名鼎鼎的高速數字信號完整性專家Eric Bogatin,他是Signal Integrity Journal的技術編輯和Teledyne LeCroy信號完整性學院的院長,他還是美國科羅拉多大學博爾德分校ECEE部門的兼職教授 。

下面是翻譯自“Signal Integrity Journal“的一篇文章。

如果用面包板/杜邦線連接就能夠讓你的電路正常工作,那么用電路板來實現就不用考慮太多,只需要做到盡可能低的成本、方便生產和測試即可。但如果性能很重要,用面包板的簡單互連無法滿足要求,或者你想養成良好的設計習慣,即便設計2層板,你也需要記住如下7個設計規則。

多數的2層電路板很難達到非常高的性能。一般來講,僅用2層電路板是很難對BGA封裝的器件(例如FPGA或高端微處理器)進行布線的。所以我們不談高端主板,但很多的消費類產品,比如微控制器和物聯網應用都是采用2層板構建的。

Ericr認為,即便市場上廣被使用,歷史悠久的2層板 -Arduino Uno板(見下面的圖1)在本文強調的7個好習慣方面都做的不夠,存在著很大的改進空間。

我們試圖避免的兩個問題:

PCB設計中的原理圖只是標識了設計中使用的元器件以及它們之間的連接方式,并沒有說明設計的信號或電源完整性性能,也就是說原理圖中沒有考慮實際的連線導致的一系列非理想的問題。

一旦在PCB上通過走線、過孔等對電信號建立了連接,實際達到的產品性能只會偏離理想值,會產生惡化,有可能會出現許多信號和電源完整性方面的問題,但兩個最常見且影響最大的問題就是:

由信號和返回路徑環路之間的互感(地彈)導致的交調/串擾(Crosstalk)

圖2為Arduino Uno板上測得的由于多個數字輸出同時“開”/“關”導致的接地反彈。

電路板的物理設計(包括布局、布線)目標就是遵循一些設計規則來盡可能減少這兩個問題。你前期做的分析越多,風險也就會越低,你的設計第一次成功的概率也就越高。如果不做詳細的分析(建議每個硬件工程師都養成詳盡分析的習慣),我們只能遵循一些通用的設計規則,以降低這些問題給產品帶來的風險。

我們可以養成如下7種好習慣,這些習慣雖然不能保證成功,但一定會降低失敗的風險。

習慣1:使用6mil寬的信號走線、20mil寬的電源走線和13mil的過孔直徑

你要以最低的成本去打板(尤其是快板),這就是國內PCB板廠要求的最小設計規則,在設計中按照上面的參數設定布線規則,可以在任何一家工廠生產你的電路板了,低于這些參數就會有風險,高于這些參數可能會導致布線困難。

工程師總喜歡用盡可能細的走線來設計較高密度的電路并且不增加成本。你也許認為6mil的走線太細了,但它可以承載1A的直流電流而不會導致明顯的溫升。在1盎司的銅中每英寸的電阻為80毫歐姆,大多數應用中,即便1歐姆的串聯電阻(相當于12英寸的走線長度)是不會影響到系統的性能的,因此對于低于1GHz的信號,可以不用考慮這方面的損耗。

使用標準62mil厚的雙層板的6mil線寬,其特征阻抗約為150歐姆。如果上升時間足夠短或連線長度足夠長必須需要端接,只要走線還在板子上,對于150歐姆走線的端接和50歐姆走線的端接是一樣容易的,并且功耗還會更小。

1盎司銅線中的20mil寬的走線可以承載3A的直流電流且不會導致明顯的溫升。其串聯電阻約為25毫歐/英寸, 4英寸長的電源走線僅具有0.1歐姆的串聯電阻,完全可以忽略。如果需要承載超過3A的電源走線,可以將線寬增加到100mil,能夠支持到10A的DC電流。

在Eric的一個實驗中,測試了在電路板上炸掉PCB上的走線所需的電流量,使用了如圖3所示的電路板。

習慣2:元器件、重要的信號線、電源走線放在頂層(Top layer),地回路放在底層(Bottom layer)。

這樣調試的時候比較容易跟蹤信號路徑,一目了然,可以通過線寬來判斷哪些是信號線、哪些是電源線。如果信號走線下面有連續的返回路徑,即便返回路徑比較長,也不會影響到板子的性能。最簡單的方法是在電路板的底層使用堅固的“地平面”。

習慣3:元器件要合理布局以便信號走線不要擁擠,且信號走線間盡可能分開。

在元器件已經布局的情況下,信號走線要盡可能分開以減少線間串擾。走線具有相當高的特征阻抗,由于它們遠離返回平面,它們之間會有一些串擾,臨近的信號距離越近,串擾越嚴重。在保持最近間距的情況下,近端串擾可高達25%。將走線盡可能分開能減少近端串擾。

習慣4:當您需要在底層(Bottom layer)鋪設“交叉下方”時,要盡可能短;如果不能縮短,就要在上面添加一條帶子。

為獲得最佳的性能,需要為每條信號線提供一個低阻抗的返回路徑,以降低相鄰信號返回路徑對之間的互感。如果需要在地平面中走信號線,那就必須在其周圍設置隔離間隙。在該間隙上方布線的信號走線將在返回路徑中出現間隙并且與跨越間隙的其它信號產生串擾。

最小化這個問題的方法就是要讓這個間隙盡可能短,這樣返回電流只需要繞行很短的路徑。當這個間隙不得不比較長時,就需要添加一個跳過頂層間隙的返回路徑。圖4顯示了2個“交叉下方”的間隙示例,其中返回帶在頂層布線。

習慣5:將去耦電容盡可能靠近IC的電源引腳,并盡可能降低環路電感

在最小的空間中使用最大尺寸的電容器,其耐壓至少是供電電壓的2倍。比較常用的是22uF的MLCC電容。電容的大小取決于去耦的元件的電流消耗。經驗值 -22uF能夠應付22mA的瞬態電流,這時電壓降很低。

電容的容量不是太重要,而更重要的是IC的電源和接地引腳與去耦電容之間的環路電感要盡可能的低,這通常意味著電容器要盡可能靠近IC引腳,并在電源和gnd路徑上使用短而寬的走線。一個例子如圖5所示。

習慣6:在所有的連接器上,要盡可能為每個數字信號分配一個返回回路。

導致地彈或開關噪聲的一個因素是多個信號線共享相同的返回引腳。在許多連接器中,可能多個信號線進行開關切換的時候只有1或2個返回引腳,這樣極容易導致地彈。Arduino板子的插頭引腳就存在這個問題 - 只有1個接地引腳,而卻有13個數字I/O進行開關切換。

習慣7:不要盲從兩個流行的設計規則:

不要對每個電源引腳都使用三個不同值(10uF、1uF、0.1 uf)的組合。因為這樣做不解決任何問題,相反,如果不仔細可能會帶來其它問題。如果空間允許,可以全部使用22uF的電容,并在布線的時候保證低回路電感。

切勿使用銅填充。它沒有解決問題,有時會產生其他問題。電源線不要使用銅填充, 而是用走線來做。這樣你可以跟蹤電源路徑以驗證連接和調試。從IC到去耦電容,保持低回路電感非常重要。即便10A的直流電流,也只需要100mil寬的走線。

如果是“地平面”填充,可以使用底層(bottom layer)用作地平面并仔細處理返回路徑。在頂層(top layer)不要用銅填充來接地。這樣很容易導致返回路徑不連續而且不易察覺。

不要認為添加了連接到地的銅填充就會減少串擾。如果已經有連續的、不重疊的返回路徑,即便是沒有任何填充,串擾也會很低。如果你能夠在信號走線之間有空間進行銅填充,則說明走線之間的間距已經足夠大到串擾可以小到忽略不計。除非你能正確處理填充,否則它通常會增加串擾,而不是減少它。

總結:

遵循這些設計要領并不能保證產品的成功,它們將會降低由于串擾或電源上的噪聲導致產品發生故障的風險。

作者Eric讓自己的學生嘗試著對Arduino Uno板子的設計根據上述的規則做進一步的改進,下圖就是改進后的PCB板圖:

你會注意到這個新的設計包含了上述的所有的7個要點:

信號寬6mil,電源走線的線寬為20mil,信號過孔為13mil;

紅色的第1層是元器件、信號和電源線。藍色的底層為堅實的地平面;

信號走線盡可能地分開;

在交叉下方布置在地平面中的情況下,間隙保持較短,當它們較長時,使用了返回帶;

去耦電容靠近電源引腳,具有低電感的電源和地的環路;

在插頭引腳中,額外的一排接地連接被添加到數字引腳的外部。使用Arduino插頭引腳的標準尺寸,但增加了外排引腳;

任何層上都沒有使用銅填充,只用了一個值的去耦電容。

除了降低信號和電源完整性問題風險的最佳設計實踐外,該板還增加了4個其它重要的提升設計的動作:

多個LED指示燈能夠顯示每路電源的供電狀態和一些數字功能;

添加了用以隔離的跳線,可以隔離某些電路的電源,方便調試;

針對一些重要的信號添加了測試點及相應的回路,方便使用具有彈簧尖端或同軸尖端的10x探針;

更直觀的絲印信息,方便板子的安裝、測試。

在設計中養成這些好的設計習慣,有助于降低設計風險、增加板子一次就能成功的概率。

-

電路板

+關注

關注

140文章

4908瀏覽量

97443 -

微處理器

+關注

關注

11文章

2247瀏覽量

82326 -

信號完整性

+關注

關注

68文章

1398瀏覽量

95388

原文標題:2層板設計需要養成的7個好習慣

文章出處:【微信號:xiaojiaoyafpga,微信公眾號:電子森林】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

PCB疊層規則你都懂了嗎?

pcb布線規則(2)

PCB制板的22個規則經驗分享

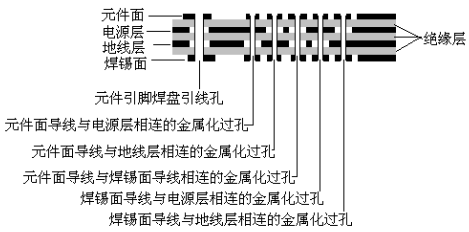

射頻設計:PCB疊層、電源退耦、過孔規則

PCB板的布局需要遵循什么規則

BTS7960大功率直流電機驅動板ALTIUM設計硬件原理圖+PCB文件 2層板設計 大小為66 7

設計2層板,你需要記住如下7個設計規則

設計2層板,你需要記住如下7個設計規則

評論