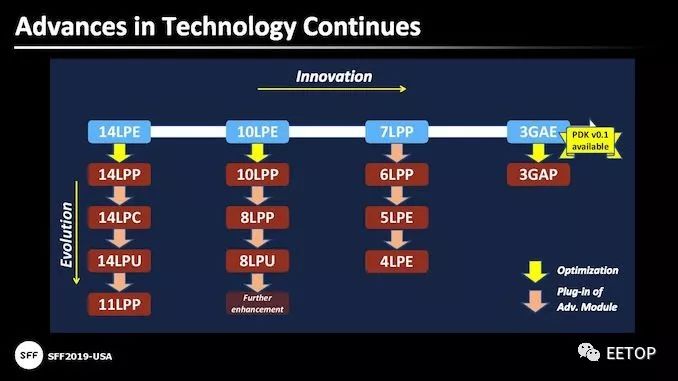

5月14日,在三星的代工論壇活動中,三星發布了其第一款3nm工藝的產品設計套件(PDK) alpha 0.1版本,旨在幫助客戶盡早開始設計工作,提高設計競爭力,同時縮短周轉時間(TAT)。這一宣布的特別之處在于,3nm是三星打算推出下一代環繞柵極Gate-All-Around(GAA)技術以取代FinFET的工藝節點。這個被稱為當前FinFET 技術進化版的生產技術,能夠對芯片核心的晶體管進行重新設計和改造,使其更小更快。

而根據國際商業戰略咨詢公司(International Business Strategies) 執行長Handel Jones 表示,目前三星正透過強大的材料研究讓晶圓制造技術獲得發展。而在GAA 的技術發展上,三星大約領先臺積電1 年的時間,而英特爾封面則是落后三星2 到3 年。

與7nm技術相比,三星的3GAE工藝可將芯片面積減少45%,功耗降低50%或性能提高35%。基于GAA的工藝節點有望在下一代應用中廣泛采用,例如移動,網絡,汽車,人工智能(AI)和物聯網。

三星計劃通過其3納米工藝的專有MBCFET?(多橋通道FET)技術為其無晶圓廠客戶提供獨特的優勢。MBCFET?是一種先進的薄而長的線型GAA結構,可堆疊薄而長的納米片,如紙張,以提高性能和功率效率,以及與pinpet工藝的兼容性。它具有利用技術的優勢。

平面FET,FinFET,GAAFET,MBCFET?晶體管結構

超越FinFET:GAA

在過去十年中,基于邏輯的工藝技術創新的主要驅動力是FinFET。與標準平面晶體管相比,FinFET在工藝節點減小時允許更好的性能和電壓縮放,從而最大限度地減少了晶體管限制的負面影響。FinFET通過在垂直方向上縮放來增加晶體管的溝道和柵極之間的接觸面積,與平面設計相比允許更快的切換時間和更高的電流密度。

然而,就像平面晶體管一樣,FinFET晶體管最終會達到一個極限點,隨著工藝節點的收縮,它們無法伸縮。為了擴大規模,通道和柵極之間的接觸面積需要增加,實現這一點的方法是采用Gate-All-Around(GAA)的設計。GAA調整晶體管的尺寸,以確保柵極不僅在頂部和兩側,也在通道下方。這使得GAA設計可以垂直堆疊晶體管,而不是橫向堆疊。

基于GAA的FET(GAAFET)可以具有多種形狀因子。大多數研究都指向基于納米線的GAAFET,具有較小的通道寬度并使通道盡可能小。這些類型的GAAFET通常可用于低功耗設計,但難以制造。另一種實現方式是使通道像水平板一樣,增加通道的體積,從而提供性能和擴展的好處。這種基于納米片的GAAFET是三星所謂的多橋通道FET或MBCFET,它將成為該公司的商標名稱。

在平面晶體管縮放到22nm/ 16nm左右的情況下,當我們從22nm/ 14nm下降到5nm和4nm時,FinFET是理想的。三星計劃在其3nm設計上推出基于納米片的GAAFET,完全取代FinFET。

3nm PDK

當半導體公司在給定工藝上設計新芯片時,他們需要的工具之一是來自代工廠的設計套件(PDK)。例如,對于在14nm芯片上創建Arm芯片的人來說,他們會調用Arm并要求為三星、臺積電或GlobalFoundries提供的Cortex-A55設計套件,該套件已針對該流程進行了優化。對于14nm,這些設計套件非常成熟,根據您是否需要高頻率或低功耗優化,Arm可能會提供不同的版本。

然而,對于一個新的工藝技術時,PDK會經歷alpha和beta版本。PDK包含流程的設計規則,以及用于實現功耗和性能最佳的優化。

三星在今天推出其第一代3nm alpha版PDK,用于采用MBCFET的第一代3nm工藝。三星將此流程稱為“3GAE”流程,這個alpha版本將允許其合作伙伴開始掌握其3GAE流程的一些新設計規則。

三星在其首個3GAE流程中做出了許多承諾。其中一個標題是將工作電壓從0.75伏降低到0.70伏。與7nm相比,三星的3GAE工藝旨在將芯片面積減少45%,功耗降低50%或性能提高35%。

三星表示,這些性能數據基于對頻率很重要的關鍵路徑使用較大寬度的單元,而對于非關鍵路徑使用較小寬度單元,其中節能是至關重要的。

從中可以看出其中的一些:三星預計其3GAE流程將在2020年首次提供客戶流片,2020年末風險生產,2021年末批量生產。

除了3GAE之外,三星已經預測其第二代3nm工藝將被稱為3GAP,重點是高性能操作。3GAE將于2021年投入風險生產,大規模生產可能在2022年。

PDK工具和EDA合作伙伴

PDK工具包括SPICE,DRC,LVS,PEX,P-Cell,Fill Deck和P&RTechfile。EDA合作伙伴包括Cadence,Mentor和Synopsys。

-

三星電子

+關注

關注

34文章

15856瀏覽量

180924 -

臺積電

+關注

關注

44文章

5609瀏覽量

166120

原文標題:3nm!三星GAA工藝超越FinFET,領先臺積電

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

3nm!三星 GAA工藝超越 FinFET,領先臺積電

3nm!三星 GAA工藝超越 FinFET,領先臺積電

評論