4月登場的「超大型積體電路國際研討會」(VLSI-TSA/DAT)是全球半導體產業年度盛事,首場專題演講邀請到美國IBM華生研究中心研究員沙希迪(Ghavam Shahidi)以「功耗改善減緩,摩爾定律是否已走到盡頭?」為題,談半導體最新制程面臨功率改善放緩的問題,并提出建議的解決之道。

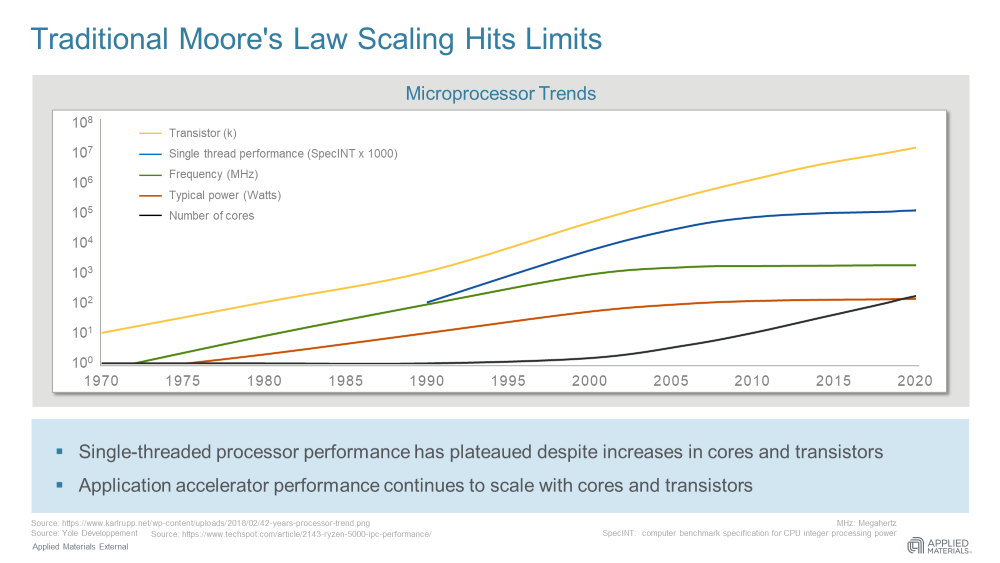

1965年提出的摩爾定律(Moore's Law)引領半導體發展超過半世紀,是指芯片上可容納的電晶體數目,約每隔18個月便會增加一倍,性能也將提升一倍,但近年的互補式金屬氧化物半導體(CMOS)先進制程中,最新幾代納米節點的功耗改善程度,已出現明顯的放緩,這不禁讓人憂心,摩爾定律是否即將走到盡頭?

制程推進唯功耗降低才能提高效能

半導體的主流制程CMOS,多年來每推進到一個新的納米節點,最大的兩個效益就是:面積可縮小30%、功耗明顯改善。以后者來看,在特定頻率下,芯片功耗的降低(每次操作的耗能)是一項重要指標,因為惟有芯片的整體耗能改善,才有機會提升芯片性能,例如:可在芯片的下一代設計中,內建更多核心或新增更多功能。

綜觀半導體納米節點的歷史數據,早期每一代的納米制程進化,其功耗與上一代相較,改善的幅度都很大。以Sony游戲主機Playsation 2所采用的250納米芯片為例,整體芯片的耗能為23瓦,演進了3個世代后,來到90納米節點,功耗僅須0.5瓦,等于每一個納米世代較前一代平均節能72%以上。

14納米制程節能幅度大不如前

然而,在近年幾個制程中,節能幅度大不如前。以英特爾的Core i7做為測試標的,第一代Core i7采45納米制程,第二代Core i7采32納米制程,兩代之間僅實現了32%到50%的能耗下降。

接下來Core i7在2012年進入了22納米制程,能耗只比32納米下降了20%至27%。2014年,英特爾又陸續發表采用14納米的Broadwell及Skylake(分別是第五、第六代的Core i7),結果它與前一代的22納米相較,功耗僅下降0%至25% ,節能幅度創下最低紀錄。直到2017年推出采14++納米制程的Core i7芯片,節能幅度才增至20%到33%。

觀察Core i7從45納米到14納米的節能數據可以看出,雖然每一代制程,芯片的面積愈縮愈小,但能夠達到的能耗縮減幅度卻愈來愈小,尤其在14納米初期最為明顯。近2年進入更先進的10納米制程,也有類似狀況,例如英特爾在2018年5月推出第一個采用10納米制程的Core i3,其功耗表現跟14納米制程類似:亦即并未看到功耗大幅降低。

挑戰極限可考慮不同半導體架構

這個是否代表摩爾定律已逼近極限?如果芯片在每個新世代的制程無法達到明顯的功耗下降,確實會導致芯片效能出現瓶頸,因為芯片能否置入更多核心,能否新增更多功能,都與能耗息息相關。

展望未來,若要改善功耗,關鍵之一在于必須將半導體元件的電容降低。我認為,不論是業界目前初邁入的7納米,甚或是未來更先進的納米制程,也要準備好3種不同架構的選項來改善功耗:一是繼續采行鰭式場效電晶體(FinFET)架構,設法將FET的閘極高度降低。

FinFET架構雖蔚為主流,卻因閘極底部不導電及閘極過高,造成寄生電容產生,若能解決此一問題,應可見到功耗的改善。二是轉向納米線(Nano-wires)或垂直式FET(Vertical FET)等3D架構,以降低寄生電容和電阻;三是將平面式(Planar)架構納入考量,例如SOI(絕緣層上硅晶體)的原理是在硅晶體之間,加入絕緣體物質,可使寄生電容減少。

我想大家都很期待,在未來幾個更先進的納米制程,能回復到早期納米節點功耗大幅降低的景況,這對下世代高效能微處理器來說尤其重要。

-

英特爾

+關注

關注

60文章

9880瀏覽量

171501 -

半導體

+關注

關注

334文章

27007瀏覽量

216276

原文標題:挑戰摩爾定律極限,可考慮不同半導體架構

文章出處:【微信號:iawbs2016,微信公眾號:寬禁帶半導體技術創新聯盟】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

擊碎摩爾定律!英偉達和AMD將一年一款新品,均提及HBM和先進封裝

國產半導體新希望:Chiplet技術助力“彎道超車”!

“自我實現的預言”摩爾定律,如何繼續引領創新

半導體發展的四個時代

半導體發展的四個時代

AI在半導體設計和制造中的作用

摩爾定律的終結:芯片產業的下一個勝者法則是什么?

挑戰摩爾定律極限 可考慮不同半導體架構

挑戰摩爾定律極限 可考慮不同半導體架構

評論