粉絲:“請問高速先生,繞線的設計要注意哪些地方”,高速先生:“至少要保證繞線的間距達到3H”,然后再補上一句,“H是信號到參考層的距離哈”。這時候粉絲一般都會“哦……謝謝哈”,我們隨即以一個尷尬而不失禮貌的微笑進行回應。

其實我們也知道,一個簡單的回答會讓粉絲們變得越發的不淡定,雖然這個答案本身是比較準確的,僅僅是這個回答會有一點口說無憑的感覺。

什么?你們還不知道我們到底在說什么東西?其實繞線的設計基本上存在于每一塊PCB板的并行信號上。最常見的就是我們的DDR設計,一組需要等長的信號由于收發pin的位置不一樣,必然會存在繞線的情況。然后從空間的角度來衡量的話,繞線的間隔越小那么所占的空間就越小,尤其是在DDR顆粒間的繞線更是如此,在里面寸土寸金的地方,作為一個工程師肯定希望更小間距的繞線咯。

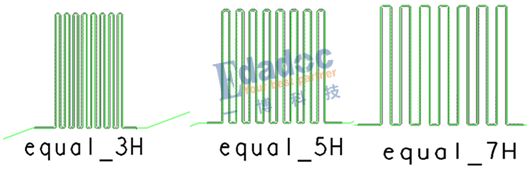

好吧好吧,解釋完我們到底在說什么之后,我們還是繼續說回口說無憑這個事哈。粉絲們希望得到一些數據的支撐,為此我們也專門做了一板測試板去驗證它。很簡單,沒有對比就沒有傷害,我們做的測試板要對比的設計如下所示,分別做了繞線間距為3H,5H和7H三種設計,當然還有不繞線的一根參考線啦,總長度為10inch。

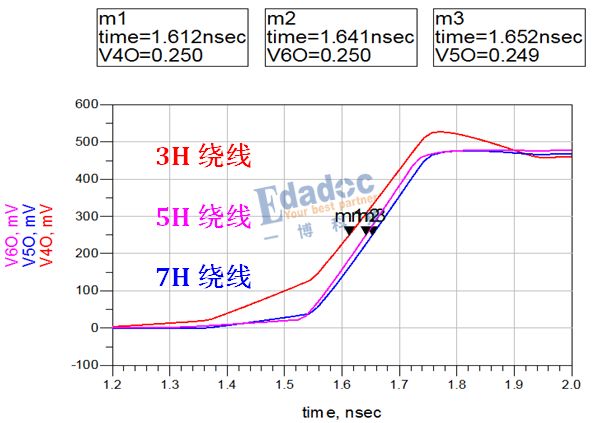

那么測試的數據是怎么樣的呢?首先說到繞線嘛,大家肯定會關心繞線完的時延啦,結果這三種情況的測試結果的對比是這樣的。可以看到,繞線繞得越密的話,信號的延時會變小,3H大概會比5H的繞線快30ps,而5H之后就影響比較小了,5H只比7H快10ps左右了。

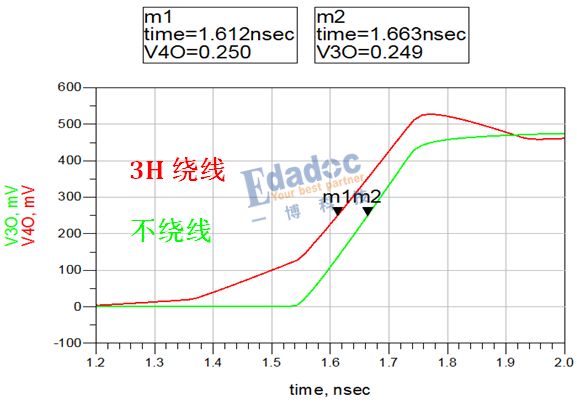

我們老是說3H是一個基本原則,我們可以和不繞線的延時來比一下,結果如下所示。

它們的延時差了大概50ps。考慮到這個是10inch的繞線情況,那么簡單粗暴的換算成單元長度時,其實每英寸的差別只有5ps左右,已經是非常小的影響了。

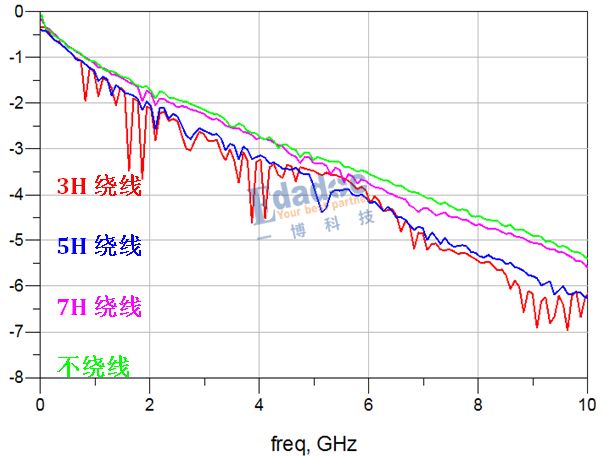

當然如果從損耗這個角度來看的話,又會看到一些和信號頻率很相關的影響了。可以看到3H在2GHz以上就會有很明顯的諧振點,要是信號速率在4Gbps(2GHz基頻)時就會嚴重影響信號質量,5H,7H就會明顯有很好的改善。

雖然從損耗來看3H比較恐怖,但是……我們都忽略了一點,哪怕你真的需要走10inch的繞線,你也不會把一個跑幾個Gbps的走線用單端線來走吧。這里順便說一下哈,同樣的繞線,用差分的形式會有非常非常明顯的改善哈,大家不要太擔心。我們單線的繞線設計目前主要就是應用于DDR這樣的并行系統,目前最高的速率也只不過在1.5GHz(3Gbps)左右哈。

-

pcb

+關注

關注

4318文章

23022瀏覽量

396434 -

繞線

+關注

關注

5文章

47瀏覽量

9725

原文標題:繞線的影響?SI來告訴你

文章出處:【微信號:yes-easy-high-speed,微信公眾號:高速先生】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

【LabVIEW我來告訴你】 Webbrowser調用的隱患

【labview我來告訴你】labview編程可以很簡單

【labview我來告訴你】對像高亮顯示”實現酷閃耀功能

【labview我來告訴你】簡單實現嵌套的if。。。else

【labview我來告訴你】用好控件的小技巧

【labview我來告訴你】XControl的妙用

labview心得體會之我來告訴你匯總(持續更新)

全自動繞線機與手工繞線有什么不同呢

谷景告訴你環形繞線電感阻值是不是越大越好

谷景告訴你共模繞線電感封裝尺寸千萬別選錯

一文告訴你繞線電感線圈在使用中為什么會有噪音

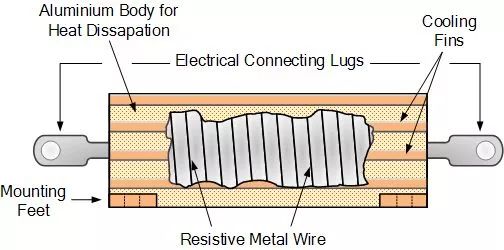

繞線電阻的工作原理是什么

繞線的影響 SI來告訴你

繞線的影響 SI來告訴你

評論