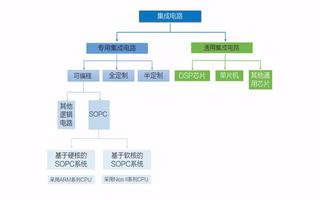

軟核演練篇包含了哪些內容:該篇以什么是軟核、什么是Qsys、如何構建一個Qsys系統為切入點,在該基礎上進一步介紹了Nios II處理器的體系結構、Qsys豐富多彩的內置IP,以及Avalon總線接口規范,然后又以Avalon總線接口規范為基礎,進一步定制了開發板所有外設的IP核。最后,又以系統uC/OS-II和uCGUI為例進行了應用開發的介紹。本篇不同于傳統的傻瓜式教程,將理論和實踐相結合,不僅僅講述了怎樣做,更進一步講述了為什么要這樣做。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

處理器

+關注

關注

68文章

19165瀏覽量

229128 -

IP

+關注

關注

5文章

1655瀏覽量

149332 -

總線

+關注

關注

10文章

2867瀏覽量

87988

發布評論請先 登錄

相關推薦

基于NIOS II的SOPC中存儲器型外設接口的設計

的系統直接與片外設備相連接,例如存儲器芯片或一個外部處理器。Avalon三態從端口允許Avalon SwitchFabric與PCB板上共享的地址和數據

發表于 12-07 10:27

ARM體系結構、處理器和設備開發文章

ARM產品必須如何運行的體系結構規范。

此外,一些合作伙伴還授權實施符合架構規范的自己的ARM處理器。

這導致了分層劃分為三個級別的規范,這

發表于 08-21 07:28

基于Avalon總線的PWM外設實現NiosⅡ嵌入式處理器的設計

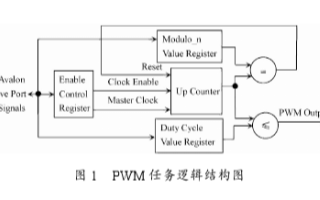

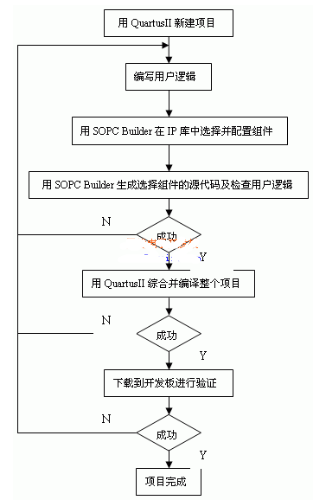

SoPCBuilder環境下加載使用,方便了用戶開發一個自定制的片上系統。本文通過在NiosⅡ嵌入式系統內部集成了基于Avalon總線的脈沖寬度調制(PWM)從外設,介紹了自定制Avalon

基于Nios II實現AVALON總線與USB控制器的接口設計

隨著電路規模越來越大,片上系統(SoC)已經成為IC設計的發展趨勢,相應地也有了更加靈活的片上可編程系統(SOPC)。Nios II CPU是一個基于流水線設計的通用RISC微處理器,擁有五級流水線

發表于 04-11 17:01

?1532次閱讀

微處理器體系結構

《微處理器體系結構》適合作為高等院校集成電路設計相關專業工程碩士的教材,并可以作為微處理器硬件與軟件設計相關專業高年級本科生和研究生的教材。

《微處理器

發表于 04-14 10:29

?0次下載

NiOSⅡ處理器的Avalon總線架構資料下載

電子發燒友網為你提供NiOSⅡ處理器的Avalon總線架構資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可

發表于 04-27 08:54

?9次下載

嵌入式微處理器體系結構 嵌入式微處理器原理與應用

嵌入式微處理器是一種集成于嵌入式系統中的微處理器,其體系結構和應用具有獨特特點。本文將詳細介紹嵌入式微處理器的體系結構以及其原理與應用。 一

Nios II處理器的體系結構及Avalon總線接口規范

Nios II處理器的體系結構及Avalon總線接口規范

評論